(54) ЗАДАТЧИК ИНТЕНСИВНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-задающее устройство | 1980 |

|

SU894731A1 |

| Устройство для моделированияиМпульСНОгО дАТчиКА чАСТОТы ВРАщЕНия | 1979 |

|

SU849245A1 |

| Система автоматического управления шахтной подъемной машиной с асинхронным электроприводом | 1979 |

|

SU893778A1 |

| СПОСОБ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ПАРАМЕТРАМИ ЭЛЕКТРОМЕХАНИЧЕСКОЙ СИСТЕМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2414048C1 |

| Интегрозадающее устройство | 1983 |

|

SU1115067A1 |

| Устройство для управления двигателем переменного тока | 1983 |

|

SU1104635A1 |

| Устройство задания режима движения шахтной подъемной установки | 1988 |

|

SU1645236A2 |

| Инвертирующий интегратор | 1988 |

|

SU1741259A1 |

| СПОСОБ ФОРМИРОВАНИЯ ИНТЕГРАЛЬНОГО СИГНАЛА УПРАВЛЕНИЯ ДЛЯ СИСТЕМ АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2403608C1 |

| ЭЛЕКТРОННОЕ РЕЛЕ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ И С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 2008 |

|

RU2360358C1 |

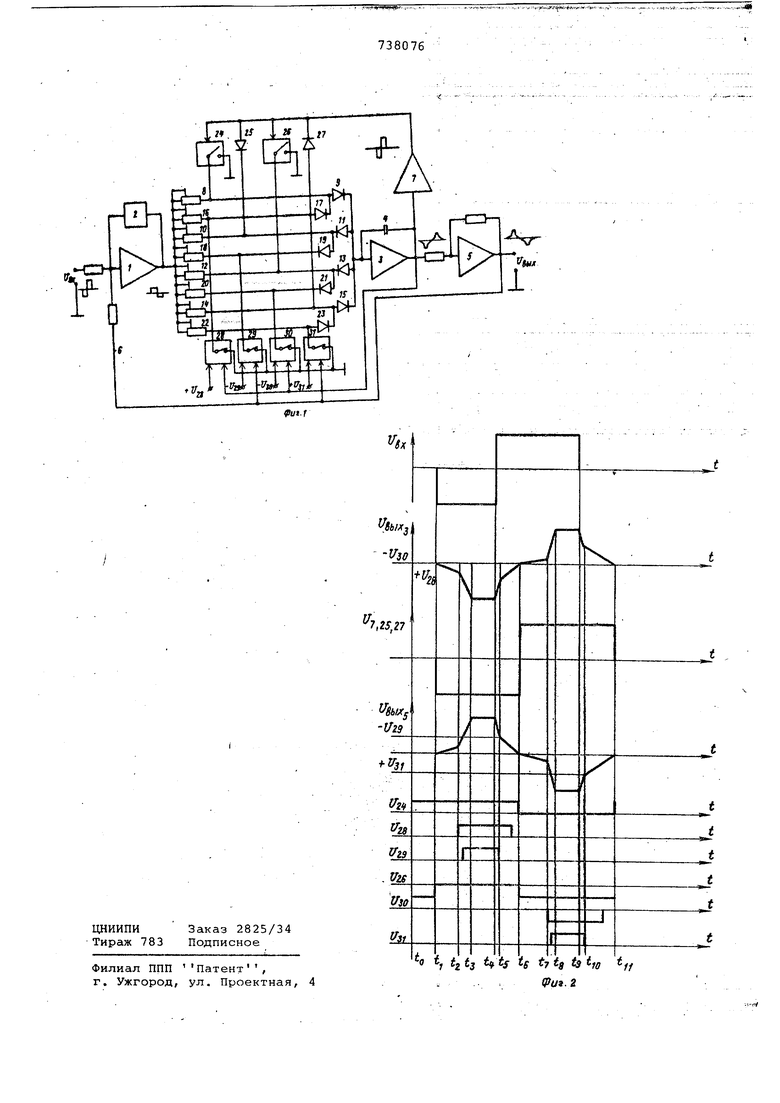

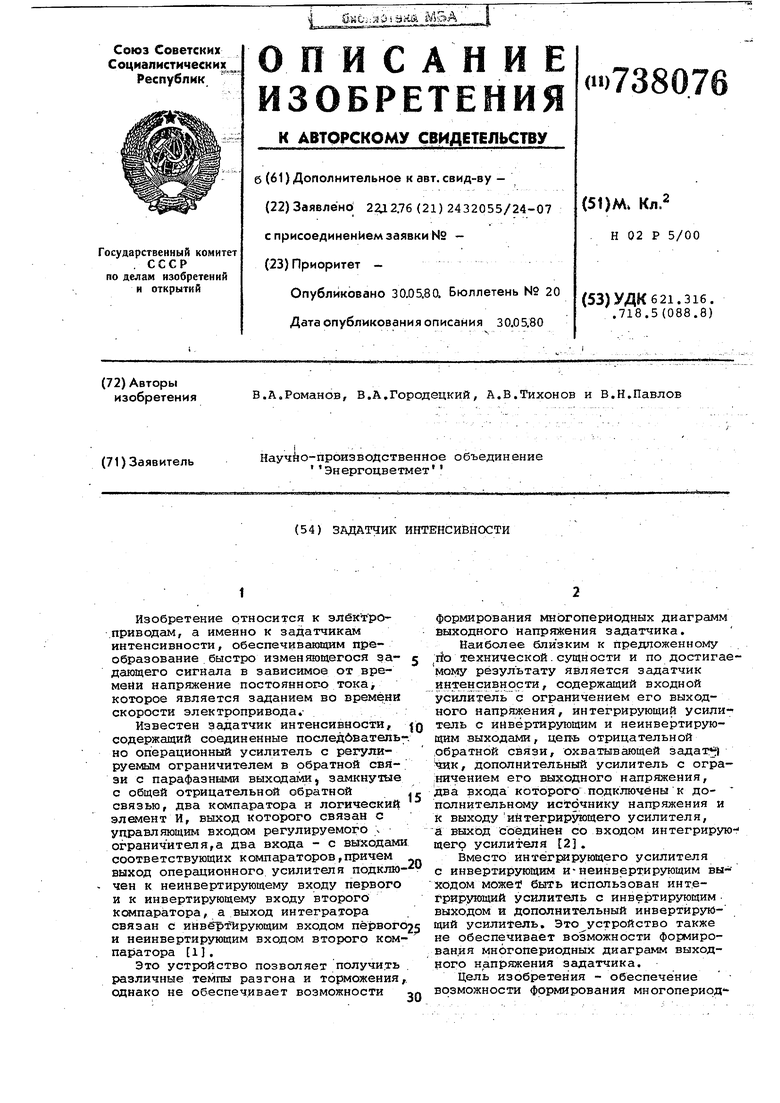

Изобретение относится к элёктро.приводам, а именно к задатчикам интенсивности, обеспечивающим преобразование быстро изменяющегося задающего сигнала в зависимое от времейи напряжение постоянног-о тока, которое является заданием во времени скорости электропривода.Известен задатчик интенсивности, содержащий соединенные последбватель но операционный усилитель с регулируемым ограничителем в обратной свяаи с парафазными выходами, замкнутые с общей отрицательной обратной связью, два компаратора и логический элемент И, выход которого связан с управляющим входсял регулируемого . ограничителя,а два входа - с выходами соответствующих компараторов,причем выход операционного, усилителя подключен к неинвертирующему входу первого и к инвертирующему входу второго ксялпаратора, а выход интегратора связан с инвёрй1рующим входом пёрвого и неинвертирующим входом второго компаратора 1 . Это устройство позволяет получить различные темпы разгона и торможения однако не обеспечивает возможности формирования многопериодных диаграмм выходного напряжения задатчика. Наиболее близким к предложенному rio технической.сущности и по достигаемому результату является задатчик интенсивности, содержащий входной усилитель с ограничением его выходного напряжения, интегрирующий усилитель с инвертирующим и неинвертирующим выходами, цепъ отрицательной .обратной связи, охватывающей задат) ЧИК, дополнительный усилитель с огра;ничением его выходного напряжения, два входа которого подключены к дополнительному источнику напряжения и К выходу интегрир щего усилителя, а выход соединен со входом интегрирую-щего усилителя 2. Вместо интегрирующего усилителя с инвертирующим и-неинвертирующим выходом можеф быть использован интегрирующий усилитель с инвертирующим выходом и дополнительный инвертирующий усилитель. Это устройство также не обеспечивает возможности формирования многопериодных диаграмм выходного напряжения эадатчика. Цель изобретения - обеспечение возможности формирования многопериод ных симметричных и несиммётрич 5ых диаграмм выходного напряжения задатчйка. Эта цель достигается тем, что задатчик интенсивности, содержащий входной усилитель с включенным в цепь его обратной связи устройством ограничения напряжения, последовательно соединенные интегрирующий и инвертирующий усилители и цепь жесткой отрицательной обратной .связи, охватывающей задатчик, снабжен подключенным к выходу интегрирующего ус Лйтёдя неинвертирующим релейным усилителем, включенными между выходом входного усилителя и суммирующей точ кой интегрирующего усилителя основ нымй цепями скорости изменения выходного напряжения задатчика каждая из которых образована последо --Ва ёЛьнб соединенными резистором и диодом, подключенными параллельно ре зисторам указанных основных цепей и выполненными в виде последовательно соединенных резистора и диода дополнительными цепями задания скорости изменения выходного напряжения за датчика, подкл1рченными к точкам между резистором и диодом указанных основных и дополнительных цепей ключе -1Ш1й эЙШёнтамй7 й1Ё йэ%Ш ВХОДЫ ключевых элементов основных цепейЭадания скорости изменения выходного напряжения задатчика соедине нУ с выходом неинвертирующего релей ногоусилителя, а управляющие входы допрлнительных цепей задания скорости изменения выходного напряжения зад а тчи к а сое д ин с вы хоДа1Ми и н тегрирующего и инвертирующего усиV, лителя. На фиг.1 представлена функционал ная схема предложенного задатчика интенсивности; на фиг.2 - диаграмма входного и частный случай диаграммы йыхоДного напряжения, поясняющие рабЬту задатчика, Задатчик .интенсивности содержит входной усилитель 1, с ключенным в цепиего обратной связи устройством ограничения напряжения 2, последова т ельно соединенные интегрирующий ус датель 3 с включенным в цепи его: обратной связи конденсатором 4 и ин бертирующий усилитель 5, цепь жестк отрицательной обратной связи ё, охватывающей задатчик, подключенный к ВЫХОДУ интегрирующего усилителя 3 неинвёрТйруййцййрёлёй ый усилитель включенные между выходом входного усилителя 1 и суммирующей точкой ин тегрйруюЩего Усилителя 3 основные -цепи задания скорости изменения выходного напряжения задатчика, каж - йаТййтйрлх образована последователь Но соединенными резистором й ДйоДбМ (пе{5вая основная цепь - рези.стор 8 и диод 9, втораяосновная цепь - ре зйстор 10 и диод 11, третья осйбвйа цепь - резистор 12 и диод 13, Чётве

738076 ая основная цепь - резистор 14 и иод 15), подключенные параллельно езисторам указанных основных цепей выполненные в виде последовательно оединенных резистора и диода дополительные цепи задания скорости измеения выходного напряжения задатчика (первая дополнительная цепь - резистор 16 и диод 17, вторая дополнительная цепь - резистор 18 и диод 19, третья . дополнительная цепь - резистор 20 и диод 1,четвертая дополнительная цепь - резистор 22 и диод 23),подключенные к общим точкам резисторов и диодов в указанных основных и дбполнй-i тельных цепей ключевые элементы 24,25/ 26,27,28,29,30,31, причем -управляющие входы ключевых элементов 24, 25, 26, 27 основных цепей задания скорости изменения выходного напряжения задатчика соединены с выходом неинвертируюшего релейного усилителя 7, а управляющие входы -ключевых элементов 28,29,30,31 дополнительных цепей задания скорости изменения выходного напряжения задатчика соединены с выходами интегрирующего 3 и инвертирующего 5 усилителей. В исходном состоянии в моменты времени, t , когда й О, открыты две основные цепи задания скорости изменения выходного напряжения задатчика: первая (резистор 8 и диод 9) и третья (резистор 12и диод 13), а вторая и четвертая основные цепи блокированы нулевым потенциалом с неинвертирующего релейного усилителя .7 через ключевые элементы 25 и 27, при этом все дополнительные цепи за- . дания скорости изменения выходного напряжения задатчика блокированы нулевым потенциалом через ключевые элементы 28, 29, 30, 31, При подаче в момент времени t, на входной инвертирующий усилитель 1 дискретного сигнала U (фиг. 2) напряжение на его выходе изменяется скачком до величины напряжения ограничения Uorp/ определяемой уставкой устройства 2 ограничения напряжения. Напряжение положительной полярности, равное Uorp , через первую основную цепь задания скорости изменения выходного йапряжёния задатчика (ре-, зистор 8 и диод 9) поступает на вход интегрирующего усилителя 3. Третья основная цепь (резистор 12, диод 13) разомкнута для положительного сигнала обратно включенным дио-дом 13. При появлении на выходе интегрирующего усилителя 3 сигнала, отличного от.нуля, срабатБ вает неинвертирующий релейный усилител. 7, на выходе которого скачком появляется напряжение отрицательной полярйости. При этом ключевой элемент 25 разомкнется и деблокирует вторую основную , цепь задания (резистор 10 и диод 11), саднако вторая основная цепь задания для положительногосигнала закрыта .диодом 11, третья основная цепь зад ния (резистор 12 и диод 13) блокируется нулевым потенциалом замкнуто го ключевого элемента 25, четвертая основная цепь задания (резистор 14 и диод 15) по-прежнему блокирована ключевым элементом 27. , С момента времени t. до момента времени tg интегрирующий .усилитель 3 линейно развертывает во времени сигнал UOPP с постоянной времени интегрирования Т.2 Rg. С . Выходное напряжение задатчика Ug,,, - момент враи1ени tg , когда выходнЬе напряжение интегрирующего усилителя 3 сравняется по модулю с напряже нием смещения + Uno ключевого злемента 28, последний разомкнется, деблокируя первую дополнительную цепь (ре зистор 16, диод 17}. Ключевой элемент 28 выполнен, например, на тран зисторе п-р-п-проводимости. С этого момента сигнал поступает на вход интегрирующего усилителя 3 по двум цепям - первой основной и первой дополнительной-и интегрирование идет с постоянной времени Количество дополнительных цепей в каждой основной цепи задания определяется числом изломов на диаграмме выходного напряжения задатчика интен сивности и задается требованиями кон кретного электропривода. Когда выходное напряжение инвертирующего усилителя 5 (и, ) сравняется по модулю с напряжением смещения - U, ключевого элемента 29, последний разомкнется, деблокирует вторую допо нительную цепь (резистор 18 и диод 1 однако эта цепь останется закрытой для входного положительного напряжёния диодами 19 и 11. В момент tj, когда выходное напряжение задатчика ( ) {Сравняется по модулю с входным напряжением (и их )/ напряжение на выходе входного инвертирующего усилителя 1 резк падает до нуля и процесс интегрирования прекращается. В момент времени Ц при смене знака входного напряжения полярность нahpяжeния Uorpменяется на отрицательную. Напряжение поступает на вход интегрирующего усилителя 3 через Открытые вторые основную (резистор 10 и диод 11) и дополнительную (резистор 18, диод 19)цепи задания скорости изменения выходного напряжения задатчика. Интегрирование идет с пЬстоянной времени 29 В момент времени t, когда выходнее ;наърЖёнйё ий feeрти руадёго- з ей да тёйя 5 BHOBbi сравняется по модулю с напряжением смещения UUg ключевого элемента29, последний замыкается, блокируя вторую дополнительную цепь задани (резистор 18, диод 19). С этого момента интегрирование идет с постоянной времени 5-6 0 В момент .времени tg напряжение на выходе неинвертирующего релейного усилителя 7 скачком также К1еняет полярность на положительную. При этом по сигналу с неинвертирующего релейного усилителя 7 ключевыми элементами 26, 27 деблокируются третья и четвертая основные цепи задания, ключевыми элементами 24, 25 блокируется перва Г и вторая основные цепи заданий. Однако четвертая основ,ная цепь задания будет закрыта для ;отрицательного входного сигналадйОдом 15. Напряжение U поступает на вхОДйнт&грйрующёго усилителя 3 черё - те& гж ъстт т--ттт (резистор -12, диод 13). Третья дополнительная цепь згадаьгйй (резистор 20, диод 21) блокирована ключевьлм элементом 30, так как I Ujo i I bijix 0| Интегрирование идет с постоянной времени Т,-, - Rjg момент времени tj. , когда выходное напряжение интегрирующего усилителя 3 сравняется по модулю с напряжением смещения Uj Цлючевого элемента 30, последний разомкнется, деблокируя Т1:ГёЧЁ дОп ШтШтёлънУйи;ёг1ьбадайия (резистор 20, диод 21). С этого момента интегрирование идет с постоянной времени 20 Когда выходное напряжение инвертирующего усилителя 5 сравняется по модупю с напряжением смещения U5 ключеес5го элемента 31, последний разомкнется, деблокируя четвертую дополнительную цепь задания (резистор 22, диод 23) , однако эта цепь остае ся закрытой для входного отрицательного напряжения диодом 23. В момент времени 8 огда выходное напряжение задатчика и,у сравняется по модулю с входным напряжением Ugj{, напряжение на выхсзде входного усилителя резко падает до нуля и.интегрирование прекращается. В момент времени tg,при смене знака входного напряжения полярность напряжения Ц,вновь меняется на поло)йительную. Напряжение поступает на вход интегрирующего усилителя 3 через открытые четвертую основную (резистор 14, диод 15) и четвертую дополнительную (резистор 22, диод 23) цёпи задания, а третья основная и третья дополнительная цепи задания закрыты диодами 13 и 21 для положительного входного сигнала. Остальные цепи задания блокированы. Интегрирование идет с постоянной времени . В момент времени t,,, когда выходное напряжение инвертирующего усилителя 5 вновь сравняется ; по модулю с напряжением смещения Uj, ключевого элемента 31, последний замыкается, блокируя четвертую дополнительную цепь задания (резистор 22, диод 23) С этого момента интегрирование идет с постоянной времени T,O,,| R,c С , т.е В момент времени t,, , когда напр жение на выходе интегрирующего усили теля 3 меняет полярность на противоположную, напряжение на выходе неин вертирующего релейного усилителя 7 также меняет полярность на отрицате/1ьную. С этого момента работа зад чика интенсивности циклически повто ряется .Работа задатчика интенсивнос описана на примере случая, когда интенсивность выходного сигнала пос ле точек излома возрастает. Если не . обходимо уменьшить интенсивность после точек излома, то ключевые элементы соответствующих дополнител ных: каналой выполняются таким образом, что дополнительные каналы откр ваются одновременно с основными кан лами при переходе диаграммы через нуль и закрываются в точках излома. Уровень напряжения в точках излома в задатчикё задается величиной напряжений смещения ключевых элементов 28, 29, 30, 31. Использование изобретения позволит осуществить независимую устав ку углов наклона и создать переменную крутизну фронтов каждой ветви диаграммы выходного напряжения зада чика интенсивности. Это расширит ег . функциональные возможности . Формула изобретения Задатчик интенсивности, содержащий входной усилитель с вклвэченным

738076 в цепи его обратной связи устройством ограничения напряжения , последовательно соединенные интегрирующий и инвертирующий усилители и цепь жесткой отрицательной обратной связи, охватывающей задатчик, отлич.ающийс я тем, что, с целью обеспечения возможности формирования многопериодных симметричных и несимметричных диаграмм выходного напряжения задатчика/ в него введены подключенный к выходу интегрирующего усилителя, неинвертирующий релейный усилитель, включенные между выходом входного усилителя и суммирующей точкой интегрирующего усилителя основные цепи задания скорости изменения выходного напряжения задатчика, каждая из которых образована последовательно соединенными резистором и диодом, подключенные параллельно резисторам указанных основных цепей и выполненные в виде последовательно соединенных резистора и диода дополнительные цепи задания скорости изменения выходного напряжения задатчика, подключенные к общим точкам резисторов и диодов указанных основных и дополнительных цепей ключевые элементы, при этом управляющие входы ключевых элементов основных цепей задания скорости изменения выходного напряжения задатчика соединены с выходом неинвертирующего релейного усилителя, а управл5вощие входы ключевых элементов дополнительных цепей задания скорости изменения выходного напряжения задатчика - с выходом интегрирующего и инвертирующего усилителей . - . . -;.... ..-. ./. ; , -. ....... I . Источники информации, принятые во внимание при экспертизе i .Авторское свидетельство СССР №489075 кл. G 05 В 11/00, 1973, 2. Патент ФРГ № 1126487, кл. 21 с 59/36, 1967. . L 1 I 7 g,i FTlf Чт

Авторы

Даты

1980-05-30—Публикация

1976-12-22—Подача