- --1

Устройство относится к области электротехники и может быть использовано при построении систем управления тиристорными преобразователями.

Известны устройства пля управления тиристорными преобразователями yLj , содержащие двухтактный ключевой каскад, работающий в автоколебательном режиме, трансформатор, токоограничивающие резисторы в цепях баз транзисторов двухтактного ключевого каскада, дополнительный транзистор, резистор, ограничивающий ток кЬллектора дополнительного транзистора, резистор смещения дополнительного транзистора. К недостатеам устройства относится низкий коэффициент полезного действия, за счет наличия бросков тока при переключении транзисторов двухтактного ключевого каскада, а также из-за потерь в дополнительном транзисторе.

Известно также устройство для управления тиристорами |2J,содержащее в своем составе двухтактный ключевой квокад, работающий в автоколебательном режиме, выходной трансформатор, ЯВЛЯЮЩИЙСЯ нагрузкой двухтактного ключевого каскада, управляющий транзистор, эмиттер которого соединен с источником смещения, резистор, ограничивающий ток управляющего чранзистора, диоды, соединяющие базы транзисторов двухтактного ключевого Каскада р коллектором управляющего транзистора через базовые обмотки

10 выходного трансформатора, и ограничивагюшие резисторы, включенные в базовые цепи транзисторов двухтактного ключевого каскада.

К недостаткам устройства относится

15 низкий КПД, тяжелый режим работы управляющего транзистора, сложная схема из-за наличия источника смещения.

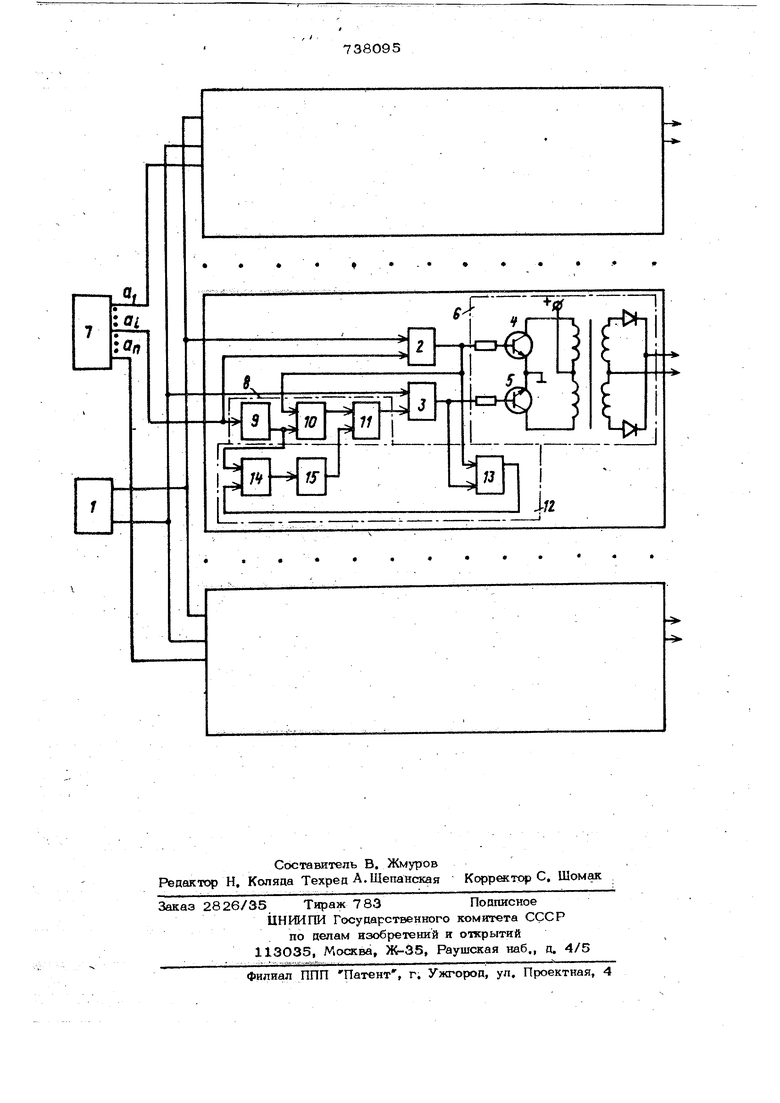

Наиболее близким по технической сущ2ф ностя к изобретению является устройство для управления тиристорным преобразователем 3 , содержащее задающий генератор, распределитель импульсов по каналам, выходной двухтактный ключевой Каскаа, цопоп ни тельный транзистор, подключенный через резистор параллельно г1ёрШЬду коллектор-эмиттер(ЭцногрHis транзисторов двухтактного ключевого ка кЩЖ it отпираемого в паузах между упр авйяюишми импульсами, RS-Цепочку, ос ществляющую включение определенного транзистора двухтактного ключевого кас karia при поступлении управляющего импульса, 6граЩ1чйвающие резисторы, вклю ченные в базовые цепи транзисторов дву тактного ключевого каскада. Извертное устройство имеет тот недостаток, чТо наличие дополнительного Транзистора, подключенного параллельно переходу коллектор -эмиттер одного из транзисторов дбухтактного ключевого ка када и отпираемого в паузах между управляющими импульсами, значительно сн жает помехоустойчивость всего устройства. Целью изобретения является повышение помехоустойчивости устройств для управления гаристорными преобразователями. Поставленная цель достигается тем, что устройство для управления тиристорным преобразователем, содержащее задающий генератор, распределитель импульсов по каналам и выходной двухтакч ный каскад на ключах переднего и задне го фронта HMiltyjibCOB управления в каждо канале,дополнительно снабжено в каждом канале модуляторами управляющих импульсов ключей переднего и заднего фронта 1зыходного каскада, узлом очёред ности работы модуляторов, вьшолненным м инверторе, -триггере ячейки запрета и логической схеме ИЛИ, и узлом соСтоявия ключей в.ьтхбдного каскада, вы полненным на Re -триггере ячейки памяти, логической, схеме И и одновйбраторе, причем выход задающего генератора пошслючен к одному из входов обоих модуляторов каждого йанал к др угом у входу одйого изкоторЬга: нёгосрёаственно, а второго через узел очере дности подключен Bbix6ft данного канала распреаелителяимпул iboiB, при этом выходы модуляторов подключены к управляюцщм входам ключей выходного каскада и входам R $ -триггера ячейки памяти, выход которого под кшбчен к одному из входов схемы И, к другом входу которой подключен выход входного инвертора узла очередности, а выход схемы И через одновибратор вклю чен на один из входов выходной схемы ИЛИ узла очередности, к другому входу 9S4. которой подключен, выход Re -триггера ячейки запрета, на входы которого подключен выход инвертора и модулятора ключа переднего фронта. На чертеже представлена приншшиальная схема устройства. Устройство содержит задающий генератор 1, выходы которого подключены к одному из входов модуляторов 2 и 3 управляющих импульсов ключей переднего 4 и заднего 5 фронта выходного двухтактного каскада 6. Выход данного канала распределителя 7 управляющих импульсов по каналам подключен на второй вход модулятора 2 ключа переднего фронта 4 и ко входу узла очередности 8 работы Модуляторов, выход которого подключен на второй вход модулятора 3 ключа заднег9 фронта 5. Узел очередности 8 состоит из входного инвертора 9 выход которого подключен к одному из входов Р -триггера ячейки запрета 10. на второй вход которого подается сигнал с выхода модулятора 2. BыxoдlЧS-тpиггера ячейки запрета 10 подключен к од- ному из входов вьпсодной логической схемы ИЛИ 11, к другому входу которой подключен выход узла состояния 12 ключей выходного двухтактного каскада 6, состоящего из RS -триггера ячейки памяти 13, на входы которого подаются сигналы с модуляторов 2 и 3, логической схемы И 14, один из входов которой связан с выходом RS -триггера ячейки памяти 13, а другой - с выходом инвертора 9 узла очередности 8, и выходного одновибратора 15, включенного на выход схемы И 14. Устройство работает следующим образом. Как толь;ко на t -ом выходе распределителя управляющих импульсов 7 появится управляющий импульс, он постуйит на один из входов модулятора упра&г ляющих иктульсов 2 ключа переднего фронта 4 и откроет его. Одновременно с запрещающего входа RS -триггера ячейки запрета 10 узла очередности 8 снимает ся запрещающий единичный сигнал. Первый заполняющий импульс, которь1й появится на выходе модулятора управляющих импульсов 2 включит транзисторный ключ 4 переднего фронта двухтактного ключевого каскада б н поступит на разрешающий вход RS -триггера ячейке запрета 10, йер ёвйДя его в единичное состояние. Единичный сигнал с выхода ячейки 10, пройдя через схему ИЛИ 11, откроет 57 модулятор управляющих импульсов 3 клю заднего фронта 5 для прохождения заполн ющих импульсов. Таким образом, оба мод лятора управляющих импульсов оказывают ся открытыми и обеспечивают нормальную работу двухтактного ключевого каскада 6, причем первым всегдй бключается тра зистор переднего фронта импульса управления. После окончацие управляющего импуль са оба модулятора закрываются, а на вхо схемы И 14 с выхода инвертора 9 подается единичный сигнал. Если последним открывался транзисторый ключ 5 двухтактного ключевого каскада 6, т.е. последний заполняющий импульс прощел через модулятор управляющих импульсов 3, то в этом случае -триггер ячейки памяти 13 узла состояния 12 ключей выходного двухтактного каскада 6 примет нулевое состояние и одновибратор 15 не получит- разрешения на запуск. Если же последним открывалс транзистор 4 двухтактного ключевого каскада 6, то RS -триггер ячейки памяти,13 примет единичное состояние. В этом случае на входе одновиоратора 15 появится сигнал запуска, и на выходе сформируется импульс, длительность которого не больше длительности заполняющего импульса, но. достаточная для надежного открывания транзистора 5 двухтактного ключевого каскада 6. Этот импульс, пройдя через схему ИЛИ 11, откроет мбдулятор 3 управляющдх импульсов ключа за:днего фронта 5 и пропустит на его вьхход заполняющий импульс. Транзистор 5 двухтактного клю чевого каскада 6 откроется и переведет трансформатор выходного каскада б в исходное состояние. Одновременно RS триггер ячейки памяти 13 выдаст на своем выходе нулевой сигнал и закроет схему И 14 запуска одновибратора 15. По окончании импульса на выходе одновибратора 15 модулятор управляющих импульсов 3 ключа заднего фронта 5 зак роется, и схема примет исходное состояние. Таким образом, при поступлении управляющего импульса в каждом канале первым включается транзистор 4 двухтактного ключевого каскада б, а при окончании управляющего импульса пооледним открывается транзистор 5. Поэтому состояние выходного трансформатор двухтактного каскада б перед поступлением очередного управляющего им56. пульса является определенным, и заполняющий импульс, поступающий нэ управляющий переход тиристора будет иметь такую же амплитуду и длительность, как и все последующие, что обеспечит четкое включение силового тиристора тиристор н6го преобразователя и высокую помехоустойчивость системы управления. Формула изобретения Устройство для управления тиристор- ным преобразователем, содержащее задающий генератс, распределитель импульсов, по каналам и вьп1Ьдйой двухтактный каскад на ключах переднего и заднего фронта импульсов управления в каждом канале, отличающееся тем, что, с целью повышения помехоустойчивости, оно снабжено в каждом канале модуляторами управляющих импульсов ключей переднего и заднего фронта выходного каскада, узлом очередности работы модуляторов, выполненным на инв ртфеЯЭтриггере ячейки запрета и логической схеме ИЛИ, и узлом состояния ключей выходного каскада, выполненным aaRS триггере ячейки памяти, логической схеМО И и оцновибраторе, причем выход задающего генератора подключен к одному из входов обоих модуляторов каждого канала, к другому входу одного из непосредственно, а второго через узел очередности подключен выход данного канала распределителя импульсов, при этом выходы модуляторов подключены к управляющим входам ключей выходиэго каскада и входам Rs -триггера ячейки памяти, которого подключен к одному из вхогдов схемы И, к другому входу которой подключен выход входного, инвертора узла очерёдности, а выход схемы И через одновибратор включен на опин яз вхооов выходной схемы ИЛИ узла очередности к другому входу которой подключен выход RS -триггера ячейки запрета, на входы которого подключен вь1ход инвертора и модулятора ключа переднего фронта. Источники ин|)ормации, принятые во вн имание при экспертизе 1,Авторское свидетельство CICCP № 440759, кл. Н 02 Р 13/16 1974. 2,Авторское свидетельство СССР № 474083, кл. Н 02 М 1/08, 1975. 3,Авторское свидетельство СССР № .464949, кл. Н 02 Р 13/16, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления статическим преобразователем | 1980 |

|

SU868967A1 |

| Устройство для управления тиристорным преобразователем | 1982 |

|

SU1019572A1 |

| Двухтактный преобразователь напряжения | 1980 |

|

SU982161A1 |

| Устройство для управления силовыми ключами плеча инвертора | 1989 |

|

SU1757045A1 |

| Стабилизированный источник вторичного электропитания | 1982 |

|

SU1049876A1 |

| Цифровое устройство для управления машиной непрерывного литья заготовок | 1989 |

|

SU1632621A1 |

| Стабилизированный по напряжению трехфазный мостовой инвертор | 1977 |

|

SU720636A1 |

| Стабилизированый источник электропитания | 1990 |

|

SU1725355A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Преобразователь напряжения с защитой от перегрузок | 1982 |

|

SU1157626A1 |

Авторы

Даты

1980-05-30—Публикация

1977-06-09—Подача