(54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ Изобретение относится к импульсной технике. Известен умножитель частоты, содержащий генератор счетных импульсов, частота которых больше частоты входных сигналов, счеТчик импульсов, содержаишй W разрядов, второй m -разрядный счетчик импульсов, формирующие триг.геры логические элементы И и . Умножитель имеет недостаточную стабильность при низких частотах входного сигнала. Наиболее близким по технической сущности является умножитель частоты, содержащий импульсный генератор, выхоа которого соединен с первыми входами логич ких элементов И, второй вход первого из которьпс соединен с входом первого формирователя передних фронтов, второй вх.о второго логического элемента И соединен с входом второго формиров.1теля пе редних фронтов, выходы каждого логического элемента И и соответствующего ему формирователя передних фронтов соедиИМПУЛЬСОВнены с входами Ъдного из двух счетчиков, вькод каждого из которых соединен с первым входом одного из двух бяо- ков сравнениями логический элемент ИЛИ два входа которого соединены с выходами упомянутых формирователей передних фронтов Hi . Недостатком этого умножителя является недостаточная точность установки и малый диапазон изменения коэффици-, ента умножения. Целью изобретений является увеличение точностаг установки и расширение диапазоне изменения коэффициента умножения. Умножитель частоты следования импульсов, соДержаишй импульсный генератор, вЫх:од которого соединен с первыми входами логических элементов И, второй вход первого из которых соединён с входом первого формирователя передних фронтов, второй вход второго логического элемента И соедине1г с входом второго формирователя передних фронтов, выходы каждого логического элемента И и соответст вующего.ему формирователя пере ддах фронто соединены с входами одного из двух счетчико импульсов, выход каждого из которых соедин с первым входом одного из двух блоков сравйения, и логический элемент ВДИ, два входа которого соединены с выходами упомянутых формирователей передних фронтов, введены триггер, два до- . полнительных счетчика импульсов и четыре дополнительных логических элемента И, выходы двух из которых соединены с дополнительными входами логического элемента ИЛИ, а первые входы - соединены с вторым входом одного из логических элементов И и одним из выходов триггера, вход которого подключен к входной шине, первые входы двух других дополнительных логических элементов И соединены соответственно с выходами фор

мирователей передних фронтов, выходы .этих дополнительных логических эпементов И подключены к первым входам дополнительных счетчиков импульсов, вторые входы которых подключены к выходам соответствующих логических элементов И, а выходы дополнительных счетчиков импульсов соединены со вторыми входами блоков сравнения, выход одного из которых соединен со вторыми входами первого и третьего, а выход второго блока сравнения соединен со вторыми входами второго и четвертого упомянутых дополнительных логических элементов И,

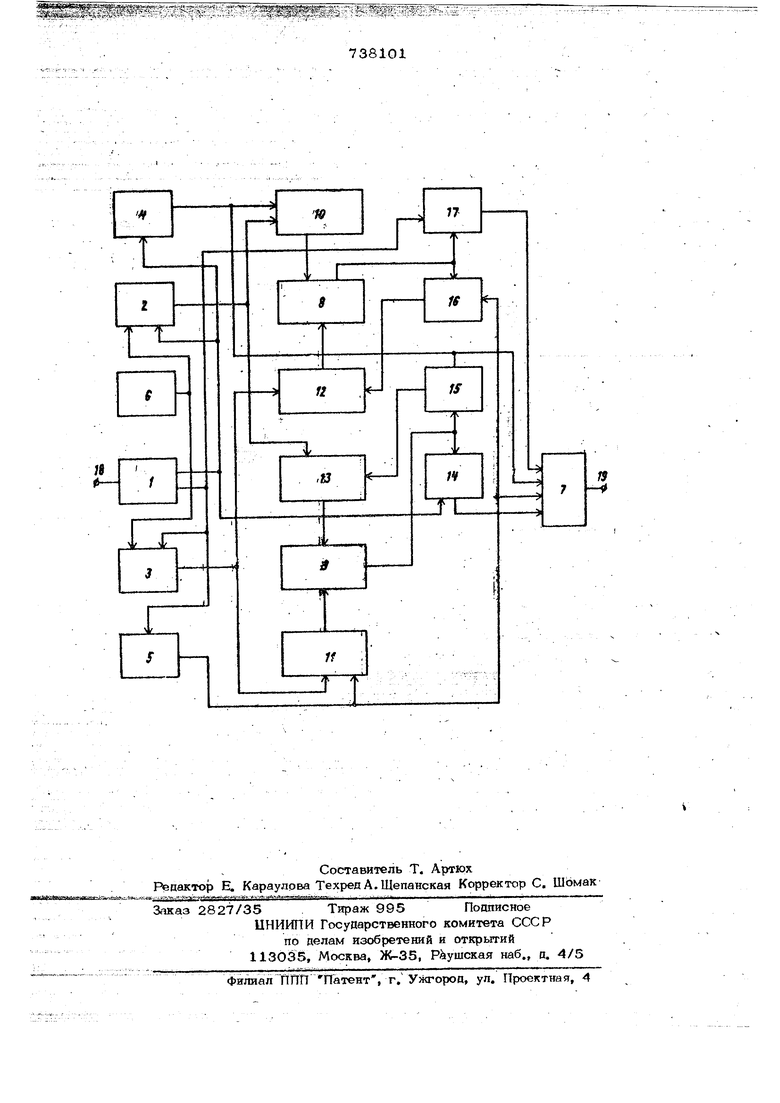

Структурная электрическая схема описываемого умножителя приведена на чертеже,

Умножитель содержит триггер 1 логические элементы И 2, 3, формировател передних фронтов 4, 5, импульсный генератор б, логический элемент ИЛИ 7,, блоки сравнения 8, 9, счетчики 10,11 импульсов, дополнительные счетчики 12, . 13 импульсов,дополнительные логические элементы И 14 ,.. 17, Входной сигнал подан на входную шину 18, выходной сигнал снимается с вьпсода 19.

Принцип работы умножителя заключае гся в следующем.

Пусть за период следования импульсов входной последовательности счетчик 11 с импульсного генератора 6 поступило 24 импульса, т.е. была произведена запись числа 24 и происходит умножение частоты на 4. В моКгент времени IQ триггер 1 переходит из состояния О в состояние 1. На выходе формирователя 7

мент И 15 на сброс с четчика 13. Затем при поступлении 12-ого импульса на счетчик 13, на выходе блока сравнения 9 формируется импульс и весь процесс повторяется снова до окончания периода входной последовательности. Счетчик 10 при этом подсчитывает импульсы за.период Т и в формировании выходных импулсов, на данном периоде, не участвует. На выход устройства поступают только импульсы с блока сравнения 9 через логи ческий элемент И 14, Логический элемен И 17 заперт низким уровнем напряжения поступающего с инверсного выхода триггера 1 для исключения сбоев в выходной последовательности из-за ложного срабатывания блока сравнения 8. В новом периоде, в момент времении t /), триггер 1 переходит из состояния состояние О, На выходе формирователя переднего фронта 5 формируется короткий импульс, поступающий через логический элемент ИЛИ на выход устройства, на сброс счетчика 11 и череэ логический элемент И 16 на сброс счетчика 12. Импульсы с генератора 6 через логическ11й элемент И 3 поступают на счетный вход счетчика 11 и на счетный вход счетчика 12, Число, записанное в (N-2) старших разрядах счетчика 10, сравнивается с числом, записанным в счетчике 12, ИмПульсы равенства с выхода блока сравнения 8 через логический элемент И 17 через логический элемент ИЛИ 7 поступают на выход устройства и через логический элемент И 16 - на сброс показаний счетчика 12. Весь процесс, происходящий за предыдущий период,повторяется снова. 014переднего фронта 4 формируется короткий импульс, поступающий на вход сброса счетчика 10, через логический элемент И 15 на вход сброса счетчика 13 и через логический элемент ИЛИ 7 на выход устройства, С генератора 6 через логический элемент И 2 на счетный вход счетчика 10 и счетный вход счетчика 13 поступают импульсы. Блок сравне- . Еия 9 сравнивает число, записанное в (Н-2) старших разрядных счетчика 11 с числом, записанным в счетчике 13. Для данного примера в ( Н -2) Старших раз{эядах счетчика 11 записано число Это значит, что при поступлении 6-го импульса на счетчик 13 на выходе блока сравнения 9 формируется импульс, поступаюиотй через логический элемент И 14, через логический элемент ИЛИ 7 на выход устройства и через логический элеТаким образом, на выходе формируется последовательность импульсов, частота которой в четыре раза больше частоты входной последовательности импульсов. При увеличешш частоты импульсов с генератора 6 можно увеличить разрядность счетчиков и осуществлять умножение частоты на более высокое число, а также повысить точность умножения, Иэменением числа сравниваемых разрядов можно изменять коэффициент умножения в широких пределах. К достоинствам уст ройства относится также то, что, чем ниже частота следования входных импуль сов, тем более точно осуществляется умножение входной частоты на данный коэф фициент умножения. Описываемое устройство может осуществлять умножение ультранизких частот (доли герца). Появляющиеся сбои автоматически устраняются в последующем периоде входной последовательности, фаза выходной последовательности импульсов жестко связана с фазой входной последовательности импульсов. В связи с тем, что устройство вьшолнено полностью на элементах цифровой техники, это дает возможность осуществить микроминиатюризацию схемы, улучщить ее эксплуатационные характеристики, а именно: снизить габариты и вес, снизить потребляемую мощность, расширить температурный диапазон. Формула изобретения Умножитель частоты следования импул сов, сод ержащий импульсный генератор, выход которого соединен с первыми входами логических элементов И, второй вхо первого из которых соединен с входом первого формирователя передних фронтов, второй вход второго логического элемента И соединен с входом второго формирователя передних фронтов, выходь/ каж дого логического элемента И и сортветствующего ему формирователя передних фронтов соединены с входами одного из . двух счетчиков импульсов, ьыход каждого из которых осоединен q первым входом одного из двух блоков сравнения, и логический.,элемент ИЛИ, два входа которого соединены с выходами упомянутых формирователей передних фронтов, отличающийся тем, что, с целью увеличения точности установки и расширения диапазона изменения коэффициента умножения, в него введены триггер, два Дополнительных счетчика импульсов и четыре дополнительнЬ1Х логических элемента И, выходы двух из которых соединены с дополнительными входами логического элемента ИЛИ, а первые входы - с вторым входом одного из основных логических элементов И и одним из выходов триггера, вход которого подключен к входной щине, первые входы двух других дополнительных логических элементов И соединены соотве,тственно с выходами формирователей передних фронтов, выходы этих дополнительных логических элементов И подключены к первым входам дополнительных счетчиков импуЛьсов, вторые входы которых подклжэчены к выходам соответствующих логических элементов И, а выходы дополнительных счетчиков импульсов соединены с вторьт и входами блоков сравнения, выход одного из которых соединен с вторыми входами первого и Третьего, а выход второго блока сравнения соединен с вторыми входами второго и четвертого упомянутых дополнительных логических элементов И. Источники информации, принятые во внимание при экспертизе 1.Заявка Японии № 47-33978 кл. 98(5), с. 32, 28.08.72. 2.Авторское свидетельство СССР № 484619, кл. Н 03 В 19/06, 04.12.73.

738101

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1983 |

|

SU1140220A1 |

| Умножитель частоты импульсов | 1984 |

|

SU1238222A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU970632A1 |

| Умножитель частоты | 1990 |

|

SU1775840A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1188846A1 |

| Цифровой умножитель частоты следования периодических импульсов | 1981 |

|

SU997228A1 |

| Устройство для умножения следованияиМпульСОВ | 1979 |

|

SU824420A1 |

| Умножитель частоты | 1982 |

|

SU1115048A1 |

rs

Авторы

Даты

1980-05-30—Публикация

1977-11-25—Подача