Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и измерительной техники.

Целью изобретения является повышение точности.

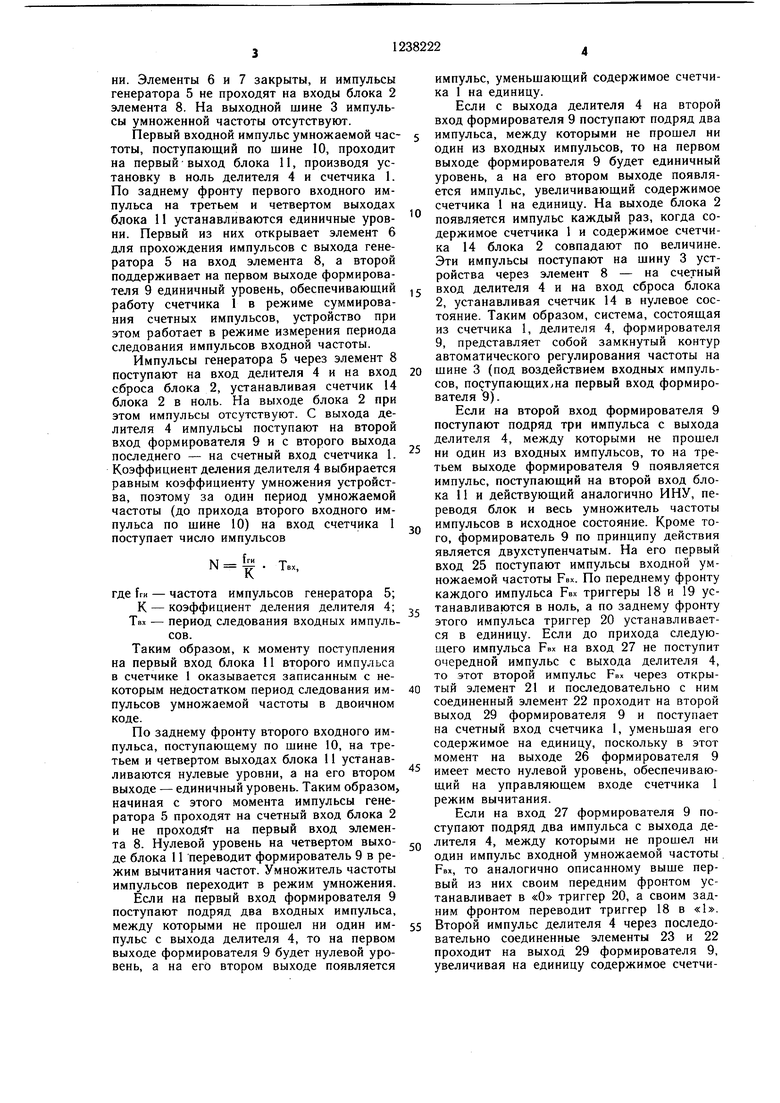

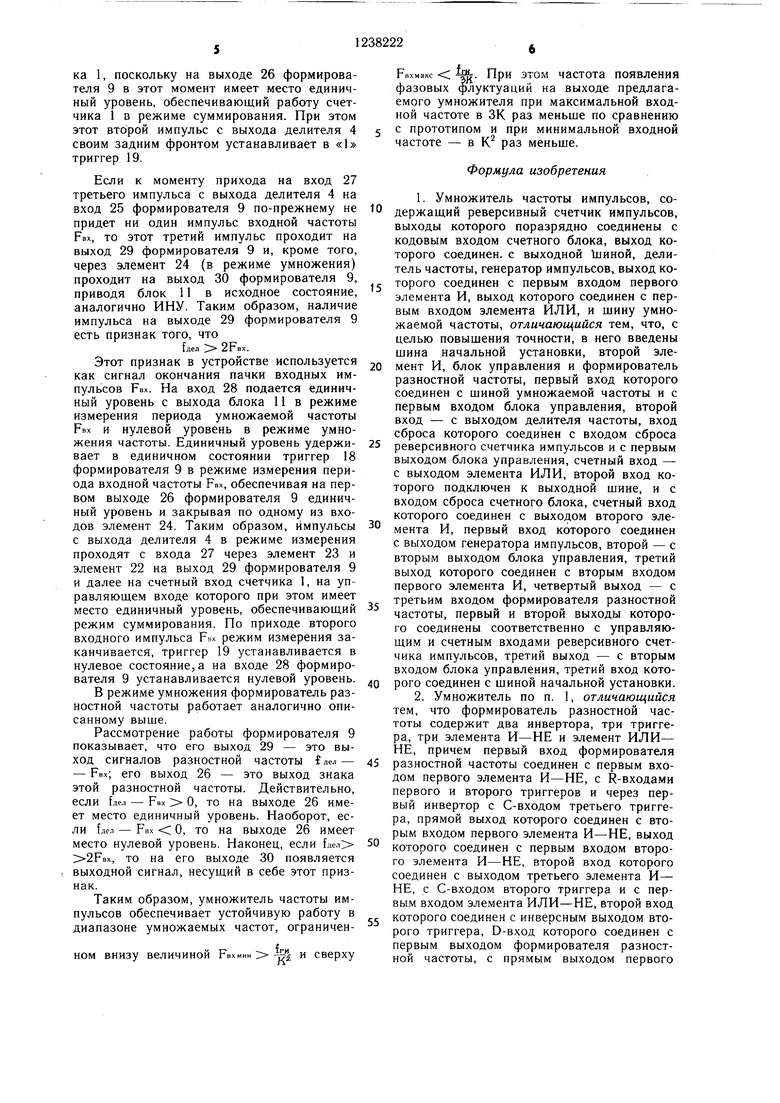

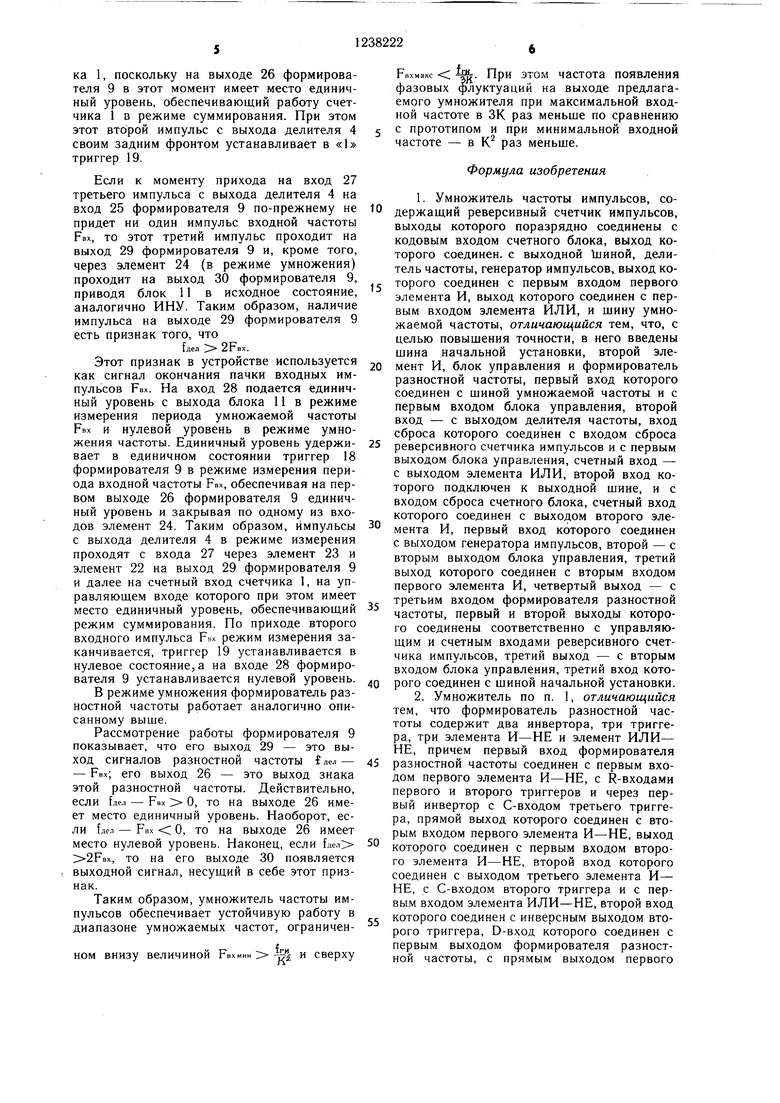

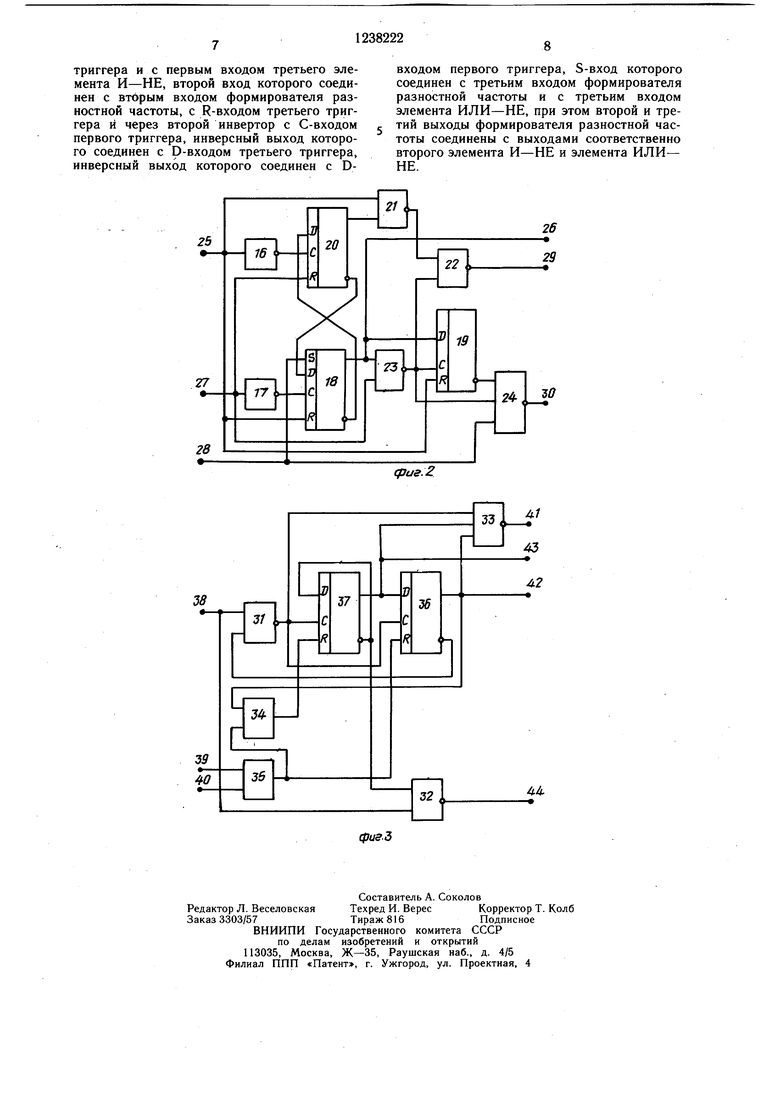

На фиг. 1 приведена электрическая структурная схема устройства; на фиг. 2 - электрическая функциональная схема формирователя разностной частоты; на фиг. 3 - электрическая функциональная схема блока управления.

Умножитель частоты импульсов содержит реверсивный счетчик 1 импульсов, выходы которого поразрядно соединены с кодовыми входами счетного блока 2, выход которого соединен с выходной шиной 3, делитель 4 частоты, генератор 5 импульсов, выход которого соединен с первыми входами первого и второго элементов 6 и 7 И, выход первого из которых соединен с первым входом элемента 8 ИЛИ, формирователь 9 разностной частоты, первый вход которого соединен с шиной 10 умножаемой частоты и с первым входом блока 11 управления, второй вход - с выходом делителя 4 частоты, вход сброса которого соединен с входом сброса реверсивного счетчика 1 импульсов и с первым выходом блока 11 управления, счетный вход - с выходом элемента 8 ИЛИ, второй вход которого соединен с выходной шиной 3, и с входом сброса счетного блока 2, счетный вход которого соединен с выходом второго элемента 7 И, второй вход которого соединен с вторым выходом блока 11 управления, третий выход которого соединен с вторым входом первого элемента 6 И, четвертый выход - с третьим входом формирователя 9 разностной частоты, первый и второй выходы которого соединены соответственно с управляющим и счетным входами реверсивного счетчика 1 импульсов, третий выход - с вторым входом блока 11 управления, третий вход которого соединен с шиной 12 начальной установки.

Счетный блок 2 состоит из элемента 13 сравнения кодов, счетчика 14 импульсов и формирователя 15 импульсов, выход которого соединен с выходом счетного блока 2, вход - с выходом элемента 13 сравнения кодов, первая и вторая группы входов которого соединены поразрядно соответственно с кодовым входом счетного блока 2 и с выходами счетчика 14 импульсов, счетный вход и вход сброса которого соединены с одноименными входами счетного блока 2.

Формирователь 9 разностной частоты содержит два инвертора 16 и 17, три триггера 18, 19 и 20, три элемента И-НЕ 21, 22 и 23 и элемент ИЛИ-НЕ 24, причем первый вход 25 формирователя 9 соединен с первым входом первого элемента И-НЕ 21, с R-входами первого и второго триггеров 18 и 19 и через первый инвертор 16 с С-входом третьего триггера 20, прямой выход которого соединен с вторым

входом первого элемента И-НЕ 21, выход которого соединен с первым входом второго элемента 22 И-НЕ, второй вход которого соединен с выходом третьего элемента 23 5 И-НЕ, с С-входом второго триггера 19 и с первым входом элемента 24 ИЛИ-НЕ, второй вход которого соединен с инверсным выходом второго триггера 19, D-вход которого соединен с первым выходом 26 формирователя 9, с прямым выходом первого триг 0 гера 18 и с первым входом третьего элемента 23 И-НЕ, второй вход которого соединен с вторым входом 27 формирователя 9, с R-входом третьего триггера 20 и через второй инвертор 17 с С-входом пер- вого триггера 18, инверсный выход которого соединен с D-входом третьего триггера 20, инверсный выход которого соединен с D-входом первого триггера 18, S-вход которого соединен с третьим входом 28 формирователя 9 и с третьим входом элемента 24

20 ИЛИ-НЕ, а второй 29 и третий 30 выходы формирователя 9 соединены с выходами соответственно второго элемента 22 И-НЕ и элемента 24 ИЛИ-НЕ.

Блок 11 управления (фиг. 3) содержит элемент 31 И-НЕ, два элемента 32 и 33

ИЛИ-НЕ, два элемента 34 и 35 ИЛИ, два триггера 36 и 37, входы 38, 39 и 40 являются соответственно первым, вторым и третьим входами блока 11 управления, первым, вторым, третьим и четвертым выходами кото, рого являются соответственно выходы 41, 42, 43 и 44, причем первый вход 38 соединен с первым входом первого элемента 32 ИЛИ- НЕ и с первым входом элемента 31 И-НЕ, выход которого соединен с С-входами первого и второго триггеров 36 и 37 и с пер вым входом второго элемента 33 ИЛИ-НЕ, выход которого соединен с первым выходом 41, второй вход - с вторым выходом 42, с первым входом первого элемента 34 ИЛИ, второй вход которого соединен с выходом второго элемента 35 ИЛИ, пер40 вый и второй входы которого соединены соответственно с вторым и третьим входами 39 и 40, и с R-входом первого триггера 36, D-вход которого соединен с третьим входом второго элемента 33 ИЛИ-НЕ, с третьим выходом 43 и с прямым выходом вто рого триггера 37, D-вход которого соединен с его же инверсным выходом и с вторым входом первого элемента 32 ИЛИ-НЕ, выход которого соединен с четвертым выходом 44, R-вход второго триггера 37 соединен

cQ с выходом первого элемента 34 ИЛИ, а инверсный выход первого триггера 36 соединен с вторым входом элемента 31 И-НЕ. Умножитель частоты импульсов работает следующим образом.

В исходное состояние устройство устанав55 ливается импульсом начальной установки (ИНУ), поступающим на второй вход блока 11 по шине 12. При этом на всех выходах блока 11 устанавливаются нулевые уровни. Элементы б и 7 закрыты, и импульсы генератора 5 не проходят на входы блока 2 элемента 8. На выходной шине 3 импульсы умноженной частоты отсутствуют.

Первый входной импульс умножаемой частоты, поступающий по шине 10, проходит на первый выход блока 11, производя установку в ноль делителя 4 и счетчика 1. По заднему фронту первого входного импульса на третьем и четвертом выходах блока 11 устанавливаются единичные уровни. Первый из них открывает элемент 6 для прохождения импульсов с выхода генератора 5 на вход элемента 8, а второй поддерживает на первом выходе формирователя 9 единичный уровень, обеспечиваюш,ий работу счетчика 1 в режиме суммирования счетных импульсов, устройство при этом работает в режиме измерения периода следования импульсов входной частоты.

Импульсы генератора 5 через элемент 8 поступают на вход делителя 4 и на вход сброса блока 2, устанавливая счетчик 14 блока 2 в ноль. На выходе блока 2 при этом импульсы отсутствуют, с выхода делителя 4 импульсы поступают на второй вход формирователя 9 и с второго выхода последнего - на счетный вход счетчика 1. Коэффициент деления делителя 4 выбирается равным коэффициенту умножения устройства, поэтому за один период умножаемой частоты (до прихода второго входного импульса по шине 10) на вход счетчика 1 поступает число импульсов

ги-р

- -J7- 1 вх, IV

где Гги - частота импульсов генератора 5; К - коэффициент деления делителя 4;

Твх - период следования входных импульсов.

Таким образом, к моменту поступления на первый вход блока 11 второго импульса в счетчике 1 оказывается записанным с некоторым недостатком период следования импульсов умножаемой частоты в двоичном коде.

По заднему фронту второго входного импульса, поступающему по шине 10, на третьем и четвертом выходах блока 11 устанавливаются нулевые уровни, а на его втором выходе - единичный уровень. Таким образом, начиная с этого момента импульсы генератора 5 проходят на счетный вход блока 2 и не проходит на первый вход элемента 8. Нулевой уровень на четвертом выходе блока 11 переводит формирователь 9 в режим вычитания частот. Умножитель частоты импульсов переходит в режим умножения.

Если на первый вход формирователя 9 поступают подряд два входных импульса, между которыми не прошел ни один импульс с выхода делителя 4, то на первом выходе формирователя 9 будет нулевой уровень, а на его втором выходе появляется

0

5

импульс, уменьшающий содержимое счетчика 1 на единицу.

Если с выхода делителя 4 на второй вход формирователя 9 поступают подряд два 5 импульса, между которыми не прошел ни один из входных импульсов, то на первом выходе формирователя 9 будет единичный уровень, а на его втором выходе появляется импульс, увеличивающий содержимое счетчика 1 на единицу. На выходе блока 2 появляется импульс каждый раз, когда содержимое счетчика 1 и содержимое счетчика 14 блока 2 совпадают по величине. Эти импульсы поступают на шину 3 устройства через элемент 8 - на счетный 5 вход делителя 4 и на вход сброса блока 2, устанавливая счетчик 14 в нулевое состояние. Таким образом, система, состоящая из счетчика 1, делителя 4, формирователя 9, представляет собой замкнутый контур автоматического регулирования частоты на 0 шине 3 (под воздействием входных импульсов, поступающихуна первый вход формирователя 9).

Если на второй вход формирователя 9 поступают подряд три импульса с выхода делителя 4, между которыми не прошел ни один из входных импульсов, то на третьем выходе формирователя 9 появляется импульс, поступающий на второй вход блока 11 и действующий аналогично ИНУ, переводя блок и весь умножитель частоты р импульсов в исходное состояние. Кроме того, формирователь 9 по принципу действия является двухступенчатым. На его первый вход 25 поступают импульсы входной умножаемой частоты Fax. По переднему фронту каждого импульса FBX триггеры 18 и 19 ус- 5 танавливаются в ноль, а по заднему фронту этого импульса триггер 20 устанавливается в единицу. Если до прихода следующего импульса FBX на вход 27 не поступит очередной импульс с выхода делителя 4, то этот второй импульс FBX через откры- 0 тый элемент 21 и последовательно с ним соединенный элемент 22 проходит на второй выход 29 формирователя 9 и поступает на счетный вход счетчика 1, уменьшая его содержимое на единицу, поскольку в этот момент на выходе 26 формирователя 9 5 имеет место нулевой уровень, обеспечивающий на управляющем входе счетчика 1 режим вычитания.

Если на вход 27 формирователя 9 поступают подряд два импульса с выхода де- 0 лителя 4, между которыми не прошел ни один импульс входной умножаемой частоты FBX, то аналогично описанному выше первый из них своим передним фронтом устанавливает в «О триггер 20, а своим задним фронтом переводит триггер 18 в «1. 5 Второй импульс делителя 4 через последовательно соединенные элементы 23 и 22 проходит на выход 29 формирователя 9, увеличивая на единицу содержимое счетчика 1, поскольку на выходе 26 формирователя 9 в этот момент имеет место единичный уровень, обеспечивающий работу счетчика 1 в режиме суммирования. При этом этот второй импульс с выхода делителя 4 своим задним фронтом устанавливает в «1 триггер 19.

Если к моменту прихода на вход 27 третьего импульса с выхода делителя 4 на

Рвхмакс . При этом частота появления фазовых флуктуации на выходе предлагаемого умножителя при максимальной входной частоте в ЗК раз меньше по сравнению с прототипом и при минимальной входной частоте - в К раз меньше.

Формула изобретения 1. Умножитель частоты импульсов, со15

вход 25 формирователя 9 по-прежнему не 10 держащий реверсивный счетчик импульсов,

придет ни один импульс входной частоты

FBX, то этот третий импульс проходит на

выход 29 формирователя 9 и, кроме того,

через элемент 24 (в режиме умножения)

проходит на выход 30 формирователя 9,

приводя блок 11 в исходное состояние,

аналогично ИНУ. Таким образом, наличие

импульса на выходе 29 формирователя 9

есть признак того, что

1дел 2гвх.

Этот признак в устройстве используется JQ как сигнал окончания пачки входных импульсов FBX. На вход 28 подается единичный уровень с выхода блока 11 в режиме измерения периода умножаемой частоты FBX и нулевой уровень в режиме умножения частоты. Единичный уровень удержи- 25 вает в единичном состоянии триггер 18 формирователя 9 в режиме измерения периода входной частоты Рвх, обеспечивая на первом выходе 26 формирователя 9 единичный уровень и закрывая по одному из входов элемент 24. Таким образом, импульсы с выхода делителя 4 в режиме измерения проходят с входа 27 через элемент 23 и элемент 22 на выход 29 формирователя 9 и далее на счетный вход счетчика 1, на управляющем входе которого при этом имеет место единичный уровень, обеспечиваюший 35 режим суммирования. По приходе второго входного импульса Рвх режим измерения заканчивается, триггер 19 устанавливается в нулевое состояние, а на входе 28 формирователя 9 устанавливается нулевой уровень. Q

В режиме умножения формирователь разностной частоты работает аналогично описанному выше.

Рассмотрение работы формирователя 9 показывает, что его выход 29 - это выход сигналов разностной частоты -Вдел - - Рвх; его выход 26 - это выход знака этой разностной частоты. Действительно, если дел - Рвх О, то на выходе 26 имеет место единичный уровень. Наоборот, если Гдел - Рвх ; о, то на выходе 26 имеет место нулевой уровень. Наконец, если дел 2Рвх, то на его выходе 30 появляется выходной сигнал, несущий в себе этот признак.

Таким образом, умножитель частоты импульсов обеспечивает устойчивую работу в диапазоне умножаемых частот, ограниченвыходы которого поразрядно соединены с кодовым входом счетного блока, выход которого соединен, с выходной длиной, делитель частоты, генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, и щину умножаемой частоты, отличающийся тем, что, с целью повышения точности, в него введены шина начальной установки, второй элемент И, блок управления и формирователь разностной частоты, первый вход которого соединен с шиной умножаемой частоты и с первым входом блока управления, второй вход - с выходом делителя частоты, вход сброса которого соединен с входом сброса реверсивного счетчика импульсов и с первым выходом блока управления, счетный вход - с выходом элемента ИЛИ, второй вход которого подключен к выходной шине, и с входом сброса счетного блока, счетный вход которого соединен с выходом второго эле- мента И, первый вход которого соединен с выходом генератора импульсов, второй - с вторым выходом блока управления, третий выход которого соединен с вторым входом первого элемента И, четвертый выход - с третьим входом формирователя разностной частоты, первый и второй выходы которого соединены соответственно с управляющим и счетным входами реверсивного счетчика импульсов, третий выход - с вторым входом блока управления, третий вход которого соединен с шиной начальной установки. 2. Умножитель по п. 1, отличающийся тем, что формирователь разностной частоты содержит два инвертора, три триггера, три элемента И-НЕ и элемент ИЛИ- НЕ, причем первый вход формирователя разностной частоты соединен с первым входом первого элемента И-НЕ, с R-входами первого и второго триггеров и через первый инвертор с С-входом третьего триггера, прямой выход которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом третьего элемента И- НЕ, с С-входом второго триггера и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом второго триггера, D-вход которого соединен с первым выходом формирователя разностной частоты, с прямым выходом первого

45

50

55

ном внизу величиной Рвхмин и сверху

Рвхмакс . При этом частота появления фазовых флуктуации на выходе предлагаемого умножителя при максимальной входной частоте в ЗК раз меньше по сравнению с прототипом и при минимальной входной частоте - в К раз меньше.

Формула изобретения 1. Умножитель частоты импульсов, со держащий реверсивный счетчик импульсов,

5

Q 5 5 Q

выходы которого поразрядно соединены с кодовым входом счетного блока, выход которого соединен, с выходной длиной, делитель частоты, генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, и щину умножаемой частоты, отличающийся тем, что, с целью повышения точности, в него введены шина начальной установки, второй элемент И, блок управления и формирователь разностной частоты, первый вход которого соединен с шиной умножаемой частоты и с первым входом блока управления, второй вход - с выходом делителя частоты, вход сброса которого соединен с входом сброса реверсивного счетчика импульсов и с первым выходом блока управления, счетный вход - с выходом элемента ИЛИ, второй вход которого подключен к выходной шине, и с входом сброса счетного блока, счетный вход которого соединен с выходом второго эле- мента И, первый вход которого соединен с выходом генератора импульсов, второй - с вторым выходом блока управления, третий выход которого соединен с вторым входом первого элемента И, четвертый выход - с третьим входом формирователя разностной частоты, первый и второй выходы которого соединены соответственно с управляющим и счетным входами реверсивного счетчика импульсов, третий выход - с вторым входом блока управления, третий вход которого соединен с шиной начальной установки. 2. Умножитель по п. 1, отличающийся тем, что формирователь разностной частоты содержит два инвертора, три триггера, три элемента И-НЕ и элемент ИЛИ- НЕ, причем первый вход формирователя разностной частоты соединен с первым входом первого элемента И-НЕ, с R-входами первого и второго триггеров и через первый инвертор с С-входом третьего триггера, прямой выход которого соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом третьего элемента И- НЕ, с С-входом второго триггера и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом второго триггера, D-вход которого соединен с первым выходом формирователя разностной частоты, с прямым выходом первого

5

0

5

триггера и с первым входом третьего элемента И-НЕ, второй вход которого соединен с вторым входом формирователя разностной частоты, с R-входом третьего триггера и через второй инвертор с С-входом первого триггера, инверсный выход которого соединен с О-входом третьего триггера, инверсный выход которого соединен с Dвходом первого триггера, S-вход которого соединен с третьим входом формирователя разностной частоты и с третьим входом элемента ИЛИ-НЕ, при этом второй и третий выходы формирователя разностной частоты соединены с выходами соответственно второго элемента И-НЕ и элемента ИЛИ- НЕ.

25

(pus.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Устройство для умножения частоты | 1991 |

|

SU1797115A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1081783A1 |

| Умножитель частоты | 1988 |

|

SU1626315A1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1140220A1 |

| Умножитель частоты периодических импульсов | 1983 |

|

SU1108610A1 |

| Умножитель частоты следования импульсов | 1990 |

|

SU1758860A2 |

| Цифровой умножитель частоты | 1987 |

|

SU1596444A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1173537A1 |

Изобретение относится к импульсной технике. Может быть использовано в устройствах автоматики и измерительной техники. Цель изобретения - повышение точности измерений :- достигается введением в умножитель второго логического элемента (ЛЭ) И 7, формирователя разностной частоты 9, блока управления 11 и шины 12 начальной установки. Кроме того, умножитель содержит реверсивный счетчик 1, счетный блок 2, шины - выходную 3 и умножаемой частоты 10, делитель частоты 4, генератор импульсов 5, первый ЛЭ И 6, ЛЭ ИЛИ 8. В счетный блок 2 входят элемент 13 сравнения кодов, счетчик импульсов 14 и формирователь импульсов 15. Состав формирователя разностной частоты 9 и блока управления 11 показан на функциональных схемах, приведенных в описании изобретения. Данный умножитель частоты устойчиво работает в диапазоне умножаемых частот, ограниченном снизу величиной Рвхмин- fni/K и сверху Fex.Mat«; fm/3K, где f ги - частота импульсов генератора 5; К - коэффициент деления делителя 4. Частота появления фазовых флуктуации на выходе умножителя при максимальной входной частоте в ЗК раз меньше, по сравнению с прототипом и при минимальной входной частоте - в К раз меньше. 1 з.п. ф-лы, 3 ил. ю (Л Ю 00 00 Ю 1C Ю

| Умножитель частоты | 1980 |

|

SU944097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Трехфазный регулируемый индуктивноемкостный преобразователь | 1976 |

|

SU615469A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-15—Публикация

1984-06-26—Подача