VI VI

СЛ

00

4 О

Изобретение относится к измерительной технике и может быть использовано при обработке информации, представляемой в виде периодических частотно-импульсных последовательностей.

Известен умножитель частоты, содержащий элемент И, одновибратор, два триггера, реверсивный счетчик и блок задания коэффициента умножителя. Недостатком его является отсутствие линейной зависи- мости периода выходных импульсов от входных.

Известно устройство умножения частоты следования периодических импульсов, содержащее делитель опорной частоты, клапан, счетчик импульсов поделенной опорной частоты, входного формирователя, блока управления, запоминающего регистра, счетчика импульсов, триггера, сравнива- ющего устройства, выходного формирователя и дополнительного сравнивающего устройства. Недостатком устройства является невозможность его использования при заранее неизвестной частоте сигнала.

Наиболее близким по техническому решению является умножитель частоты, содержащий два делителя частоты, счетчик, реверсивный счетчик, блок сравнения, два триггера, три элемента ИЛИ, три элемента И Недостатком данного устройства является низкое быстродействие, обуславливающее линейное умножение входной частоты лишь по истечению нескольких периодов входной частоты. Другим недостатком уст- ройства является возможность появления выходных импульсов с неравномерным временным дрейфом в процессе настройки.

Целью изобретения является повышение быстродействия. По сравнению с прото- типом, у которого работа реверсивного счетчика происходит в режимах суммирования и вычитания на одной опорной частоте, используется в предложенном устройстве работа реверсивного счетчика в разных ча- стотах, что позволяет в течение одного периода входной частоты Те определить половину периода выходной частоты и в следующие два периода Те воспроизводить выходную частоту на выходе умножителя частоты, что позволяет являться существенным отличием данного умножителя частоты. Быстродействие устройства повышено по сравнениюс прототипом, т.к. время определения выходной частоты не может превы- шать одного периода входного сигнала.

Данное устройство может быть выполнено на цифровых элементах, в виде микросхемы и не нуждается в настройке.

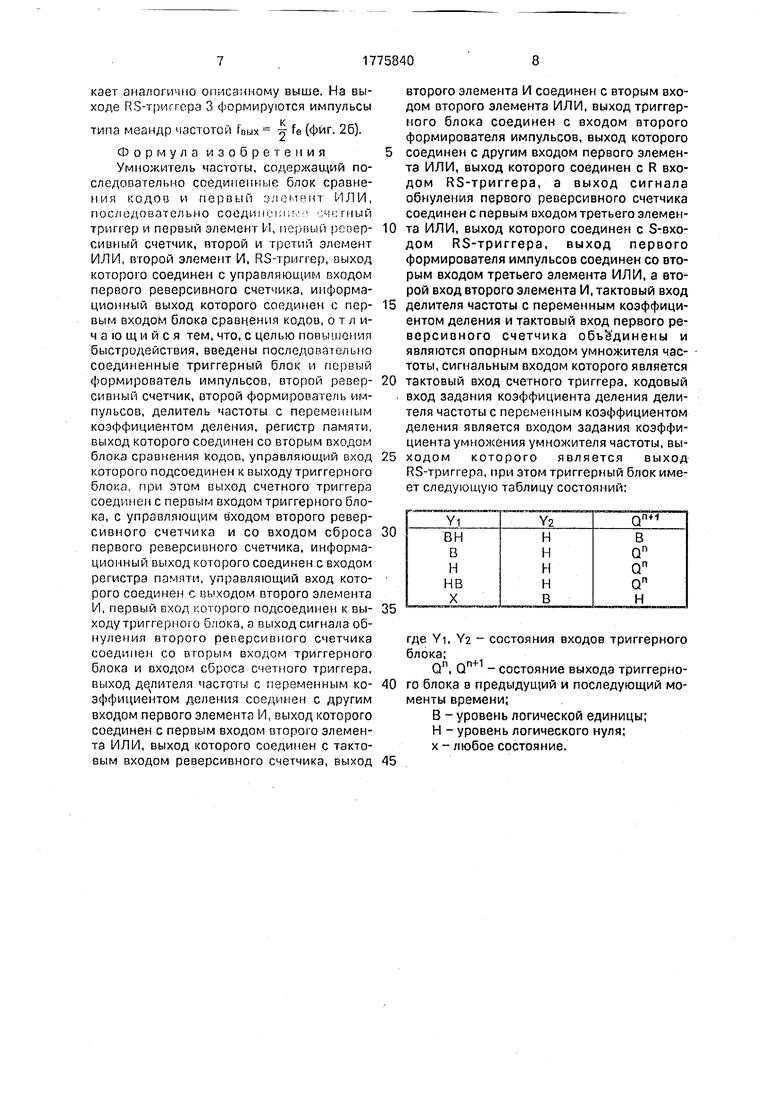

Поставленная цель достигается тем, что используется умножитель, содержащий последовательно соединенные блок сравнения кодов и первый элемент ИЛИ, последовательно соединенные счетный триггер и первый элемент И, первый реверсивный счетчик, второй и третий элементы ИЛИ, второй элемент И, RS-триггер, выход которого соединен с управляющим входом первого реверсивного счетчика, информационный выход которого соединен с первым входом блока сравнения кодов, отличающийся тем, что, с целью повышения быстродействия, введены последовательно соединенные триггерный блок и первый формирователь импульсов, второй реверсивный счетчик, второй формирователь импульсов, делитель частоты с переменным коэффициентом деления, регистр памяти, выход которого соединен со вторым входом блока сравнения кодов, управляющий вход которого подсоединен к выходу триггерного блока, при этом выход счетного триггера соединен с первым входом триггерного блока, с управляющим входом второго реверсивного счетчика и со входом сброса первого реверсивного счетчика, информационный выход которого соединен со входом регистра памяти, управляющий вход которого соединен с выходом второго элемента И, первый вход которого подсоединен к выходу триггерного блока, а выход сигнала обнуления второго реверсивного счетчика соединен со вторым входом триггерного блока и входом сброса счетного триггера, выход делителя частоты с переменным коэффициентом деления соединен с другим входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом реверсивного счетчика, выход второго элемента И соединен со вторым входом второго элемента ИЛИ, выход триггерного блока соединен со входом второго формирователя импульсов, выход которого соединен с другим входом первого элемента ИЛИ, выход которого соединен с R-входом RS-тригера, а выход сигнала обнуления первого реверсивного счетчика соединен с первым входом третьего элемента ИЛИ, выход которого соединен с 5-входом RS-триггера, а выход первого формирователя импульсов соединен со вторым входом третьего элемента ИЛИ, а второй вход второго элемента И, тактовый вход делителя частоты с переменным коэффициентом деления и тактовый вход первого реверсивного счетчика объединены и являются опорным входом умножителя частоты, сигнальным входом которого является тактовый вход счетного триггера, кодовый вход задания коэффициента деления делителя частоты с переменным коэффициентом деления является входом задания коэффициента умножения умножителя частоты, выходом которого является выход RS-триг- гера, при этом триггерный блок имеет следующую таблицу состояний:

0

ние с уровнем логической 1 на выходе триггерный блок 2, разрешая прохождение импульсов частотой f0n через элемент И 9 и элемент ИЛИ 8 на тактовый вход реверсивного счетчика 4, который теперь работает в режиме вычитания, т.к. на его управляющий вход поступает уровень логического О с выхода счетного триггера 1. За счет того, что запись в реверсивный,счетчик 4 идет с частотой

-, а считывание происходит с часК.

оп

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Устройство для измерения внутреннего угла синхронной машины | 1984 |

|

SU1226331A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| Способ контроля состояния кромки режущего инструмента и устройство для его осуществления | 1990 |

|

SU1763890A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Формирователь импульсов с регулируемой частотой следования | 1990 |

|

SU1780186A1 |

| Устройство для определения первой разности частотно-импульсного сигнала | 1982 |

|

SU1043675A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

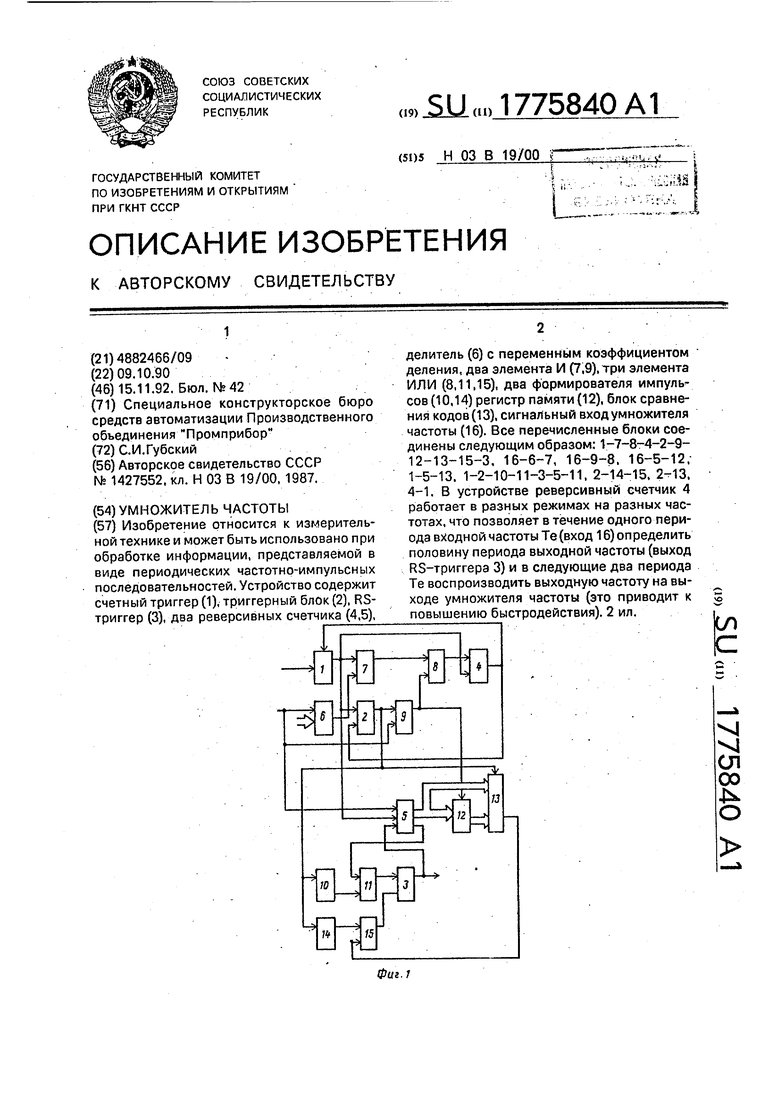

Изобретение относится к измерительной технике и может быть использовано при обработке информации, представляемой в виде периодических частотно-импульсных последовательностей. Устройство содержит счетный триггер (1), триггерный блок (2), RS- триггер (3), два реверсивных счетчика (4,5), делитель (б) с переменным коэффициентом деления, два элемента И (7,9), три элемента ИЛИ (8,11,15), два формирователя импульсов (10,14) регистр памяти (12), блок сравнения кодов (13), сигнальный вход умножителя частоты (16). Все перечисленные блоки соединены следующим образом: 1-7-8-4-2-9- 12-13-15-3, 16-6-7, 16-9-8. 16-5-12. 1-5-13. 1-2-10-11-3-5-11, 2-14-15, 2-13. 4-1. В устройстве реверсивный счетчик 4 работает в разных режимах на разных частотах, что позволяет в течение одного периода входной частоты Те (вход 16) определить половину периода выходной частоты (выход RS-триггера З) и в следующие два периода Те воспроизводить выходную частоту на выходе умножителя частоты (это приводит к повышению быстродействия). 2 ил. ./ v fe

где YI - Y2 - состояние входов триггерного блока

Qn - Qn+1 - состояние выхода триггерного блока в предыдущий и последующий момент времени

В - уровень логической 1

Н - уровень логического О

х - любое состояние

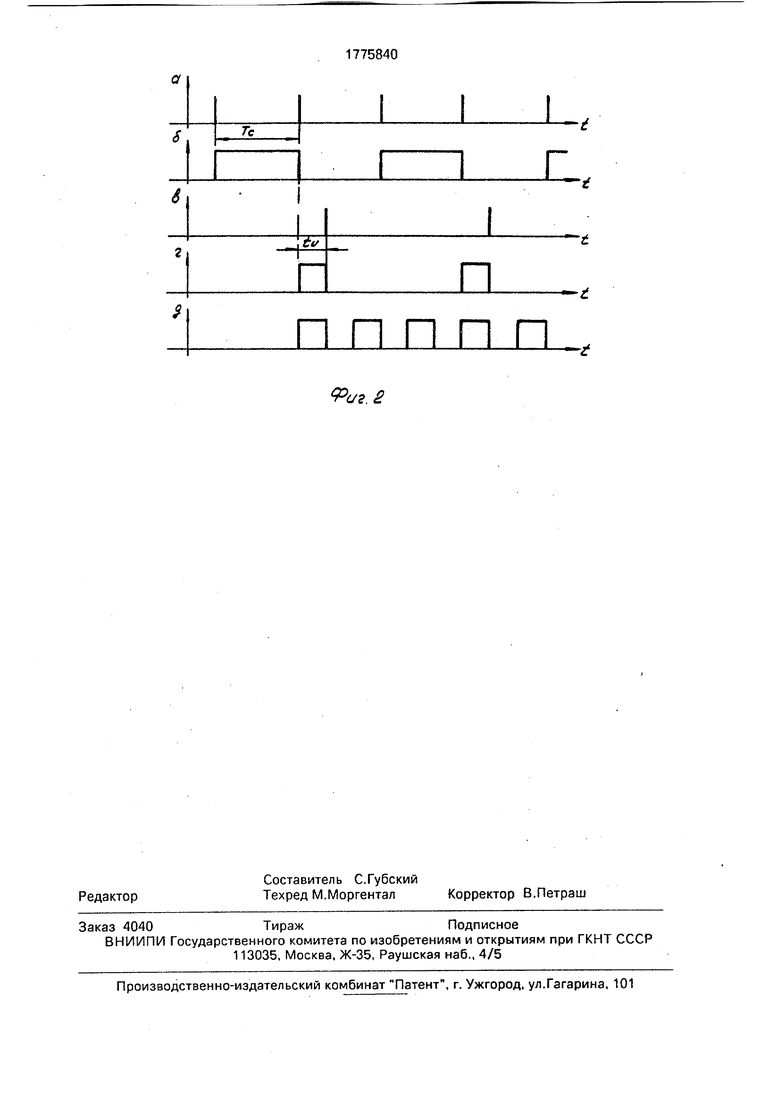

На фиг. 1 представлена структурная схема умножителя частоты; на фиг. 2 -диаграммы, поясняющие его работу,

Устройство-умножитель частоты, содержит счетный триггер 1, триггерный блок 2, RS-триггер З, реверсивные счетчики 4, 5, делитель частоты с переменным коэффициентом деления 6, элемент И 7, элемент ИЛИ 8, элемент И 9, формирователь импульсов 10, элемент ИЛИ 11, регистр памяти 12, блок сравнения кодов 13, формирователь импульсов 14, элемент ИЛИ 15.

По включению питания счетный триггер 1, триггерный блок 2, RS-триггер З устанавливаются в состояние с уровнем логического О на выходах, в реверсивных счетчиках 4,5 устанавливается код числа N 0, а коэффициент делителя частоты 6 равен К.

Импульсы входной частоты с периодом Те поступают на вход счетного триггера 1 (фиг. 2а), а с его выхода импульсы длительностью т.и Те поступают на вход элемента И7 (фиг. 26), разрешая прохождение частоты опорных импульсов с выхода делителя

частоты 6

-22-(при условии, что на тактовый

К

вход делителя частоты 6 поступает опорная частота f0n) на тактовый вход реверсивного счетчика 4 через элемент ИЛИ 8, при этом на управляющий вход реверсивного счетчи- ка4 поступаетуровень логической 1, обуславливающий режим суммирования. По спаду импульса с выхода счетного триггера 1 устанавливается в нулевое состояние реверсивный счетчик 5 и переходит в состоя

тотой f0n, на выходе обнуления счетчика 4 появляется импульс, отдаленный от заднего фронта импульса на выходе счетного триггеТера 1 на время т.и --(фиг. 2в). Этим импуль14

сом устанавливается в исходное, нулевое, состояние счетный триггер 1 и триггерный блок 2, который блокирует прохождение опорной частоты на тактовый вход реверсивного счетчика 4, при этом на выходе триггерного блока 2 формируется импульс

длительностью т,и

Те

- (фиг. 2г). По переднеК

5

0

5

0

5

5

му фронту этого импульса формирователь импульсов 10 формирует короткий импульс, проходящий через элемент ИЛИ 11 на установочный вход S RS-триггера З, при этом RS-триггер З устанавливается в состояние с уровнем 1 на выходе, который поступает на управляющий вход реверсивного счетчика 5, обуславливая режим суммирования счетчика. За время импульса т.и в реверсивный счетчик 5 запишется код NK, причем каждое изменение состояния реверсивного счетчика 5 записывается в регистр памяти 12, но работа блока сравнения кодов блокируется импульсом т,и, поступившим на управляющий вход блока сравнения кодов 13 с выхода триггерного блока 2. По заднему фронту импульса т,и формирователь импульсов 14 формирует короткий импульс, прохо- дящмй через элемент ИЛИ 15 на установочный вход R RS-триггера З, изменяя его состояние, уровень логического О на его выходе обуславливает режим вычитания реверсивного счетчика 5. Импульс сигнала обнуления с выхода реверсивного счетчика 5 поступает через элемент ИЛИ 11 на установочный вход S RS-триггера З, изменяя его состояния на единичное, снова обуславливая режим суммирования реверсивного счетчика 5. При достижении на информационном выходе реверсивного счетчика 5 кода М« на выходе блока сравнения кодов 13 появляется импульс, проходящий через элемент ИЛИ 15 на установочный вход R RS-триггерз З, изменяя его состояние на нулевое. Далее процесс изменения состояния RS-триггера З протекает аналогично описанному выше. На выходе RS-триггера З формируются импульсы

V

типа меандр частотой tBux - к fe (фиг. 26).

Фор мула изобретения

Умножитель частоты, содержащий последовательно соединенные блок сравнения кодов и первый элемент ИЛИ, последовательно соединим;. .четный триггер и первый элемент И, первый репер- сивный счетчик, второй и третий элемент ИЛИ, второй элемент И, RS-триггер, выход которого соединен с управляющим входом первого реверсивного счетчика, информационный выход которого соединен с пер- вым входом блока сравнения кодов, отличающийся тем, что, с целью повышения быстродействия, введены последовательно соединенные триггерный блок и первый формирователь импульсов, второй ревер- сивный счетчик, второй формирователь импульсов, делитель частоты с переменным коэффициентом деления, регистр памяти, выход которого соединен со вторым входом блока сравнения кодов, управляющий вход которого подсоединен к выходу триггерного блока, при этом выход счетного триггера соединен с первым входом триггерного блока, с управляющим входом второго реверсивного счетчика и со входом сброса первого реверсивного счетчика, информационный выход которого соединен с входом регистра памяти, управляющий вход кото- рого соединен с выходом второго элемента И, первый вход которого подсоединен к вы- ходутриггерною блока, а выход сигнала обнуления второго рег.ерсивпого счетчика соединен со вторым входом триггерного блока и входом сброса счетного триггера, выход делителя частоты с переменным ко- эффициентом деления соединен с другим входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом реверсивного счетчика, выход

второго элемента И соединен с вторым входом второго элемента ИЛИ, выход триггер- пого блока соединен с входом второго формирователя импульсов, выход которого соединен с другим входом первого элемента ИЛИ, выход которого соединен с R входом RS-триггера, а выход сигнала обнуления первого реверсивного счетчика соединен с первым входом третьего элемента ИЛИ, выход которого соединен с S-вхо- дом RS-триггера, выход первого формирователя импульсов соединен со вторым входом третьего элемента ИЛИ, а второй вход второго элемента И, тактовый вход делителя частоты с переменным коэффициентом деления и тактовый вход первого ре- версивного счетчика объединены и являются опорным входом умножителя частоты, сигнальным входом которого является тактовый вход счетного триггера, кодовый вход задания коэффициента деления делителя частоты с переменным коэффициентом деления является входом задания коэффициента умножения умножителя частоты, выходом которого является выход RS-триггера, при этом триггерный блок имеет следующую таблицу состояний:

где Yi, YZ - состояния входов триггерного блока;

Qn, Qn+1 - состояние выхода триггерного блока в предыдущий и последующий моменты времени;

В - уровень логической единицы;

Н - уровень логического нуля;

х - любое состояние.

Фиг.ё

| Умножитель частоты | 1987 |

|

SU1427552A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-15—Публикация

1990-10-09—Подача