3.Регулятор no п. t, о т л ич а ю щ и и с я тем, что блок програымирозааия содержит подключенныек первому входу программного запоминающего элемента первый переключакпда элемент, к второму входу - через второй элемент И второй переключакщнй элемент, причем второй вход второго элемента И, соединениьй с третьим .входом программного эапоминакщего элемента, является входом блока програ1фшрования, а выходы программного .эапоминакщего элемента - выходами блока программирования.

4.Регулятор по п. 1, отличающийся тем, что блок Сравнения содержит включенные последовательно третий элемент И, первый элемент НЕ, четвертый элемент И, элемент ИЛИ, выход которого является первьм выходом блока сравнения,

и пятый элемент И, а также подключенный к второму входу элемента ИЛИ шестой элемент И, к первому входу которого подключены выходами второй элемент НЕ и седьмой элемент И, к второму входу - третий элемент НЕ, а к третьему - выход третьего элемента И, седьмой и восьмой элементы И, первыми входами подключенные к первому входу блока сравнения, соединенному с первыми входами третьего элемента И, вторыми входами соединенные с вторым входом блока сравнения, причём выход шестого элемента И связан с входом третьего элемента НЕ и вторым входом четвертого элемента И, третьим входом соединенного с выходом второго элемента НЕ, первый выход седьмого элемента И связан с вторым входом пятого элемента И, выход которого является вторым выходом блока сравнения, а второй выход седьмого элемента И связан с первьв4 входом шестого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограммный регулятор температуры | 1983 |

|

SU1136123A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Многоканальный регулятор тепловых процессов | 1981 |

|

SU1013922A2 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Многоканальный широтно-импульсный регулятор температуры (его варианты) | 1981 |

|

SU962883A1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Многоканальный широтно-импульсный регулятор температуры (его варианты) | 1981 |

|

SU978111A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Г. МНОГОПРОГРАММНЫЙ РЕГУЛЯТОР ТЕМПЕРАТУРЫ, содержащий дат чики температуры и исполнительные элементы по числу ка 1алов, подключенные к соответствующим информационным входам и управляющим выходам обегающего блока, подключенные к первому, и второму выходам блока адресации, и соединенные последовательно блок памяти, коммутатор, первый блок буферной памяти и сумма-г тор, выходом подключенный к второму входу блока памяти, связанные с выходом блока памяти, и соединенные последовательно селектор уровня и блок управления, первым выходом соединенный с вторым входом коммутатора, вторым - с третьим входом коммутатора, а третьим выходом - с первым управляющим входом обегающего . блока, вторым управляющим входом соединенного через блок сравнения с первым выходом блока программирования и таймером, причем второй выход блока программирования связан с вторым входом сумматора, третий - с вторым входом- селектора уровня, четвертый - с вторым входом блока управления, третьим входом подключенного к адресному выходу обегающего блока, блок адресации первым и вторьа4 выходами соединен с тактовым входом обегающего блока, третьим выходом соединен с третьим входом блока памяти четвертым выходом - с вторю4 входом первого блока буферной памяти и стробирукнцим входом обегаюцего блока, отличающийся тем, что, с целью расширения области применения регулятора, он содержит подключеннь первьм входом к перво(Л му и второму выходам блока адресации второй блок буферной памяти, выходом подключенный к входу блока программирования, вторым входом подключенный к пятому выходу блока адресации, а третьим - к выходу блока сравнения. 2. Регулятор по п. 1, о т л ича ющи и.с я -тем, что блок адре00 сации содержит последовательно соеди ненные генератор, первый и второй ;о ел счетчики, триггер, третий счетчик, делитель, элемент И и элемент задержки, а также подключенный к второму выходу первого счетчика дешифратор, выходом соединенный с вторым входом элемента И, и одновибратор, подключенный к выходу триггера и третьему входу элемента И, причем второй выход третьего счетчика является первым .второй выход второго счетчика - вторым, выход элемента задержки - третьик выход дешифратора-четвертым, а выход одновибратора - пятым выходами блока адресации.

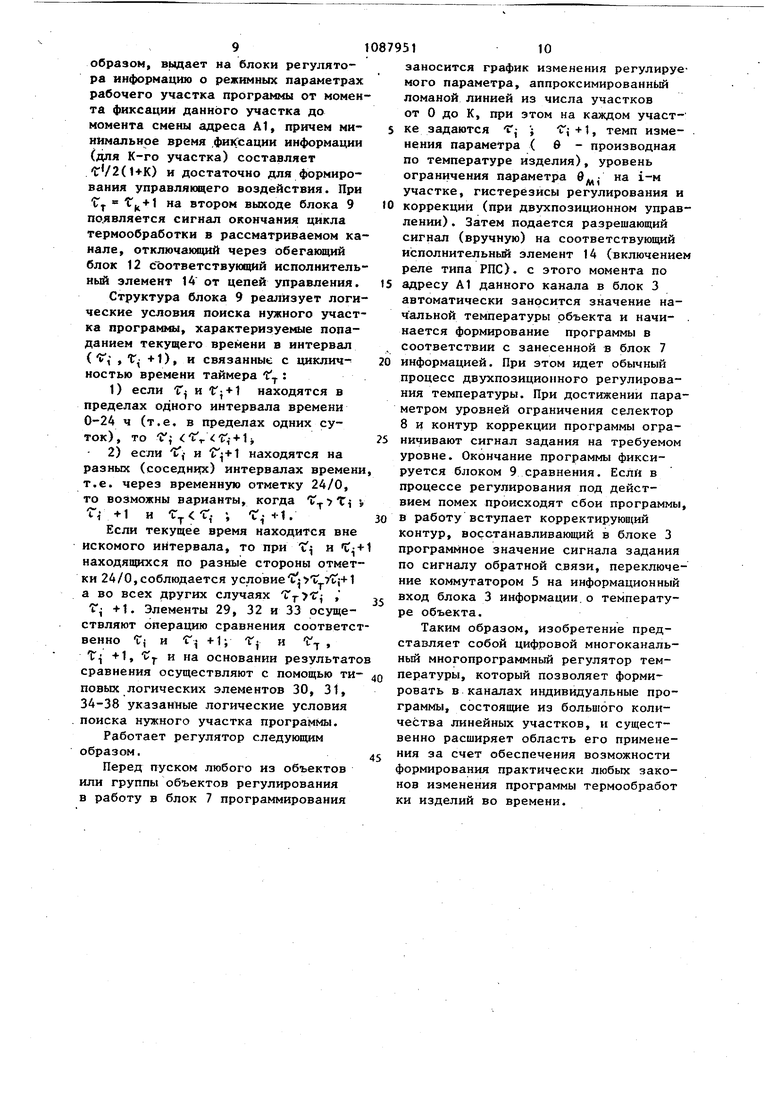

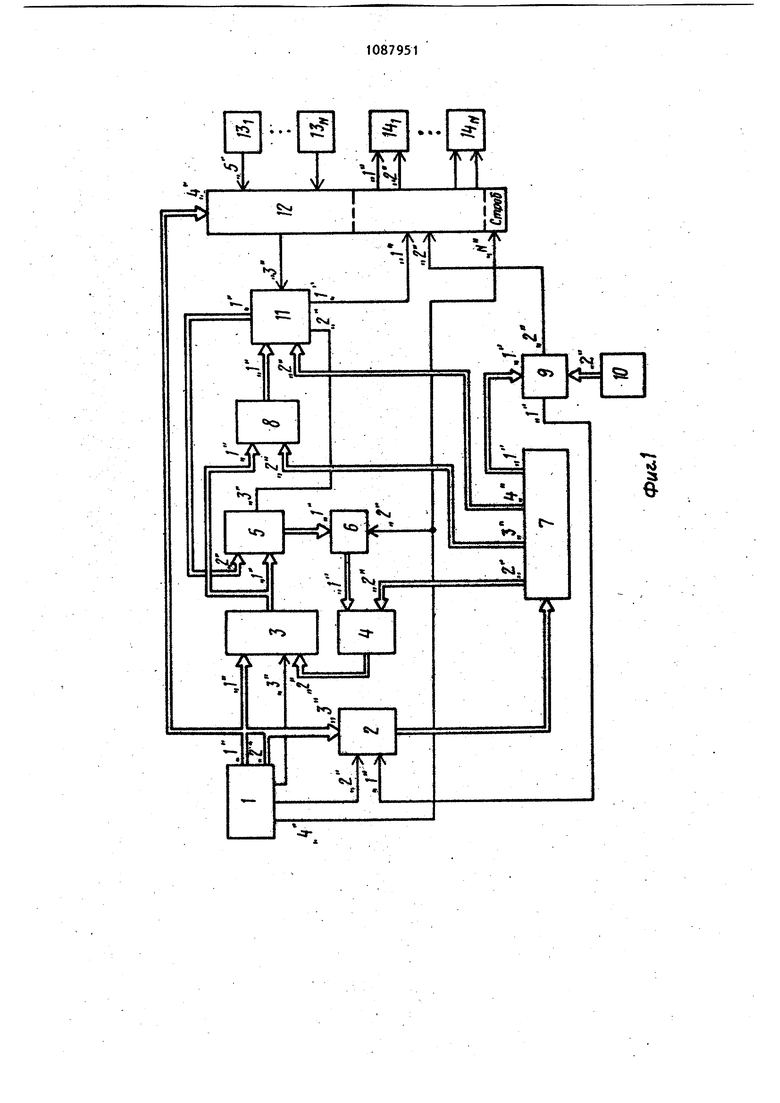

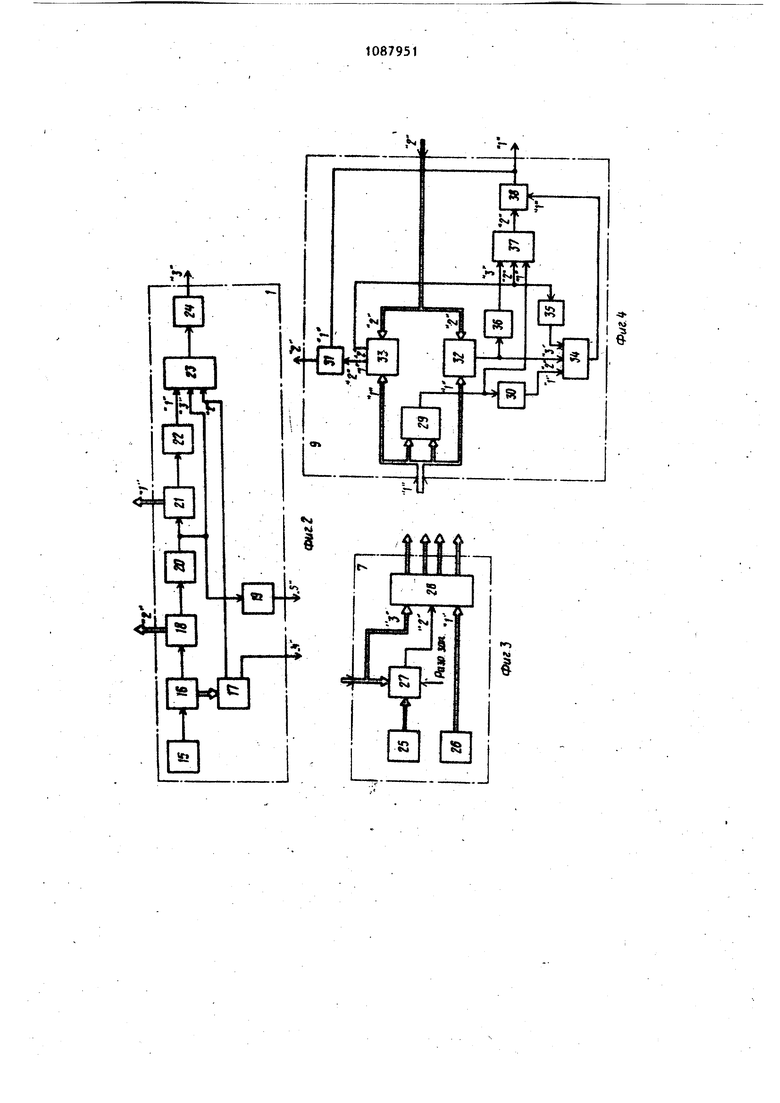

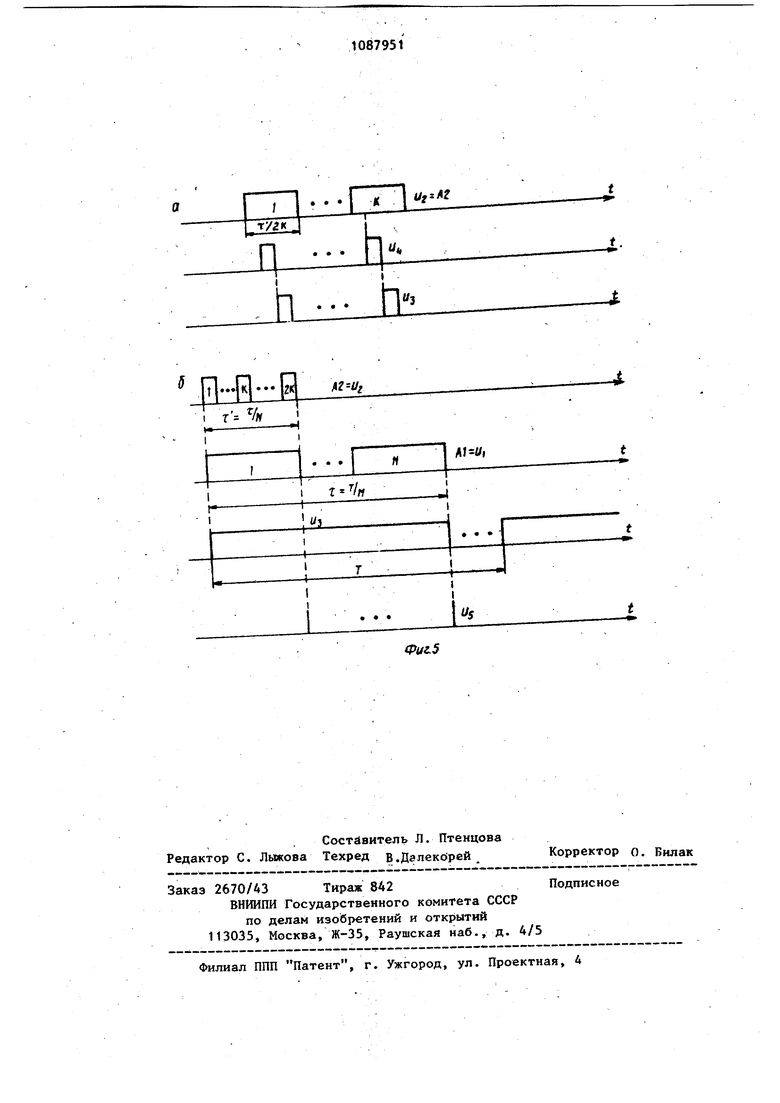

Изобретение относится к автоматическому регулированию технологических процессов и может быть использовано для программного регулирования процессов термообработки из делий в группе технологических установок. Известно устройство для многоПрограммного регулирования температуры, содержащее генератор, термодатчики и задатчики по числу канало термообработки, корректир отщй блок блок пересчета периода импульсов, обегающий блок и исполнительные органы, блок управления и усилитель f Однако это устройство имеет ограниченные возможности программирования и низкую точность задания программ, для формирования которых используются индивидуальные блоки триггерных ячеек. Наиболее близким к изобретению по технической сущности является мн гоканальный регулятор температуры. содержащий последовательно соединен ные блок адресации, запоминаняцее устройство, селектор, блок управления, обегакхций блок, выходы которого подключены к исполнительньм органам и третьему входу блока управления, ё входы - к первому и пятому выходу блока управления, связанному также с вторым входом блока буферной памяти, к выходам термодатчиков и второму выходу блока сравнения, коммутатор, входами соединенный с двумя выходами блока управления и с выходом запоминающего устройства, а выходом через последовательно соединенные блок буферной памяти и сумматор - с первым входом запоминакш его устройства, блок программирования, связанный с первыми входами сумматора, селектора, блока управления и блока сравнения, и к второму входу обегающего блока, подключенного к таймеру. Блок адресации состоит из генератора, счетчика, элемента И. Блок программирования содержит блок переключателей и перепрограммируемое запоминакмцее устройство С2 , В ряде практических случаев требуется формирование сложных законов программного управления, аппроксимируемых кусочно-линейной функцией. из К-участков. Однако известное устройство может реализовать програм му, состоящую только из трех линейных участков программы, что ограничивает область его применения. Целью изобретения является расширение области применения регулятора. Поставленная цель достигается тем, что многопрограммньш регулятор температуры, содержащий датчики температуры и исполнительные эле менты по числу каналов, подключенные к соответствующим информационны входам и управляющим выходам обегаю щего блока, подключенные к первому и второму выходам блока адресации, и соединенные последовательно блок памяти, коммутатор, первый бло.К буферной памяти и сумматор, выходом подключенный к второму входу блока памяти, связанные с выхрдом блока п мяти, и соединенные последовательно селектор уровня и блок управления, первым выходом соединенный с вторым входом коммутатора, вторым - с третьи входом коммутатора, а третьим выходом - с первым управляющим входом обегающего блока, вторым управляющим входом соединенного через блок сравнения с первым выходом блока пр граммирования и таймером, причем вт рой выход блока программирования св зан с вторым входом сумматора, третий - с вторым входом селектора уровня, а четвертый - с вторым входом блока управления, третьим входо подключенного к адресному выходу обегающего блока, блок адресации пе вым и вторым выходами соединен с тактовым входом обегающего блока, третьим выходом соединен с третьим входом блока памяти, четвертым выходом - с вторым входом первого бло ка буферной памяти и стробирующим входом обегающего блока, содержит подключенньй первым входом к первом и второму выходам блока адресации второй блок буферной памяти, выходо подключенный к входу блока программирования, вторым входом подключенн к пятому выходу блока адресации, а третьим - к выходу блока сравнения. Блок адресации в нем содержит последовательно соединенные генератор, первый и второй счетчики, триггер, третий счетчик, делитель. лемент И и элемент задержки, а таке подключенный к второму выходу перого счетчика дешифратор, выходом оединенный с вторым входом элемента , и одновибратор, подключенный к ыходу триггера и третьему входу лемента И, причем второй выход ретьего счетчика является первым, второй выход второго счетчика - вторым,выход элемента задержки - третьим, ыход дешифратора - четвертым, а выод одновибратора - пятым выходами лока адресации. Блок программирования в нем содержит подключенные к первому входу программного запоминающего элемента первый переключающий элемент, к второму входу - через второй элемент И второй переключающий элемент, причем второй вход второго элемента И, соединенный с третьим входом программного запоминающего элемента, является входом блока программирования, а выходы программного запоминающего элемента - выходами блока программирования . Блок сравнения в нем содержит включенные последовательно третий элемент И, первый элемент НЕ, четвертый элемент И, элемент ИЛИ, выход которого является первым выходом блока сравнения, и пятый элемент И, а . также подключенный к второму входу элемента ИЛИ шестой элемент И, к первому входу которого подключены выходами второй элемент НЕ и седьмой элемент И, к второму входу третий элемент НЕ, а к третьему - выход третьего элемента И, седьмой и восьмой элементы И, первыми входами подключенные к пе рвому входу блока сравнения, соединенному с первыми входами третьего элемента И, вторыми входами соединен} ые с вторым входом блока сравнения, причем выход шестого элемента И связан с вторым входом третьего элемента НЕ и вторым входом четвертого элемента И, третьим входом соединенного с выходом второго элемента НЕ, первый выход седьмого элемента И связан с вторым входом пятого элемента И, выход которого является вторым выходом блока сравнения а второй выход седьмого элемента И связан с первым входом шестого элемента И. На фиг. 1 представлена структурная схема регулятора; на фиг. 2 структурная схема блока адр(сагг.ин; на фиг. 3 - структурная схема блока програмьшрования; на фиг. 4 - структурная схема блока сравнения; на фиг. 5 - временные диаграммы. Устройство содержит блок 1 адреса ции, второй 2 блок буферной памяти блок 3 памяти, сумматор 4, коммута.тор 5, первый-6 блок буферной памяти блок 7 программирования, селектор 8 Уровня, блок 9 сравнения, таймер 10 блок И управления, обегаюций блок 12, датчики 13 температуры, исполни.тельные э|1ементы 14, генератор 15, первьА счетчик; 16, дешифратор 17, второй счетчик 18, одновибратор 19, триггер 20, третий счетчик 21, делитель 22, элемент И 23, элемент задержки 24, переключаицне элементы 25 и 26, второй элемент И 27, про граммньА эапоминапорсй элемент 28, третий элемент И 29, первый элемент НЕ 30, пятый элемент 31, седьмой 32 и восьмой 33 элементы И, четвертый элемент И 34, второй 35 и третий 36 элементы НЕ, шестой элемент И 37 элемент ШШ 38. Блоки и узлы регулятора выполняют следующие функции. Блок 1 адресации (фиг. 2) формирует по временной диаграмме, представленной на фиг. 5; следующие сигналы на 1-5 выходах. 1)ядресиыА сигнал А1 (выход 1) снимаемый с разрядных выходов счетчюса 21, имеицего емкость N, равную числу каналов регулирования (этот сигнал служит для управления блоком 3, обегаквщм блоком 12 и блоком 7 программирования); 2)адресный сигнал А2 (выход 2 cнимae в Iй со счетчика 18 с емкостью К, равной максимальному числу участков програ в 1ы термообработки каждого канала (этот сигнал служит для управления считыванием информации с блока 7); ЗТ сигнал разрешения записи в блок 3, поступакмций с сумматора 4, (снимается с выхода последовательной цепочки, содержащей генератор 15, счетчики 16 и 18, триггер 20, счетчик 21, элемент И 23 и одновибратор 24, и формирует через каждый период Т LК-2 М, один цикл перезаписи по Н каналам, где L и М - емкости счетчика 16 и делителя 22); 4)импульс на сброс памяти блока 2 в начальный момент опроса каждого канала (выход 4); 5)стробирующий импульс на выходе 5 для записи информации в блок 6 и записи логического уровня управляннцего сигнала от блока 11, поступаницего через блок 12 в фиксаторы ну-, левого порядка исполнительных элементов 14. Сигнал стабильной частоты генератора 15 поступает на счетчик 16 с емкостью , разрядные выходы которого соединены с дешифратором 17. Когда в счетчике 16 записан код 2, дешифратор 17 В14цает импульс на выход 4, а при коде 2 - сигнал разрешения на формирование импульса по выходу 3 (пропущенные состояния счетчика 16 служат для устранения влияния переходных процессов, вызванных переключениями элементов, и для обеспеченця заданного алгоритма работы) , Счетчик 18 соединен с последним разрядом счетчика 16 и с триггером 20, который формирует паузу, необходимую для обеспечения считывания информации с блока 7 и блока 3 и ее переработки после выбора номера участка программы. При окончании в данном канапе полного цикла опроса всех каналов одновибратор 19 осуществляет сброс памяти блока 2. С помощью делителя 22 осущестпляется вырезка из сигнала длительностью Т импульса Т Т/М для форнирования сигнала разрешения записи. Блок 3 работает вкруговую в режиме построчной выборки по адресному сигналу, выдавая канальную информацию на выходные шины об уровне сигнала задания и вместе с коммутатором 5, блоком 6 и сумматором 4 образует многоканальный формирователь индивидуальных линейно изменякяцихся во времени программ термообработки изделий. Причем темп нагрева определяется значением приращения, подаваемого на вход 1 сумматора 4 и периодом следования импульсов разрешения записи информации, поступающей с выхода 3 блока 1 адресации. С приходом адресного сигнала на вход блока 3 канальная информация считывается, через коммуратор 5 подается в блок 6 и заносится в него по сигналу с выхода 5 блока 1 адресации, далее суммируется сумматором 4. с заданным значением приращения и, если при- сутствует сигнал разрешения записи на 2 входе блока 3, заносится в него вместо прежней информации по всем опрашиваемым каналам один раз в такт работы Т. Информационный сигнал с выхода блока 3 подается на вход селектора 8, пропускаю1це го на свой выход наименьший из входных сигналов, т.е. либо код сигнала от лока 3, либо код уровня изотермы от блока 7. Обеганяций блок 12 периодически-последовательно по адресному сигналу, определяющему номер канала, подключает выход 1 и вход 3 блока 11 управления соответственно к первому входу исполнительного элемента 14 и выходу датчика 13. В блоке It сигнал датчика 13 усиливается, преобразуется- в код, сравнивается с сигналом задания, поступающим с селектора 8, определяется разность сигнала задания и обратной связи (сигнал ошибки), которая далее сравнивается с заданными блоком 7 (вь1ход 3) значениями гистерезисов регулировани и коррекции. По результатам сравнени на выходе 1 формируется двухпозиционное регулирующее воздействие. Если сигнал ошибки превышает гистерезис коррекции, появляется сигнал на.выходе 2 блока 11, который коммутатором 5 подключает к блоку 6 буферной памяти вместо сигнал от блока 3 сигнал обратной связи (сигнал датчика 13) от блока 11 (выход 3) . При срабатывании корректирующего контура в блок 3 заносится код сигнала датчика вместо си нала задания. Такая коррекция восста навливает программу термообработки при сбоях, возникающих в результате действия производственных помех. Блок 7 программирования (фиг. 3) выдает занесенную в него информацию 1 - о температуре нагре на выходе ва ипи охлаждения Q, выходе об уровне ограничения температуры Q выходе 3 - о значениях гистерезис регулированиядрд и коррекции, на вы ходе А т о временных координатах, i-ro участка программы (Т , Р +1). Блок 7 состоит из декадного переклю чающего элемента 25 для установки номера программируемого канала и но мера участка канальной программы; декадного переключающего элемента 2 1 18 для задания значений записываемых параметров (темпа нагрева, уровня ограничения температуры, гистерезисы регулирования и коррекции, временные координаты tT,- , Т -f 1 начала и конца i-ro участка); элемента 27 и элемента 28, в качестве которого целесообразно использовать интегральные постоянные энергонезависимые ЗУ с электрическим перепрограммированием, например К558РР1 и т.п. Запись информации осуществляется следующим образом. Элементом 25 устанавливается номер программируемого канала, затем номер участка (начиная с первого), элементом 26 устанавливаются значения режимных параметров, и вручную кратковременно нажимается кнопка подачи сигнала разрешения записи на элемент 27.Заданная элементом 26 информация в момент совпадения кода адресов элемента 25 и кода адресных сигналов А1 и Л2 записывается в соответствующую ячейку элемента 28. При отсутствии сигнала разрешения записи элемент 28,управляясь адресными сигналами, выдает по каждому из адресов А1 А2 полную информацию о параметрах участках программы без,записи новой информации. Количество участков канальных программ ограничено емкостью памяти элемента 28 по адресу А2 и может легко наращиваться от 2-х до 64-х и более до значения 2. В качестве элементов 25 и 26 удобно использовать комплекты декадных (десятичных) переключателей с шифратором. При использовании однокоординатных элементов 28 адресные шины разделяются по усмотрению разработчика на две группы адресов А1 и А2 в соответствии с требуемым числом каналов и участков. Блок 9 сравнения по .значениям временных координат i-ro интервала (участка программы), снимаемых с выхода 4 блока 7 (f, - начало, - конец участка) , определяет попадает ли текущее время таймера в этот интервал. Последовательный опрос участков в каждом канале с 1-го по К-й осуществляется до момента попадания текущего времени в i-й интервал, когда сигнал выхода 1 блока 9, зафиксирует блоком 2 адресный сигнал А2 на входе блока 7 до моНента смены адресного сигнала А1. Блок 7 программирования, таким образом, выдает на блоки регулятора информацию о режимных параметрах рабочего участка программы от момен та фиксации данного участка до момента смены адреса А1, причем минимальное время .фиксации информации (для К-го участка) составляет и/2(1+К) и достаточно для формирования управляющего воздействия. При Т f + 1 на втором выходе блока 9 появляется сигнал окончания цикла термообработки в рассматриваемом ка нале, отключаюощй через обегающий блок 12 clJOTBeTCTByiomMA исполнитель ный элемент 14 от цепей управления. Структура блока 9 реализует логи ческие условия поиска нужного участ ка програм1«ы, характеризуемые попаданием текущего времени в интервал ( f,- , Т +1), и связанные с цикличностью времени таймера f : 1)если Т и находятся в пределах одного интервала времени 0-24 ч (т.е. в пределах одних суток), то f fr fi + U 2)если С,- и находятся на разных (соседних) интервалах времени т.е. через временную отметку 24/0, то возможны варианты, когда г,- +1. Если текущее время находится вне искомого интервала, то при ti и t + находящихся по разные стороны отметки 24/О,соблюдается условиеС Т 7С)+1 f. : а во всех других случаях уС Т +1. Элементы 29, 32 и 33 осуществляют операцию сравнения соответст Т,- 1; венно f +1,1 и на основании результато сравнения осуществляют с помощью типовых логических элементов 30, 31, 34-38 указанные логические условия . поиска нужного участка программьи Работает регулятор следующим образом. Перед пуском любого из объектов или группы объектов регулирования в работу в блок 7 программирования заносится график изменения регулируемого параметра, аппроксимированнь1й ломаной линией из числа участков от О до К, при зтом на каждом участке задаются Т, } ti , темп изме- . нения параметра (в - производная по температуре изделия), уровень ограничения параметра бд,,- на i-м участке, гистерезисы регулирования и коррекции (при двухпозиционном управлении) . Затем подается разрешающий сигнал (вручную) на соответствующий исполнительньй злемент 14 (включением реле типа РПС). с этого момента по адресу А1 данного канала в блок 3 автоматически заносится значение начальной температуры объекта и начи- . нается формирование программы в соответствии с занесенной в блок 7 информацией. При зтом идет обычный процесс двухпозиционного регулирования температуры. При достижении параметром уровней ограничения селектор 8 и контур коррекции программы ограничивают сигнал задания на требуемом уровне. Окончание программы фиксируется блоком 9 сравнения. Если в процессе регулирования под действием помех происходят сбои программы. в работу вступает корректирующий контур, восстанавливающий в блоке 3 программное значение сигнала задания по сигналу обратной связи, переключение коммутатором 5 на информационный вход блока 3 информации.о температуре объекта. Таким образом, изобретение представляет собой цифровой многоканальный многопрограммный регулятор температуры, который позволяет формировать в каналах индивидуальные программы, состоящие из большого количества линейных участков, и существенно расширяет область его применения за счет обеспечения возможности формирования практически любых законов изменения программы термообработ ки изделий во времени.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ПРОГРАММНОГО МНОГОКАНАЛЬНОГО АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ ТЕПЛОВЫХПРОЦЕССОВ | 0 |

|

SU334558A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-04-23—Публикация

1983-01-21—Подача