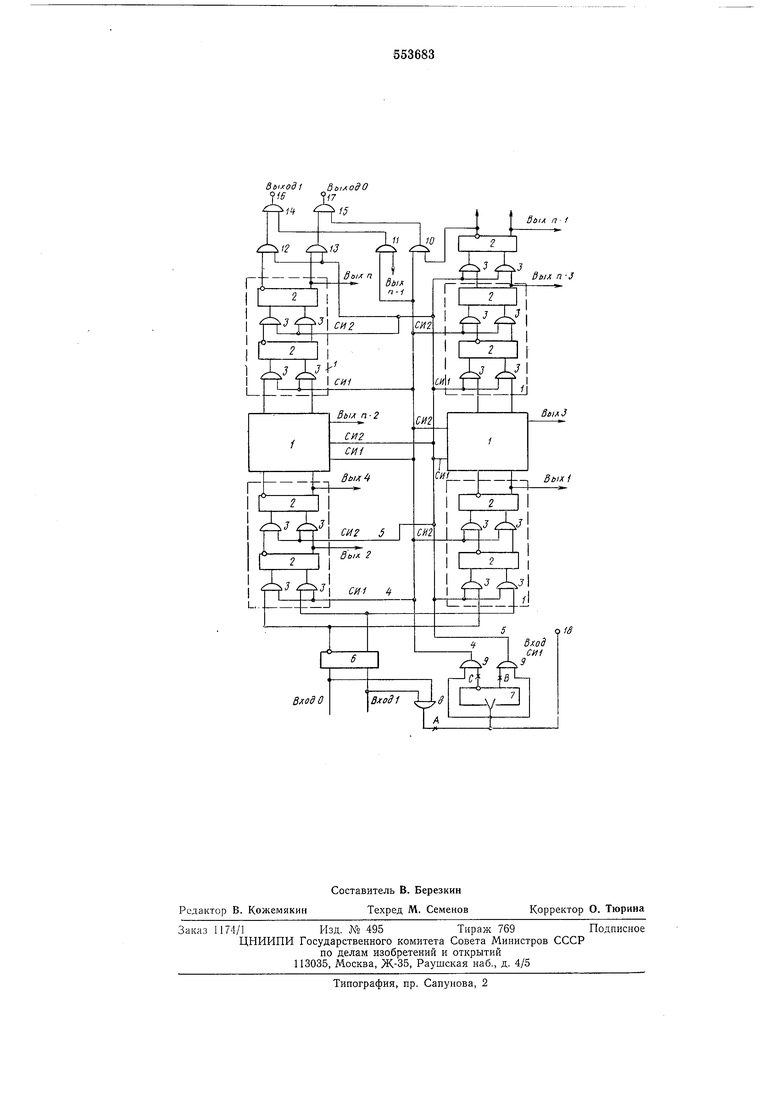

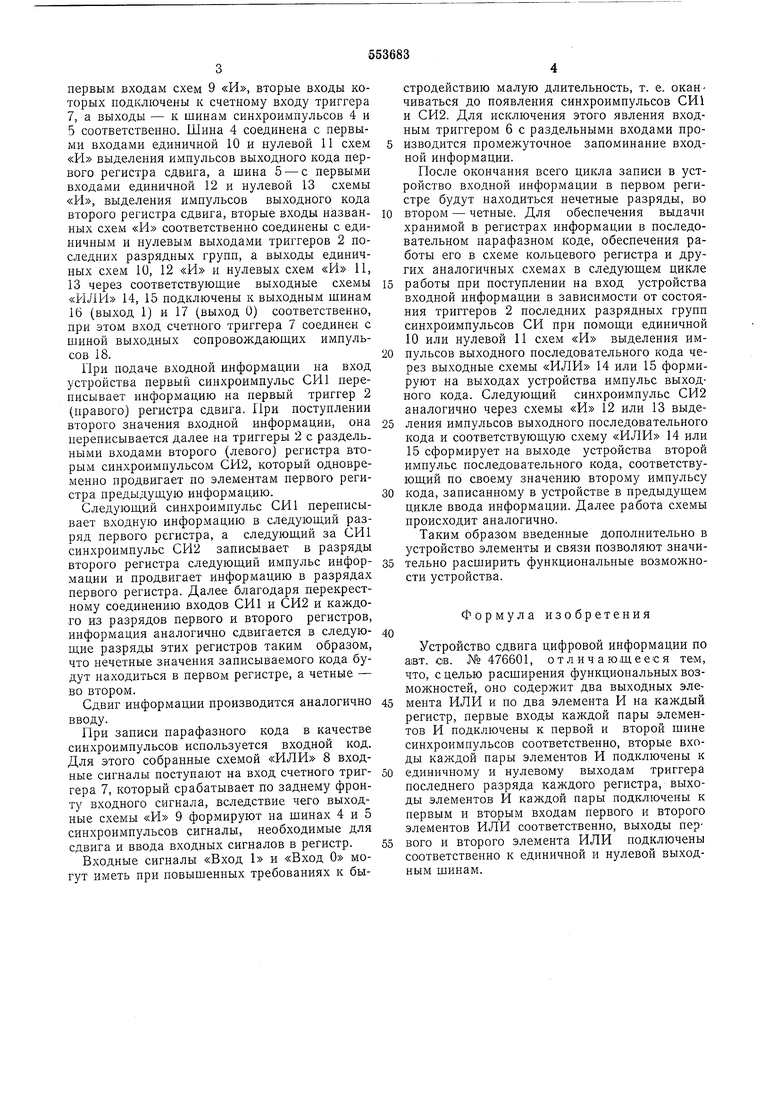

первым входам схем 9 «И, вторые входы которых подключены к счетному входу триггера 7, а выходы - к шинам синхроимпульсов 4 и 5 соответственно. Шина 4 соединена с первыми входами единичной 10 и нулевой 11 схем «И выделения импульсов выходного кода первого регистра сдвига, а шина 5 - с первыми входами единичной 12 и нулевой 13 схемы «И, выделения импульсов выходного кода второго регистра сдвига, вторые входы названных схем «И соответственно соединены с единичным и нулевым выходами триггеров 2 последних разрядных групп, а выходы единичных схем 10, 12 «И и нулевых схем «И И, 13 через соответствуюш,ие выходные схемы «Р1ЛИ 14, 15 подключены к выходным шинам 16 (выход 1) и 17 (выход 0) соответственно, при этом вход счетного триггера 7 соединен с шиной выходных сопровождаюш,их импульсов 18.

При подаче входной информации на вход устройства первый синхроимпульс СИ1 переписывает информацию на первый триггер 2 (правого) регистра сдвига. При поступлении второго значения входной информации, она переписывается далее на триггеры 2 с раздельными входами второго (левого) регистра вторым синхроимпульсом СИ2, который одновременно продвигает но элементам первого регистра предыдущую информацию.

Следующий синхроимпульс СИ1 переписывает входную информацию в следующий разряд первого регистра, а следующий за СИ1 синхроимпульс СИ2 записывает в разряды второго регистра следующий импульс информации и продвигает информацию в разрядах первого регистра. Далее благодаря перекрестпому соединению входов СИ1 и СИ2 и каждого из разрядов первого и второго регистров, информация аналогично сдвигается в следующие разряды этих регистров таким образом, что нечетные значения записываемого кода будут находиться в первом регистре, а четные - во втором.

Сдвиг информации производится аналогично вводу.

При записи парафазного кода в качестве синхроимпульсов используется входной код. Для этого собранные схемой «ИЛИ 8 входные сигналы поступают на вход счетного триггера 7, который срабатывает по заднему фронту входного сигнала, вследствие чего выходные схемы «И 9 формируют на щинах 4 и 5 синхроимпульсов сигналы, необходимые для сдвига и ввода входных сигналов в регистр.

Входные сигналы «Вход 1 и «Вход О могут иметь при повышенных требованиях к быстродействию малую длительность, т. е. оканчиваться до появления синхроимпульсов СИ1 и СИ2. Для исключения этого явления входным триггером 6 с раздельными входами производится промежуточное запоминание входной информации.

После окончания всего цикла записи в устройство входной информации в первом регистре будут находиться нечетные разряды, во втором - четные. Для обеспечения выдачи хранимой в регистрах информации в последовательном парафазном коде, обеспечения работы его в схеме кольцевого регистра и других аналогичных схемах в следующем цикле работы при поступлении на вход устройства входной информации в зависимости от состояния триггеров 2 последних разрядных групп синхроимпульсов СИ при помощи единичной 10 или нулевой 11 схем «И выделения импульсов выходного последовательного кода через выходные схемы «ИЛИ 14 или 15 формируют на выходах устройства импульс выходного кода. Следующий синхроимпульс СИ2 аналогично через схемы «И 12 или 13 выделения импульсов выходного последовательного кода и соответствующую схему «ИЛИ 14 или 15 сформирует на выходе устройства второй импульс последовательного кода, соответствующий по своему значению второму импульсу кода, записанному в устройстве в предыдущем цикле ввода информации. Далее работа схемы происходит аналогично.

Таким образом введенные дополпительно в устройство элементы и связи позволяют значительно расширить функциональные возможности устройства.

Формула изобретения

Устройство сдвига цифровой информации по авт. ОБ. № 476601, отличающееся тем, что, с целью расширения функциональных возможностей, оно содержит два выходных элемента ИЛИ и по два элемента И на каждый регистр, первые входы каждой пары элементов И подключены к первой и второй щине синхроимпульсов соответственно, вторые входы каждой пары элементов И подключены к единичному и нулевому выходам триггера последнего разряда каждого регистра, выходы элементов И каждой пары подключены к первым и вторым входам первого и второго элементов ИЛИ соответственно, выходы первого и второго элемента ИЛИ подключены соответственно к единичной и нулевой выходным шинам.

Bbixodf дылодО

It 4- V

i/J

i2

Suif n /

It W

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сдвига цифровой информации | 1977 |

|

SU656107A2 |

| Устройство сдвига цифровой информации | 1972 |

|

SU476601A1 |

| Устройство для сдвига цифровой информации | 1976 |

|

SU660047A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1015443A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Регистр сдвига | 1976 |

|

SU682950A1 |

| Устройство для управления шаговым двигателем | 1972 |

|

SU514411A1 |

| Парафазный сдвигающий регистр | 1976 |

|

SU739654A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

SxodO

3 Ж5

Влод1

I-

Авторы

Даты

1977-04-05—Публикация

1975-10-08—Подача