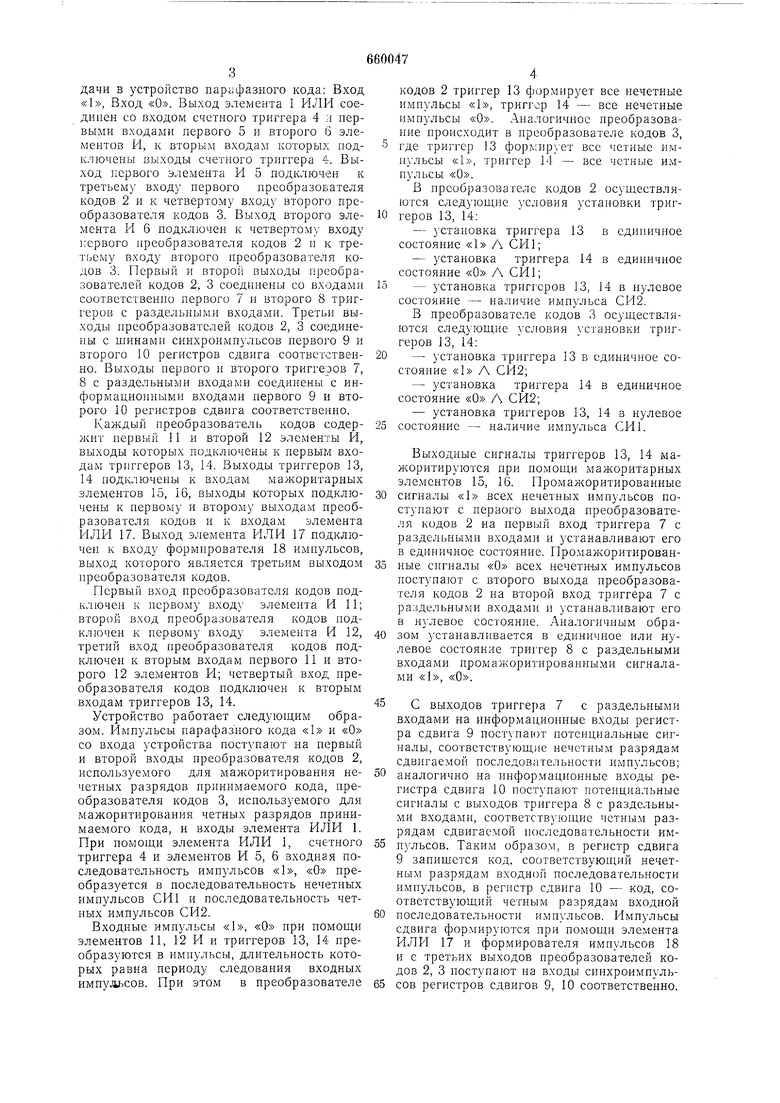

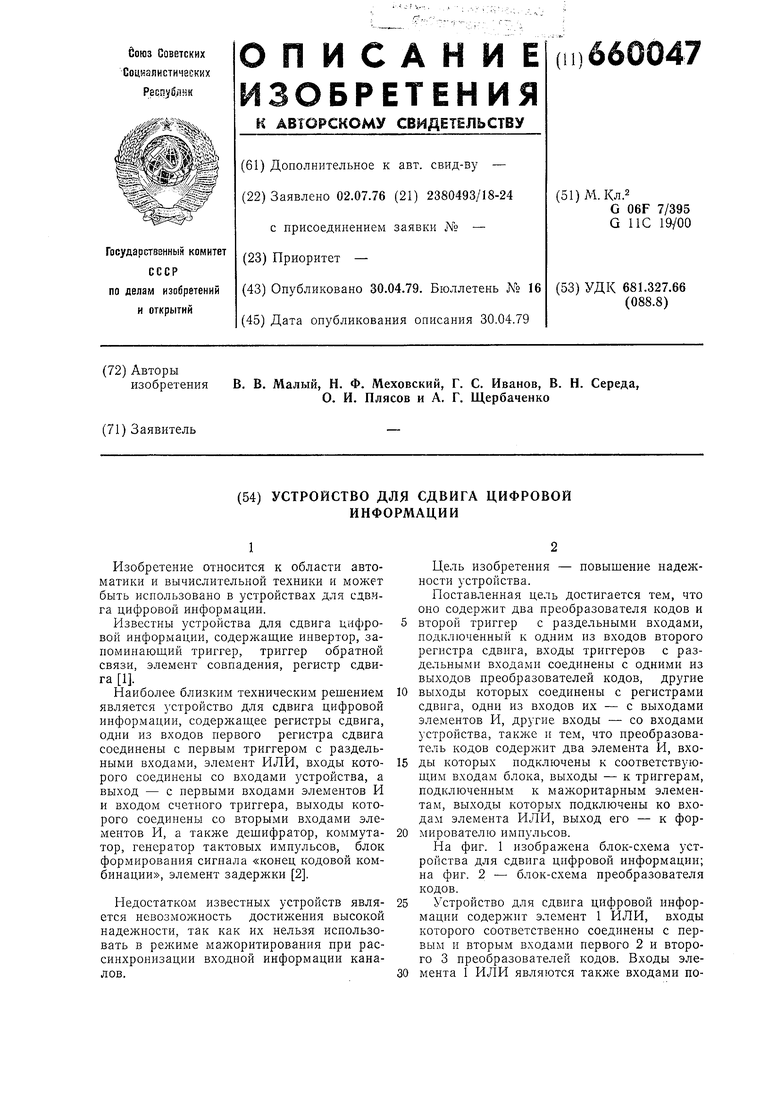

дачи в устройство пар 1фазного кода: Вход «1, Вход «О. Выход элемента 1 Р1ЛИ соединен со входом счетного триггера 4 л первыми входами первого 5 и второго 6 элементов И, к вторым входам которых подключены выходы счетного триггера 4. Выход первого элемента И 5 подключен к третьему входу первого преобразователя кодов 2 и к четвертому входу второго преобразователя кодов 3. Выход второго элемента И 6 подключен к четвертом/ входу первого преобразователя кодов 2 и к третьему входу второго преобразователя кодов 3. Первый и второй выходы преобразователей кодов 2, 3 соедипены со входами соответственно первого 7 п второго 8 триггеров с раздельными входами. Третьи выходы иреобразователей кодов 2, 3 соединены с шинами синхроимпульсов первого 9 и второго 10 регистров сдвпга соответственно. Выходы первого п второго триггеров 7, 8 с раздельными входами соединены с информацио 1ными входами первого 9 и второго 10 регистров сдвига соответственно.

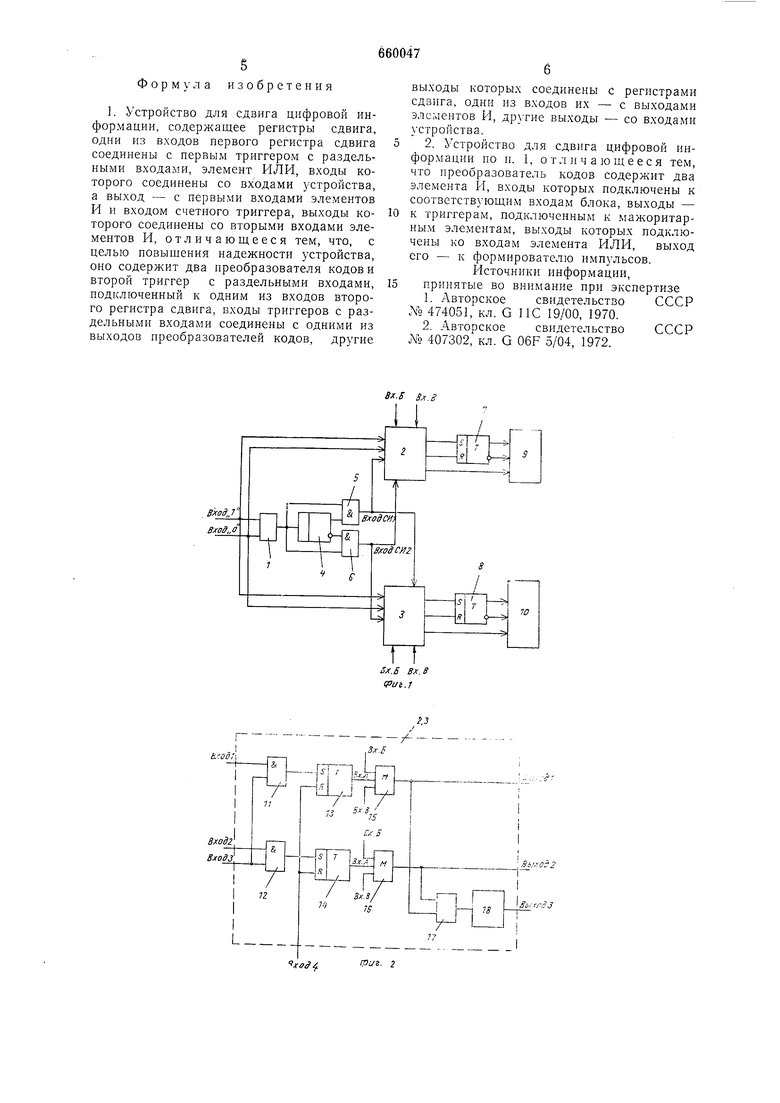

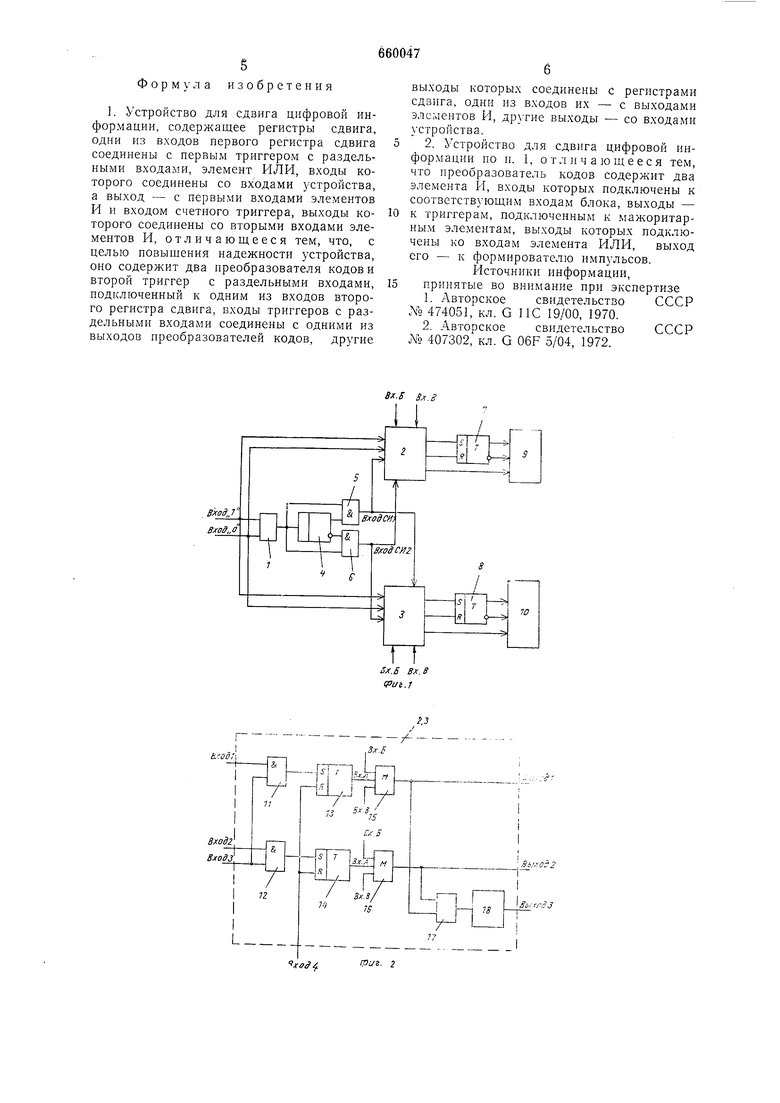

1чаждый преобразователь кодов содержит первый 11 и второй 12 элементы И, выходы которых подключены к первым входам триггеров 13, 14. Выходы триггеров 13, 14 под1.лючены к входам мажоритарных элементов 15, 16, выходы которых подключены к первому и второму выходам преобразователя кодов и к входам элемента ИЛИ 17. Выход элемента ИЛИ 17 подключен к входу формирователя 18 имнульсов, выход которого является третьим выходом преобразователя кодов.

Иервый вход преобразователя кодов подключеп к первому входу элемента И 11; второй вход преобразователя кодов подключен к первому входу элемента И 12, третий вход преобразователя кодов подключен к вторым входам первого И и второго 12 элементов И; четвертый вход преобразователя кодов подключен к вторым входам триггеров 13, 14.

Устройетво работает следующим образом. Импульсы парафазного кода «1 и «О со входа устройства поступают на первый и второй входы преобразователя кодов 2, иепользуемого для мажоритирования нечетных разрядов принимаемого кода, преобразователя кодов 3, используемого для мал ;оритирования четных разрядов принимаемого кода, и входы элемента ИЛИ 1. При помощи элемента ИЛИ 1, счетного триггера 4 и элементов И 5, 6 входная последовательность импульсов «1, «О преобразуется в последовательность нечетных импульсов СИ1 и последовательность четных импульсов СИ2.

Входные импульсы «1, «О при помощи элементов 11, 12 И и триггеров 13, 14 преобразуются в импульсы, длительность которых равна периоду следования входных ИМПУЛЬСОВ. При этом в преобразователе

кодов 2 триггер 13 формирует все нечетные пмпульсы «1, триггер 14 - все нечетные импульсы «О. Аналогичное преобразование происходит в преобразователе кодов 3,

где триггер 13 формирует все четные импульсы «1, триггер 14 - все четные импульсы «О.

В преобразователе кодов 2 осуществляются следующие условия установки триггеров 13, 14:

-установка триггера 13 в единичное состояние «1 Л СИ1;

-установка триггера 14 в единичное состояние «О Л СИ1;

- установка триггеров 13, 14 в нулевое состояние - наличие импульса СИ2.

В преобразователе кодов 3 осуществляются следующие ус.гговия установки триггеров 13, 14:

- установка триггера 13 в единичное состояние «1 Л СИ2;

-установка триггера 14 в единичное состояние «О Л СИ2;

-установка триггеров 13, 14 в нулевое состояние - наличие импульса СИ1.

Выходные сигналы триггеров 13, 14 мажоритируются при помощи мажоритарных элементов 15, 16. Промажоритированные

сигналы «1 всех нечетных импульсов поступают с первого выхода преобразователя кодов 2 на первый вход триггера 7 с раздельными входами и устанавливают его в единичное состояние. Промажоритированные сигналы «О всех нечетн-ых импульсов поступают с второго выхода преобразователя кодов 2 на второй вход триггера 7 с раздельными входами и }станавливают его в нулевое состояние. Аналогичным образом устанавливается в единичное или нулевое состояние триггер 8 с раздельными входами промажоритироваинымн сигналами «1, «О.

С выходов триггера 7 с раздельными входами иа информационные входы регистра сдвига 9 поступают потенпиальные сигналы, соответствующие нечетным разрядам едвигаемой последовательности импульсов;

аналогично на информационные входы регистра сдвига 10 поступают потенциальные сигналы с выходов триггера 8 с раздельными входами, соответствующие четным разрядам сдвигаемой последовательности импульсов. Таким образом, в регистр сдвига 9 запишется код, соответствующий нечетным разрядам входной последовательности импульсов, в регистр сдвига 10 - код, соответствующий четным разрядам входной

последовательности импульсов. Импульсы сдвига формируются при помощи элемента ИЛИ 17 и формирователя импульсов 18 и с третьих выходов иреобразователей кодов 2, 3 поступают на входы синхроимпульсов регистров сдвигов 9, 10 соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сдвига цифровой информации | 1975 |

|

SU553683A1 |

| Устройство сдвига цифровой информации | 1977 |

|

SU656107A2 |

| Устройство сдвига цифровой информации | 1972 |

|

SU476601A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1015443A1 |

| Преобразователь параллельного кода в последовательный | 1977 |

|

SU780002A1 |

| Уравновешивающая схема для аналогоцифрового преобразователя поразрядного уравновешивания | 1972 |

|

SU444319A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Устройство для приема биимпульсного сигнала | 1987 |

|

SU1427588A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

Авторы

Даты

1979-04-30—Публикация

1976-07-02—Подача