Изобретение относится к автоматике и вычислительной технике, может быть использовано для приема и передачи дискретных сообщений и являет- ся усовершенствованием устройства по авт. св. № 1089608.

Цель изобретения - повышение надежности устройства,

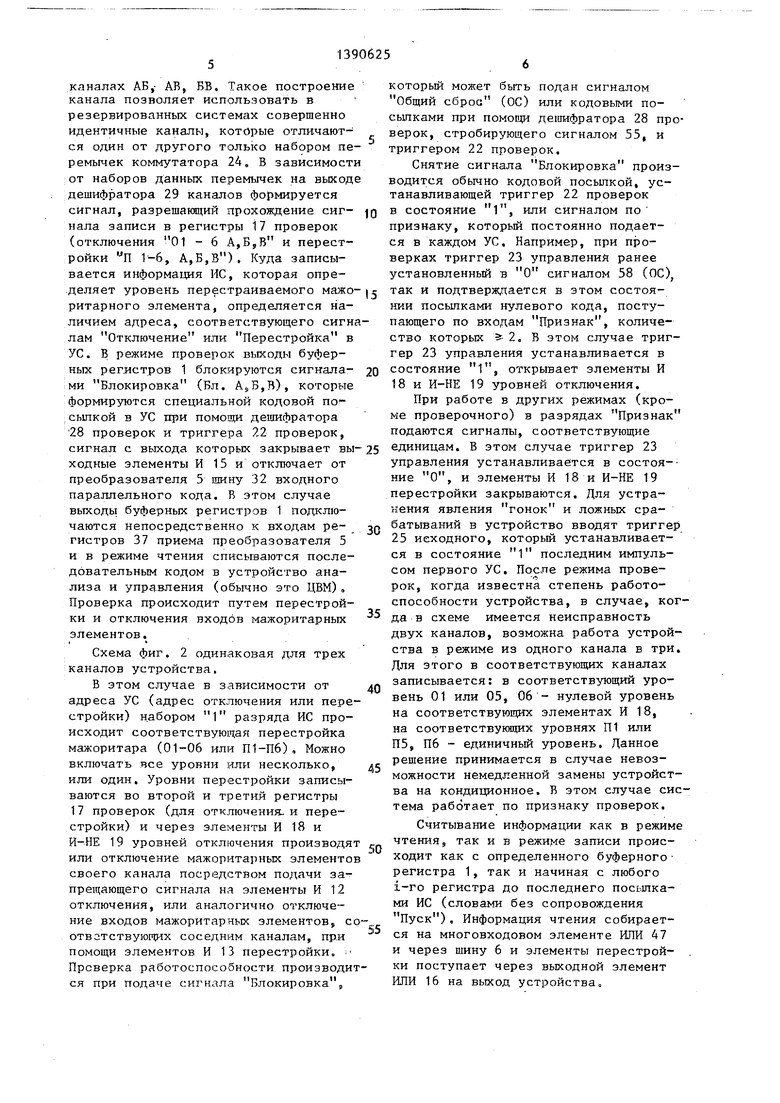

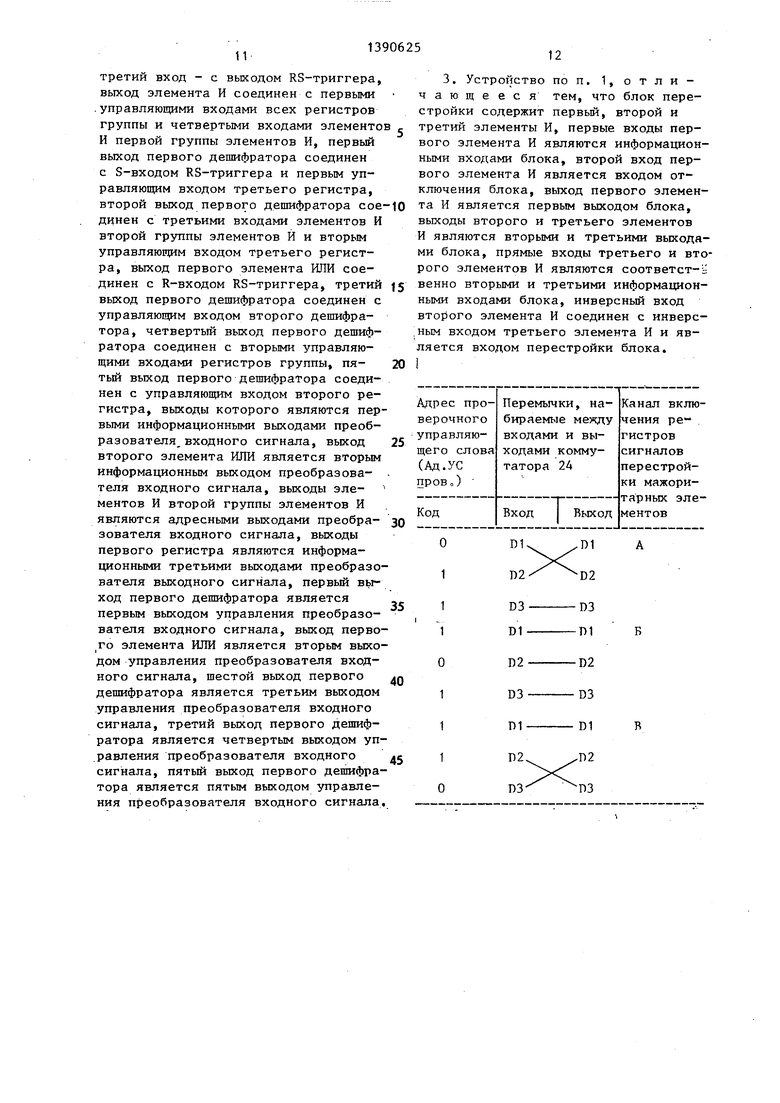

На фиг. 1 и 2 показана функцио- нальная схема предлагаемого устройства на фиг, 3 - функциональная схема Преобразователя входных сигналовj на фиг. 4 - функциональная схема блока перестройки; на фиг. 5 - вре- Менная диаграмма работы блока форми- |рования сигнала; на. фиг. 6 - временная диаграмма работы преобразователя входных сигналов.

Устройство содержит (фиг, 1) -в :каждом канале буферные регистры 1, мажоритарные элементы 2-4, преобра- ;зователи 5 входных сигналов, выход |(шина) 6 преобразователя входного |сигнала, входы (шины) 7-11 преобра-- Зоватёля входного сигнала, элементы И 12 отключения, элементы И 13 перестройки, элемент И--ШШ 14 (переключатели) выходные элементы И 15 (не показаны), выходной элемент ИЛИ 16j, регистры 17 проверок,, элементы И

18уровней перестройки, элементы И-Н

19уровней перестройки; элемент И 20 управления, элементы И 21 проверок, триггер 22 проверок,,- триггер 23 уп- равления, коммутатор 24, триггер 25 исходного, элемент ШШ 26 управле- |Ния, элемент ИЛИ 27 регистра прове- |рок, дешифратор 28 проверок, дешиф- :ратор 29 каналов, элемент И 30 дешиф ратора каналов, многовходовой элемен ИЛИ 31 (не-показан), шину 32 входного параллельного кода устройства, блок 33 перестройки.

Преобразователь входного сигнала (фиг. 3) содержит 1К-триггер 34, RS- триггер 35,регистр 36 сдвига, регистры 37 приема, регистр 38 адреса, регистр 39 хранения информационного слова (ИС), дешифраторы 40 и 41, элемент 42 задержки, .блок 43 форг-гаро вания сигнала, элементы И 44 регистров приема, элементы И 45 и 46, элементы ИЛИ 47 и 483 инвертор 49, счетчик 50, выходы 51-61 являются вы ходами отдельных блоков преобразователя.

Блок 33 перестройки (фиг. 4) содержит элементы И отключения 62 тл

перестройки 63,, к входам которых подключены шины информации и управления. Устройство работает следующим образом.

Входные сигналы поступают на шины 7 Вх. Ч и 8 Вх.СИ (в случае информации Вх.1 и Вх.0 д анные сигналы объединяются по ИЛИ и выпол- няют роль импульсов шины Вх.СИ).Последовательность поступления входных сигналов показана на фиг. 6. Сигнал, поступающий по шине 9 Пуск, устанавливает счетные элементы cxei-ibi в исходное положение. Таким образом, после прохождения сигнала Пуск импульсы на имне 7 Вх.СИ задним фронтом считаются счетчиком 50, а информация, поступающая на шину 8 Вх.1, запоминается 1К-триггером 34, после чего сдвигается импульсом СИ в регистре 36 сдвига, а 1К-триггер 34, за- : тем сбрасывается в О (в случае поступления единичной информации) задним фронтом, формируемым на выходе элемента 42 задержки. Далее в зависимости от числа поступивших импульсов производится дешифровка состояния счетчика 50 дешифратором 40 команд.,,

Управляющее слово (УС) содержит обычно информацию : адрес, признак работы и проверки,а также два холостых разряда в конце посыпки. После прохождения рабочих разрядов УС холостой импульс кода переписьшает информацию с регистра 36 сдвига на дешифратор 41 адреса, а последний импульс УС записывает (сигнал 56) информацию с дешифратора 41 в регистр 38 адреса, формируя на его выходе соответствующий начальный адрес. Далее информация с регистра 36 сдвига задним фронтом последнего несущего информацию импульса ИС (ИС также имеет два последних холостых разряда) пере- письгоается в регистр 39 хранения ИС (сигнал 59).

При прохождении УС в отдельный самостоятельный разряд записьшается сигнал записи или чтения, В режиме записи устройство производит запись информации ИС (ИС1-ИСп) в буферные регистры 1, а в режиме чтения производятся перезапись информации на регистры 37 приема и считывание этой информации через выходной мажоритар- i ный элемент 4.

В режиме записи импульс на выходе 56 передним фронтом стробирует выход регистра 38 адреса, вследствие чего на выходах элементов И 45 формируется соответствующий сигнал начального адреса А1, А2 или An, который проходит через мажоритарные элементы 3 адреса, стробирует буферные регистры 1 в зависимости от адре са, запоминаемого на регистре 38 адреса. Задний фронт импульса на выходе 56 сдвигает информацию начального адреса ,на регистре 38 адреса, и с приходом следующего ИС процесс повто ряется до окончания цикла работы (до достижения величины п, где п - максимальный адрес буферного регистра 1).

Устройство может работать как.от одного ИС, так и в режиме записи нескольких ИС (с адреса А1 или Ai до An).

В этом случае быстродействие устройства повышается на величину

К п1 - 1,

где п1 - количество посыпаемых ИС.

Длительность импульса на выходах А1-Ап перекрывает практически любзгю рассинхронизацию между каналами в поступлении информации (длительность определяется двумя длительностями тактов, что очень важно при работе в дистанционных системах).

В режиме чтения в УС поступает признак чтения на выходе 57, который запрещает прохождение импульсов через элементы И 45 и через инвертор 49 разрешает прохождение импульсов через элементы И 44 регистров приема Импульсом на шине 54 происходит запись информации с шин 11, которые представляют собой информацию с шин 32 параллельного входного кода или с выходов буферных регистров в зависимости от сигнала Блокировка (Б на регистры 37 приема, В зависимости от того, с каких буферного регистра и входной шины необходимо провести чтение, адресная посылка в УС дешифруется аналогично указанному и открывает соответствующий элемент И 44 регистров приема, в связи с чем информация считывается через элемент ИЛИ 47 только с одного регистра 37 приема. При смене адреса открьгоается следующий элемент И 44 и так далее до окончания цикла. В зависимости от

5

5

о

0 g o g

5

требований, предъявляемых к системам, выходной элемент может представлять собой обычный согласующий элемент или мажоритарный элемент.

Временная диаграмма работы блока 43 формирования сигнала приведена на фиг. 5.

Б состав адресного массива УС входят также адреса, предназначенные для определения работоспособности каналов устройства. Они принимаются в первый регистр 17 проверок и записываются в него сигналом по шине 53. Данньй регистр обычно содержит разряды для хранения сигналов Начало блокировки, Конец блокировки, адреса отключения мажоритарных элементов (Откл), перестройки мажоритарных элементов (Пер, разряды признака работы, проверок и канальности.Без применения проверок в трехканальной системе невозможно определить наличие неисправности в одном канале, поскольку одна или несколько неисправностей в каналах парируются мажори- тарньпчи элементами, а .при наличии двух неисправностей система выходит из строя. Поэтому необходимо уметь определять неисправность канала для проведения ремонтных работ, а при невозможности их проведения обеспечивать работу с одним исправным каналом, т.е. при двух неисправностях.

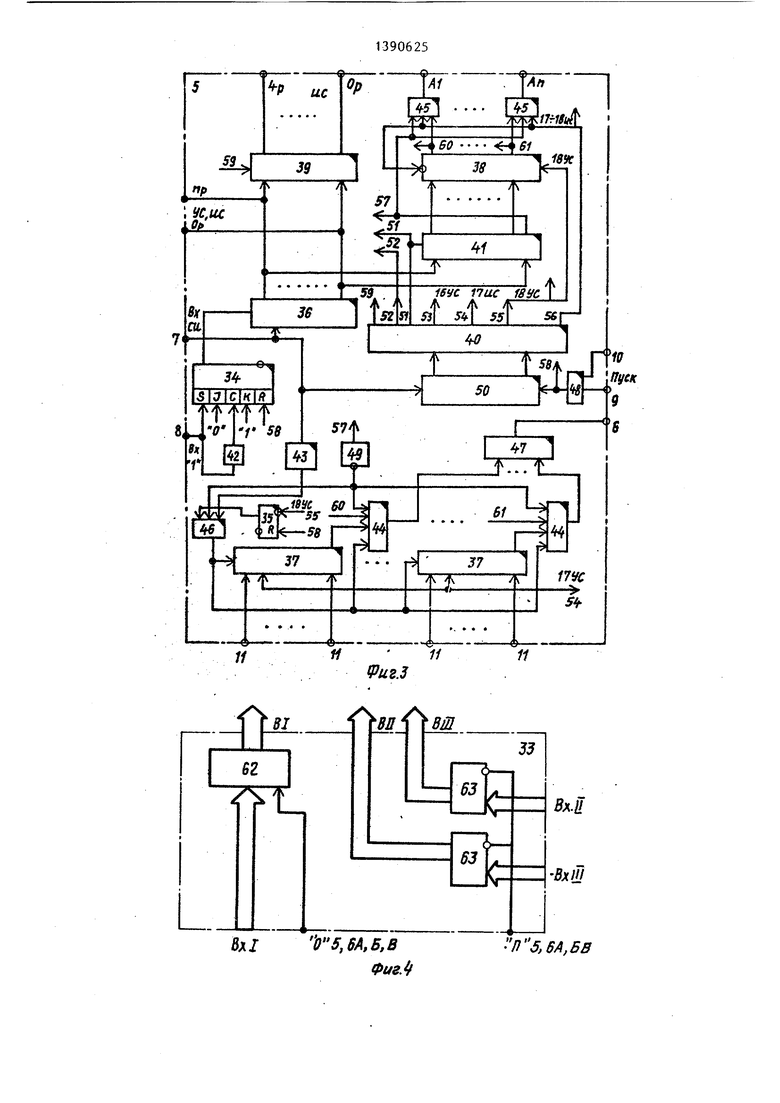

Информация, записанная в первом регистре 17 проверок, начинает производить перестройку структуры устройства. По трем каналам информация поступает симметричная, но требуется различная реакция различных каналов. Это осуществляется установкой перемычек в коммутаторе 24, при этом вся остальная структура и аппаратурное построение каналов одинаковое. Реакция канала зависит от того, при каких кодах разрядов проверки появляется импульс записи в первом регистре 17 (Отключение) или во втором регистре 17 (Перестройка).

Набор перемычек коммутатора 24 показан в таблице,

Из характера набора перемычек между D1, П2 и Г)3 коммутатора 24 очевидно, что при наборе в УС кодов 001, 010, 100 мажоритарные элементы при помощи второго и третьего регистров 17 перестраиваются соответственно в

каналах АБ,- АВ, ВВ. Такое построение канала позволяет использовать в резервированных системах совершенно идентичные каналы, которые отличаются один от другого только набором перемычек коммутатора 24, В зависимости от наборов данных перемычек на выходе дешифратора 29 каналов формируется сигнал, разрешаннций прохождение сигнала записи в регистры 17 проверок (отключения 01 - 6 А,Б,В и перестройки П 1-6, А,Б,в). Куда записывается информация ИС, которая определяет уровень перестраиваемого мажоритарного элемента, определяется наличием адреса, соответствующего сигна лам Отключение или Перестройка в УС. В режиме проверок выходы буферных регистров 1 блокируются сигналами Блокировка (Бл. А5,В,В), которые формируются специальной кодовой сылкой в УС при ПОМО13Щ дешифратора 28 проверок и триггера 22 проверок, сигнал с выхода которых закрывает выходные элементы И 15 и отключает от преобразователя 5 шину 32 входного параллельного кода. В этом случае выходы буферных регистров 1 подключаются непосредственно к входам регистров 37 приема преобразователя 5 и в режиме чтения списываются последовательным кодом в устройство анализа и управления (обычно это ЦВМ), Проверка происходит путем перестройки и отключения входов мажоритарных элементов.

Схема фиг. 2 одинаковая для трех каналов устройства,

В этом случае в зависимости от адреса УС (адрес отключения или перестройки) набором 1 разряда ИС происходит соответствующая перестройка мажоритара (01-06 или П1-П6), Можно включать все уровни или несколько, или один. Уровни перестройки записываются во второй и третий регистры 17 проверок (для отключениями перестройки) и через элементы И 18 и И-НЕ 19 уровней отключения производят или отключение мажоритарных элементов своего канала посредством подачи запрещающего сигнала на элементы И 12 отключения, или аналогично отключение входов мажоритарных элементов, ср отватствую1ч 1х соседним каналам, при помощи элементов И 13 перестройки, Проверка работоспособности, производится при подаче сигнала Блокировка,

которьш может быть подан сигналом Общий сброс (ОС) или кодовыми посыпками при помош дешифратора 28 проверок, стробирующего сигналом 55, и триггером 22 проверок.

Снятие сигнала Блокировка производится обычно кодовой посьткой, устанавливающей триггер 22 проверок в состояние 1, или сигналом по признаку, который постоянно подается в каждом УС, Например, при проверках триггер 23 управления ранее установленный в О сигналом 58 (ОС), так и подтверж,дается в этом состоянии посылками нулевого кода, поступающего по входам Признак, количество которых э: 2, В этом случае триггер 23 управления устанавливается в состояние 1, открывает элементы И 18 и И-НЕ 19 уровней отключения.

При работе в других режимах (кроме проверочного) в разрядах Признак подаются сигналы, соответствующие единицам. В этом случае триггер 23 управления устанавливается в состоя- ние О, и элементы И 18 и И-НЕ 19 перестройки закрываются. Для устранения явления гонок и ложных срабатьгеаний в устройство вводят триггер 25 исходного, который устанавливает

сом первого УС. После режима проверок, когда известна степень работоспособности устройства, в случае, когда в схеме имеется неисправность двух каналов, возможна работа устройства в режиме из одного канала в три. Для этого в соответствующих каналах записывается; в соответствующий уровень 01 или 05, 06 - нулевой уровень на соответствующих элементах И 18, на соответствукщих уровнях П1 или П5, П6 - единичный уровень. Данное решение принимается в случае невозможности немедленной замены устройства на кондиционное. В этом случае система работает по признаку проверок.

Считывание информации как в режиме чтения,, так и в режиме записи происходит как с определенного буферного регистра 1, так и начиная с любого i-ro регистра до последнего посьшка- ми ИС (словами без сопровождения Пуск), Информация чтения собирается на многовходовом элементе ИЛИ 47 и через шину 6 и элементы перестройки поступает через выходной элемент ИЛИ 16 на выход устройства.

5

0

5

0

5

В зависимости от требований, предъявляемых к системам, выходной элемент ИЛИ 16 может представлять собой обычный согласующий элемент (напри- мер, магистральньй усилитель).

Место чтения информации определяется переключателем 14, т.е. информация может считываться с шин входного параллельного кода 32 (при от- сутствии блокировки) или с выходов буферных регистров 1 (блокировка подана) .

Перестройка работы из одного канала в три по выходам информации и адресов производится блоком 33 перестройки, По сигналу 05 отключаются каналы, в которых имеется неисп- равность, а по сигналу П5 производится подключение входов буферных регистров 1 всех каналов к исправному каналу, которые затем объединяются многовходовым элементом ИЛИ 31 и через разблокированные выходные элементы И 15 поступают на выход уст- ройства.

Формула изобретения

1. Устройство для приема последовательного кода по авт. св. 1089608, отличающееся тем, что, d целью повышения надежности, в него . введены первый, второй и третий регистры, первьй и второй дешифраторы, первый, второй и третий триггеры, первьш, второй, третий и четвертый элементы И, первьш и второй элементы ШШ, коммутатор, первая, вторая, третья, четвертая, пятая, шестая, седьмая группы элементов И, первая и вторая группа ключей, элементы И в каждом канале, элементы ИЛИ в каждом /канале и группа элементов И-ИЛИ,й каждо .канале между соответствующим входом преобразователя входного сигнала и : входом устройства подключен выходом и первым входом соответствующий элемент И-ЙЛИ группы элементов И-ИЛИ, второй вход которого соединен с выходом буферного регистра, третий вход соединен с выходом первого триг гера, в каждом канале между адресными выходами преобразователя входных сигналов и точкой объединения вхо дов первых мажоритарных элементов всех каналов подключены первыми вхо- дами и выходом соответствующие элементы И первой группы элементов И, вторые виоды которых соединены с вы

.

JO у., 20 25

30, ом -- 5

45

50

ходом соответствующего ключа первой группы, в каждом канале между информационными первыми выходами преобразователя входных сигналов и точкой объединения входов вторых мажоритарных элементов всех каналов подключены первыми входами и выходом соответствующие элементы И второй группы элементов И, вторые входы которых соединены с выходом соответствующих ключей первой группы, в каждом канале между точками соответствующего объединения вторых и третьих входов первых мажоритарных элементов и вторыми и третьими входами первых мажоритарных элементов подключены первым входом и выходом соответствующие элементы И третьей группы элементов И, вторые входы которых соединены с выходами соответствующих ключей второй .группы, в каждом канале между точками объединения вторых и третьих вхо-. ДОН вторых мажоритарных элементов подключены первыми входами и выходами элементы И четвертой труппы, вторые входы которых соединены с выходами соответствующих ключей второй группы, между вторым информационным выходом преобразователя входных сигналов и точкой объединения входов третьих мажоритарных элементов всех каналов подключены первым входом и выходом соответствующие элементы И пятой группы, вторые входы которых соединены с выходами соответствующих ключей первой группы, в каждом канале между точками соответствующего объединения вторых и третьих входов третьих мажоритарных элементов и вторыми и третьими входами третьих мажоритарных элементов подключены первыми входами и выходами соответствующие элементы И шестой группы элементов И, вторые входы которых подключены к выходам соответствующих ключей второй группы, в каждом канале между выходом третьего мажоритарного элемента и выходом устройства подключены первым входом элемент И и выходом элемент ИЛИ, выход элемента И соединен с первым входом элемента ИЛИ, второй и третий входы которого подключены к выходам элементов И седьмой группы, первые входы которых соединены с выходами элементов И других каналов, вторые входы соединены с выходами соответствующих ключей второй группы, информационные

третьи выходы преобразователей входных сигналов соединены с информаиион- ными входами первого, второго и третьего регистров, выходы, первого регистра соединены соответственно с первыми входами ключей первой группы, выходы второго регистра соединены соответственно с первьЛ Ж входами клю- :чей второй группы, вторые входы клю- чей первой и второй групп объединены К соединены с выходом второго тригге ра, первые выходы третьего регистра соединены с информационными входами первого дешифратора, вторые выходы третьего регистра соединены с входами коммутатора, третьи выходы третьего регистра соединенны с первьми входами первого элемен з: а FDIH и первого элемента И, вторые входы которых со еди- Нены с выходом третье;го триггера, вы- коды первых элементов И и ИЛИ соеди-- Нены соответственно с первым и вторым Входами второго триггера, информацион Йые выходы первого дешифратора соеди- ,Иены с установочньачи входами первого триггера,, первый управляющий вых.рд первого дешифратора соедднен с первьг Ки входами второго элемента ИЛИ и ВТОРОГО элемента И, второй управляю- йщй выход первого дешифратора соединен с вторым входом второго злемента ИЛИ и первым входом третьего элемента И, вьгкод второго элемента ИЛИ соединен с первым входом четвертого элемента И, вькод коммутатора соединен с входом второго дешифратора;, выход которого соединен с вторым входом четвертого элемента И; выход которого соединен с вторыми: входами второго и третьего элементов И, выходы которых соединены соответственно с входами управления первого и второго регистров , управляющий вход первого дешифратора и первый вход третьего триггера соединены с первым выходом управления преобразователя входных сигналов, второй вход третьего триггера и вход стробирования первого триггера соединены с вторым выходом управления преобразователя входных сигналовj :зход управления третьего регистра соединен с третьим вЬ)Ходо.м управления преобразователя входньк сигналовj третьи входы первого элемента ИЛИ и первого элемента И объединены и соединены с четвертым выходом управления преобразователя входных сигналов, третий вход четвертого элемента И

0

S

02) 30

35

40

45

50

55

соединен с пятым выходом управления преобразователя входных сигналов.

2 Устройство по п..1, о т л и- чающееся тем, что преобразователь входного сигнала содержит группу регистров, первый, второй и третий .регистры, первый и второй дешифраторы, счетчик, 1К-триггвр, RS-триг- гер, блок формирования сигнала, инвертор, первый и второй элементы ИЛИ, элемент задержки,, элемент И, первую и вторую группу элементов И,управляющий вход первого регистра соединен с первым входом счетчика, входом блока формирования сигнала и является пер- Bbffv входом преобразователя входного сигнала, S-вход 1К-триггера непосредственно и С-вход 1К-триггера через элемент задержки объединены и являются вторым входом преобразователя входного сигнала, выход 1К-триггера соединён с информационным входом первого регистра, входы первого элемента ИЛИ являются соответственно третьим и четвертым входами преобразователя входного сигнала, выход первого элемента ИЛИ соединен с R-входом RS- триггера и вторым входом счетчика, выходы которого соединены с соответ- ствующими входами первого дешифратора, информационные входы соответствующих регистров группы являются пятыми входами преобразователя вход- ного сигнала, выходы регистров группы соединены с первыми входами соот- ветству 01тщх элементов И первой группы выходы которых соединены с входами второго элемента ИЛИ, выходы первого регистра соединены с соответствующими входами второго perHCT-- ра И с соответствующими информационными входами второго дешифратора, первые выходы которого соединены с одноименными инфсрмационньп ш входами третьего регистра, выходы которо - го соединены с первыми входами соот- ветствующ1-1х элементов И второй груп- пь элементов И и ьтррьми входами соответствующих элементов И первой группы третьи входы которых объе- динены и соединены с выходом инвертора, вход которого объединен с вторыми входами всех элементов К второй группы элементов И и соединен с вторым выходом второго дещифратора, первьш вход элемента И соединен с выходом блока формирования сигнала, второй вход - с выходом инвертора,

третий вход - с выходом RS-триггера, выход элемента И соединен с первыми .управляющими входами всех регистров группы и четвертыми входами элементо И первой группы элементов И, первый выход первого дешифратора соединен с S-входом RS-триггера и первым управляющим входом третьего регистра, второй выход первого дешифратора сое динен с третьими входами элементов И второй группы элементов И и вторым управляющим входом третьего регистра, выход первого элемента ИЛИ соединен с R-входом RS-триггера, третий выход первого дешифратора соединен с управляющим входом второго дешифратора, четвертый выход первого дешифратора соединен с вторыми управляющими входами регистров группы, пятый выход первого дешифратора соединен с управляющим входом второго регистра, выходы которого являются первыми информационными выходами преобразователя, входного сигнала, выход второго элемента ИЛИ является вторым информационным выходом преобразова- теля входного сигнала, выходы эле- ментов И второй группы элементов И являются адресными выходами преобразователя входного сигнала, выходы первого регистра являются информационными третьими выходами преобразователя выходного сигнала, первый вьг- ход первого дешифратора является первым выходом управления преобразователя входного сигнала, выход перво го элемента ИЛИ является вторым выходом управления преобразователя входного сигнала, шестой выход первого дешифратора является третьим выходом управления преобразователя входного сигнала, третий выход первого дешифратора является четвертым выходом уп .равления преобразователя входного сигнала, пятый выход первого дешифратора является пятым выходом управления преобразователя входного сигнала

3. Устройство по п. 1, отличающееся тем, что блок перестройки содержит первьй, второй и третий элементы И, первые входы первого элемента И являются информационными входами блока, второй вход первого элемента И является входом отключения блока, выход первого элемента И является первым выходом блока, вьпсоды второго и третьего элементов И являются вторыми и третьими выходами блока, прямые входы третьего и второго элементов И являются соответст-ь венно вторыми и третьими информационными входами блока, инверсный вход второго элемента И соединен с инверс- .ным входом третьего элемента И и является входом перестройки блока.

20

Ю |5 д

Ю |5 д

25

Ю |5 д

30

Ю |5 д

35

Ю |5 д

40

SiJS 7

W/U

Прицюк

Pus.t

uc

«а®-1

Op

fl-n U51 ж

тТГ:т7к /7гУ5 г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема последовательного кода | 1982 |

|

SU1089608A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Многоканальное устройство для реверсирования двигателей постоянного тока | 1987 |

|

SU1573520A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 1995 |

|

RU2084011C1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

Устройство относится к автоматике и вычислительной технике и может быть использовано для приема и передачи дискретной информации. Целью устройства является повышение надежности. Устройство содержит в каждом канале буферные регистры, мажоритарные элементы, преобразователи входных сигналов, элементы И отключения, элементы И перестройки, переключите-: ли, выходные элементы И, выход ной элемент ИЛИ,регистры проверок, элементы И уровней перестройки, элементы И-НЕ уровней перестройки, элемент И управления, элементы И проверок, триггер проверок, триггер управления, коммутатор, триггер исходного,. элемент ИЛИ управления, элемент регистра проверок, дешифратор проверок, депшфратор каналов, элемент И дешифратора каналов, многовходовой элемент ИЛИ, шина входного параллельного кода устройства и блок перестрой- ки. Кроме того, преобразователь входного сигнала содержит 1-К-триггер, RS-триггер, регистр сдвига, регистры приема, регистр адреса, регистр хранения информационного слова, дешифраторы, элемент задержки, блок формирования сигнала, элементы И регистров приема, элементы И, элементы ИЛИ, инвертор, счетчик. Устройство обеспечивает о 1ределение работоспособности каналов передачи информации на всех уровнях мажорирования и определение и блокировку неисправных информационных трактов, охватьгеаемых мажоритарными элементами, что устраняет накопление ошибки в передаваемой информации. Устройство благодаря осуществлению функций проверки/отключения не теряет работоспособности при двух неисправных каналах. 2 ЗпП„ ф-лы, 6 ил., 1 табл. i (Л

,6А.Б.В

Фиг.

П 5,6А, Б В

| Устройство для приема последовательного кода | 1982 |

|

SU1089608A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-04-23—Публикация

1986-08-22—Подача