(54) ИМПУЛЬСНЫЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU839036A1 |

| Умножитель частоты следования импуль-COB | 1979 |

|

SU817996A1 |

| Устройство для воспроизведения сигналов цифровой информации с носителя магнитной записи | 1982 |

|

SU1040516A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2042261C1 |

| Способ многоканального воспроизведения уплотненных во времени информационных сигналов с магнитного носителя | 1985 |

|

SU1283832A1 |

| Умножитель частоты | 1983 |

|

SU1171956A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Умножитель частоты | 1974 |

|

SU627554A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Устройство для обработки вибрационныхзАпиСЕй | 1979 |

|

SU842679A1 |

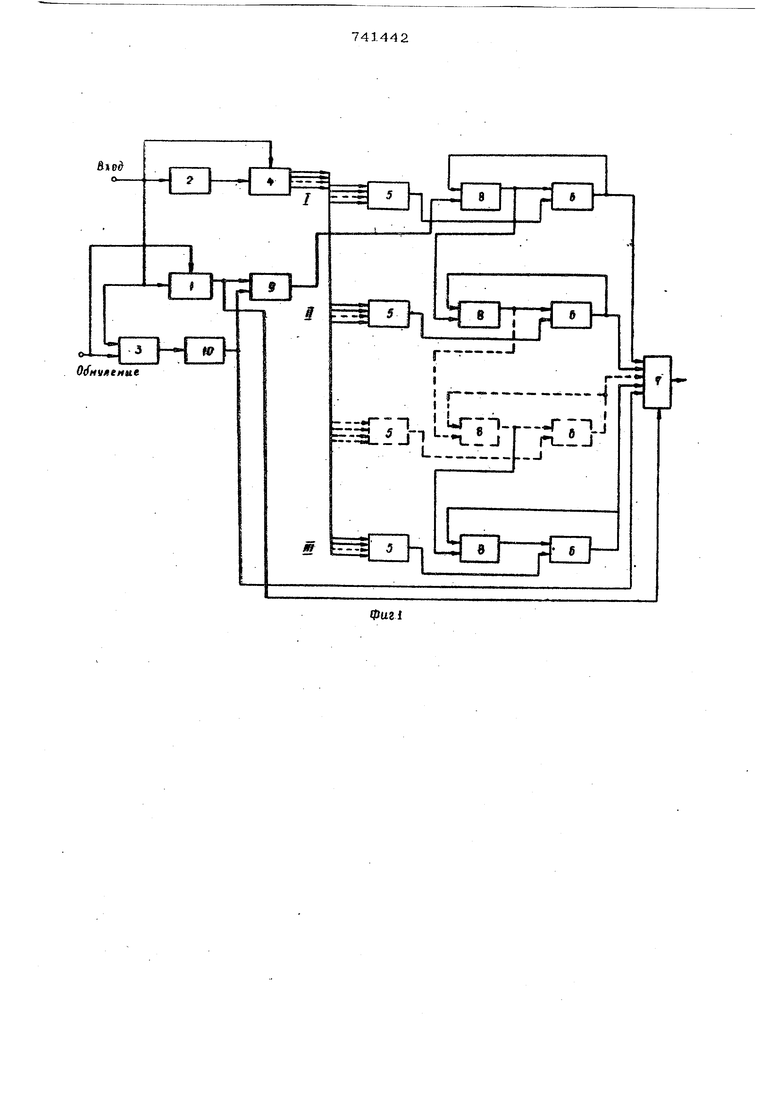

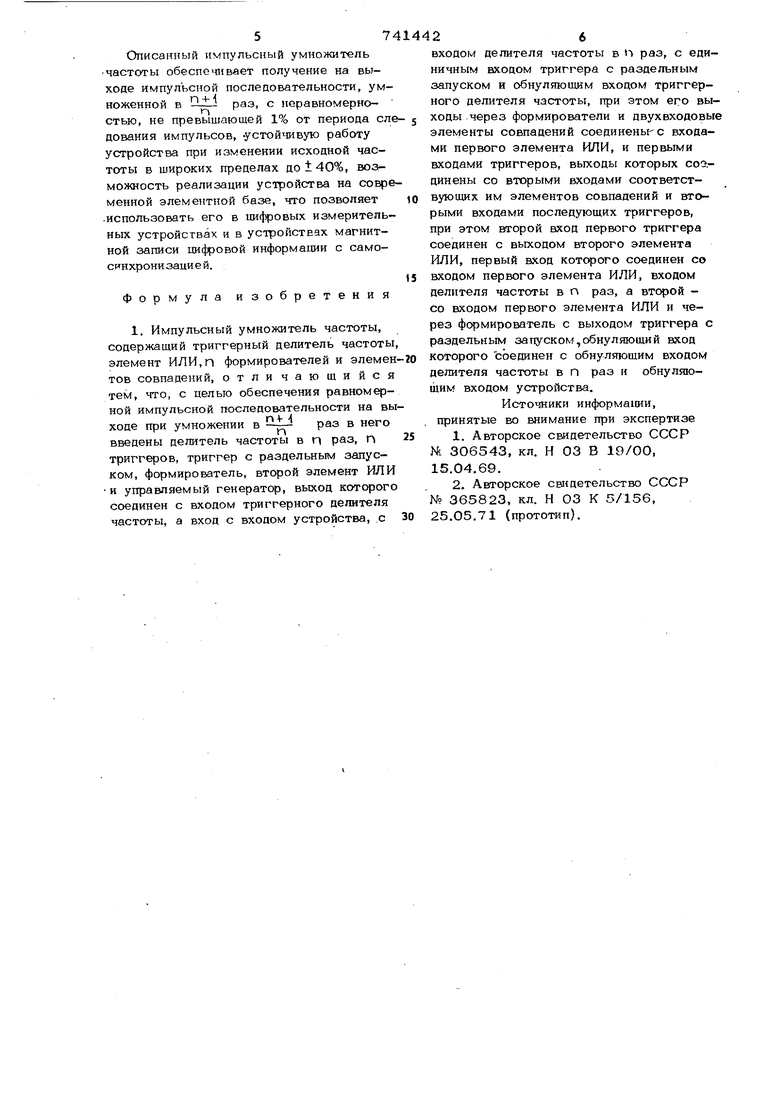

Изобретение относится к импульсной технике и может быть использовано для умножения частоты следования импульсов в измерительных устройствах, Известны импульсные умножители час тоты, позволяющие производить умножение частоты следования импульсов в широком диапазоне изменения исходной частоты в целое число раз 1 . Наиболее близким по технической сущ ности является дискретный умномдатель частоты, содер-жащий элемент задержки, вход которого соединен с входом устройства и с одним из входов элемента ИЛИ триггерный делитель частоты, вход которого соединен с выходом элемента задерж ки, а выходы через последовательно соединенные формирователи и элементы совпадений - с остальными входами элемента ИЛИ, при этом вторые входы элементов совпадений соединены с выходом прог раммного устройства . Это устройство, позволяя умножать исходную частоту следования импульсов в дробное число раз, не обеспечивает равномерность выходной последовауельности импульсов, а это сужает область его применения, не позволяя использовать известный умножитель в измерительных и других устройствах. Цель изобретения - обеспечение формирования равномерной импульсной последовательности на выходе устройства при умнолдании исходной частоты в раз и широких пределах ее изменения. Это достигается тем, что в импульсный умножитель частоты, содержащий триггерный делитель частоты, элемент ИЛИ,п формирователей и элементов сов падений,введены управляемый генератор. включенный между юсодом устройства и входом триггерного делителя частоты, П триггеров, выходы которых соединены с входами соответствующих им элементов совпадений и вторыми входами последующих триггеров, а первые входы с выходами элементов совпадений, триггер с раздельные запуском, включенный 37 между входом устройства и формирователем, делитель частоты в п раз и элемент ИЛИ, входы которого соединены с входами первого элемента ИЛИ и выходами формирователя и целителя частоты в г раз, а выход - со вторым входом пер вого из п триггеров, при этом вход целителя частоты в п раз соединен с входом устройства и обнуляющим входом делителя частоты, а обнуляющий вход триггера с раздельным запуском соединен с обнуляюищм входом делителя частоты в г раз и обнуляюишм входом устройства. На фиг. 1 показана функциональная сх ма описываемого умножителя частоты; на фиг. 2 - временные диаграммы поясняющие его работу. Импульсный умножитель частоты содер жит делитель 1 частоты в п раз, управляемый генератор 2, триггер 3 с раздельным запуском, целитель 4 частоты п формирователей 5, i элементов 6 совпадений, первый элемент 7 ИЛИ, п триг геров 8, второй элемент 9 ИЛИ и форми рователь 10. Выход первого элемента ИЛИ является выходом устройства. Для упрощения рассмотрим работу уст ройства для г 3. Входная импульсная последовательность (фиг. 2а) поступает на вход управляемого генератора 2, частота следования импульсов на выходе которого paBHanL (фиг. 25), -частота следования импульсов на входе управляемого генератора, а также на вход дега1теля 1 частоты в 3 раза. Коэффициент гп выбирается равны мГп--к(), где у - целое положительное число. Для рассматриваемого примера приме И 2, т.е., причем вместо управляемого генератора 2 может быть использован умножитель частоты в целое число раз. С выхода управляемого генератора 2 импульсная последовательность (фиг. 2 поступает на триггерный делитель 4 час тоты. На формирователи 5 импульсы пос

тупают с соответствую ишх плеч триггеров триггерного делителя 4 таким образом, что на выходах формирователей 5 формируются импульсные последовательности (фиг. 2Ь,г,а ) импульсы которых отстоят соответственно на t , К (п-1), (п-2) от импульса управляемого генератора 2 (отсчет производится после обнуления триггорпого целителя 4 входной импульсной последовательности фиг, 2а).

Далее эти импульсы (фиг, 2В,г,g) поступают на свои двухвходовые элементы 6

8 и обеспечивая прохождение второго импульса (фиг. 2А) через элемент 6 совпадений на один из входов первого элемента 7 ИЛИ. Второй импульс в свою очередь устанавливает триггер 8 в исходное состояние (фиг. 2з). Далее процесс повторяется с той лишь разницей, что на вход триггера 8 начинают поступат(з импульсы (фиг, 2р) с целителя 1 частоты в Ю раз. На выходы первого элемента 7 ИПИ формируется ум1 оже1П1ая в -- - л раз импульсная послоцовательиость (фиг. 2п), 2 совпадений, на вторые входы которых поступают импульсы (фиг. 2е,-А,, з) с триггеров 8, которые разрешают прохождение через элементы G совпадений импульсных последовательностей (фиг. 2n,K,N). Для подготовки схемы к работе на обнуляющий вход триггера 3 с раздельным запуском поступает внешний обнуляющий импульс (фиг. 2м), который переводит триггер 3 с раздельным запуском (фиг, 2 и ) в исходное положение и обнуляет делитель 1 частоты в п раз. Внешний обнуляюший импульс (фиг. 2м) поступает перед первым импульсом входной импульсной последовательности, В этот момент, когда первый импульс входной импульсной последовательности (фиг. 2а) произведет переключение триггера 3 с раздельным запуском, на выходе формирователя 10 образуется импульс (фиг, 2о), который поступает на один из входов первого элемента 7 ИЛИ для получения на его выходе импульса, соответствующего первому импульсу входной последовательности (фиг, 2а), который будет также первым импульсом умноженной импульсной последовательности (фиг. 2п ), а также поступает через второй элемент 9 ИЛИ на один из входов триггера 8, обеспечивая подготовку его к работе (фиг. 2е). Триггер 8 разрешает прохождение шестого импульса (фиг. 2и) через элемент 6совпадений на вход первого элемента 7ИЛИ. Шестой импульс с выхода элемента 6 совпадений возвращает триггер 8в исходное состояние (фиг. 2е), одновременно переключая (фиг, 2ж), следующий триггер 8 и разрешая прохождение четвертого импульса (фиг, 2к) через элемент 6 совпадений. С выхода элемента 6 совпадений четвертый импульс (фиг, 2) поступает на один из входов первого элемента 7 ИЛИ и устанавливает триггер 8 в исходное состояние (фиг. 2ж), переключая (фиг, 2з) следующий триггер Описанный импульснь1й умножитель Частоты обеспечивает получение на выходе импульсной последовательности, умноженной в Q-il раз, с неравномерно- стью, не превышающей 1% от периода ел дования импульсов, -устойчивую работу устройства при изменении исходной частоты в широких пределах до 140%, возможность реализации устройства на совре менной элементной базе, что позволяет .использовать его в цифровых измерительных устройствах и в устройствах магнитной записи цифровой информации с самосинхронизацией. Формула изобретения 1. Импульсный умножитель частоты, содержащий триггерный делитель частоты элемент ИЛИ,п формирователей и элемен тов совпадений, отличаюшийся тем, что, с целью обеспечения равномерной импульсной последовательности на вы п V ходе при умножении в -- раз в него введены делитель частоты в п раз, П триггеров, триггер с раздельным запуском, формирователь, второй элемент ИЛИ и управляемый генератор, выход которого соединен с входом триггерного делителя частоты, а вход с входом устройства, .с входом делителя частоты в п раз, с единичным входом триггера с раздельным запуском и обнуляющим входом триггер- ного делителя частоты, при этом его выходы через формирователи и двухвходовые элементы совпадений соединены-с входами первого элемента ИЛИ, к первыми входами триггеров, выходы которых соэ,динены со вторыми входами соответствующих им элементов совпадений и вторыми входами последующих триггеров, при этом второй вход первого триггера соединен с вьтходом второго элемента ИЛИ, первый вход которого соединен со входом первого элемента ИЛИ, входом делителя частоты в п раз, а второй со входом первого элемента ИЛИ и через формирователь с выходом триггера с раздельным за пуском, обнуляющий вход которого соединен с обнуляющим входом делителя частоты в п раз и обнуляющим входом устройства. Источники информа1ши, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Nt ЗО6543, кл. Н 03 В 19/00, 15.04,69. 2.Авторское свидетельство СССР N 365823, кл. Н 03 К 5/156, 25.05.71 (прототип). У uц-и-Т 1-:---- пллшллпллллшшшштогщпшшшии «

1 иииу--и1Г

Фиа.2 У и- ---

Авторы

Даты

1980-06-15—Публикация

1977-11-09—Подача