Изобретение относится к области вычислительной и измерительной техники и может быть использовано для предварительного умножения частотно-импульсных сигналов на коэффициент, больший единицы с целью увеличения статической и динамической точности последукших частотомеров а также в качестве масштабного блока в частотно-импульсных вычислительных устройствах.

Известны умножители частотно- импульсных сигналов, содержащие устройство задержки импульсов, коммутирующий триггер, делитель частоты блок сравнения периодов, реверсивный счетчик, преобразователь код-напряжение, генератор управляемой частоты и схемы совпадения

WОднако точность преобразования в них недостаточна.

Наиболее близким к изобретению по технической сущности и достигаемому эффекту является умножитель частоты потока вмпульсов, содержащий последовательно соединенные : реверсивный счетчик, преобразователь код-напряжение, генератор управляемой частоты, цепь обратной связи и блок сравнения периодов, второй вход которого связан со вторым входом цепи об штной связи и с выходо блока синхронизации, первым входом подключенного к выходу генератора управляемой частоты, вторым - к входу устройства, а также два элемента совпадения, подключенные к входам реверсивного счетчика Г2| .

Недостатком этого устройства является неустойчивая работа в области низких частот.

Целью изобретения является расширение диапазона умножаемых частот.

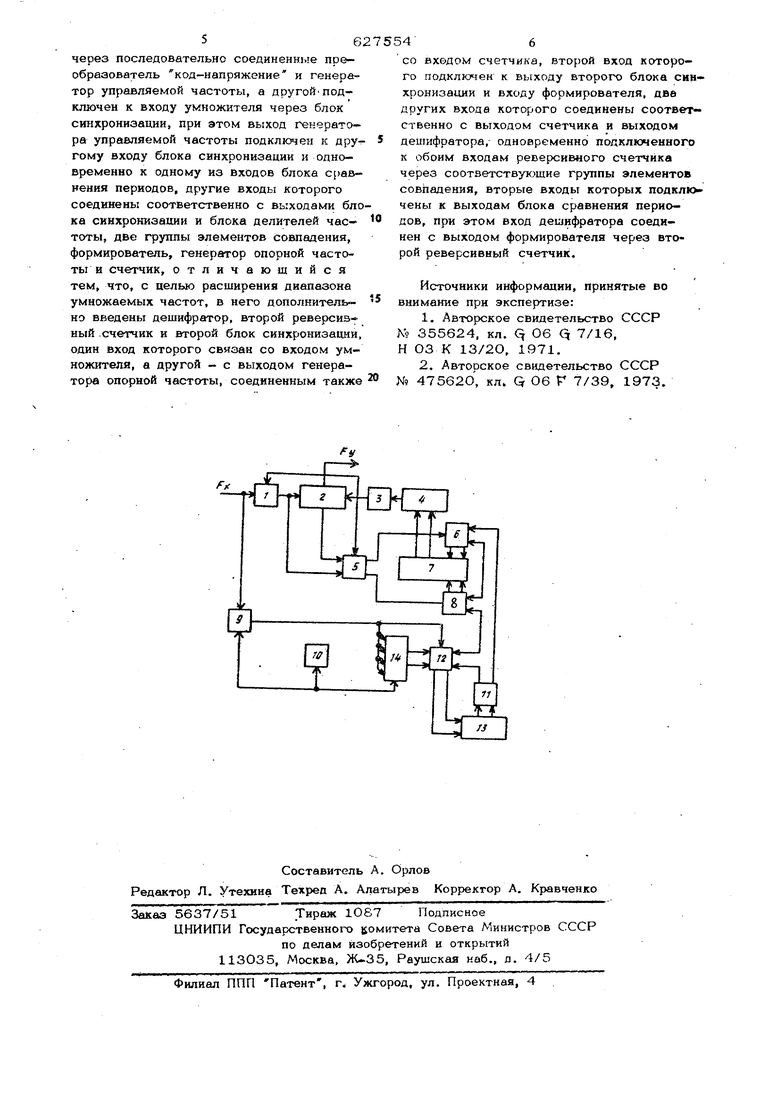

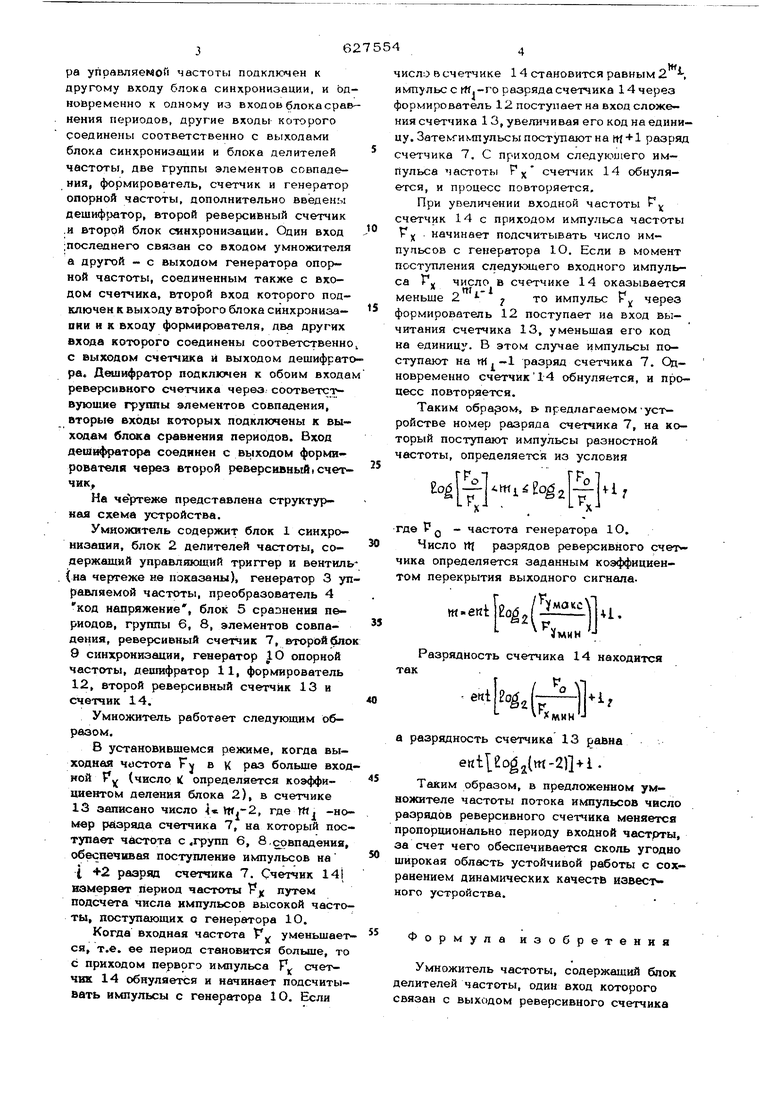

Эта цель достигается засчет того, что в умножитель частоты, содержащий блок делителей частоты, одиш вход -которого связан с выходом реверсивного счетчика через последовательно сиедмнеиные преобразователь код-напряжение и генератор управляемой частоты, а другой подключен к входу умножителя через блок сиихронизадии, при этом выход генераточ pa управляемой частоты подключен к другому входу блока синхронизации, и опнойременно к одному из входов блокасрав нения периодов, другие входы которого соединены соответственно с выходами блока синхронизации и блока делителей частоты, две группы элементов совпадения, формирователь, счетчик и генератор опорной частоты, дополнительно введены дешифратор, второй реверсивный счетчик .и второй блок синхронизации. Один вход ;последнего связан со входом умножителя а другой с выходом генератора опорной частоты, соединенным также с входом счетчика, второй вход которого подключен к выходу вто{эого блока синхронизапки и к входу формирователя, два других входа которого соединены соответственно с выходом счетчика и выходом дешифрато ра. Дешифратор подключен к обоим входа реверсивного счетчика через соответствующие группы элементов совпадения, вторые входы которых подключены к выходам блсжа сравнения периодов. Вход дешифратора соединен с выходом формирователя через второй реверсивный i счетчик. На че ртеже представлена структурнвя схема устройства. Умножитель содержит блок 1 синхронизации, блок 2 делителей частоты, содержащий управляющий триггер и вентиль (иа чертеже не показаны), генератор 3 уп равляемой частоты, преобразователь 4 код напряжение , блок 5 сравнения периодов, группы 6, 8, элементов совпадения, реверсивный счетчик 7, второй бло 9 синхронизации, генератор 10 опорной частоты, децгафратор 11, формирователь 12, второй реверсивный счетчик 13 и счетчик 14. Умножитель работает следующим образом. В установившемся режиме, когда выходная чостота TV в К раз болыые вхо ной У (число tL определяется коэффициентом деления блока 2), в счетчике 13 записано число « Wj-2, где W, -но мер разряда счетчика 7, на который пос тупает частота с .групп 6, 8,совпадения обеспечивая поступление импульсов на I +2 разряд счетчика 7. Счетчик 141 намеряет период частоты Pjj путем подсчета числа импульсов высокой часто ты, поступающих о генератора 1О. Когда входная частота V уменьщает ся, т.е. ее период становится больше, то с приходом первого импульса Г счетчик 14 обнуляется и начинает подсчитывать импульсы с генератора 10. Если исло в счетчике 14 становится равным 2 мпульсе т.-го разряда счетчика 14 через ормирователь 12 поступает на вход сложеия счетчика 13, увеличивая его код на единицу. Зaтe fикfflyльcы поступают на tt/+l разряд четчика 7. С приходом следуюи1его импульса частоты РХ счетчик 14 обнуляется, и процесс повторяется. При увеличении входной частоты счетчик 14 с приходом импульса частоты V начинает подсчитывать число импульсов с генератора 1О. Если в момент поступления следукмиего входного импуль- 14 оказывается са } ., число в счетчике меньше iC то импульс Ь j через формирователь 12 поступает на вход вычитания счетчика 13, уменьшая его код на единицу. В этом случае импульсы поступают на tKi-1 разряд счетчика 7. Одновременно счетчик14 обнуляется, и процесс повторяется. Таким обраром, в-предлагаемом-устройстве номер разряда счетчика 7, на который поступают импульсы разностной частоты, определяется из условия ЕоЛ.т,.ео,И.1; L . L -xJ где PQ - частота генератора 10. Число щ разрядов реверсивного счетчика определяется заданным коэффициентом перекрытия выходного сигнала. . гумоксХ 1, . Ыин f Разрядность счетчика 14 находится - Ф, мин а разрядность счетчика 13 равна ,(т-2). Таким образом, в предложенном умножителе частоты потока импульсов число разрядов реверсивного счетчика меняется пропорционально периоду входной частрты, за счет чего обеспечивается сколь угодно широкая область устойчивой работы с сохранением динамических качеств иавестного устройства. Формула изобретения Умножитель частоты, содержащий блок делителей частоты, один вход которого связан с выходом реверсивного счетчика через последовательно соединенные преобразователь код-напряжение и генератор управляемой частоты, а другойподключен к входу умножителя через блок синхронизации, при этом выход генератора управляемой частоты подключен к дру гому входу блока синхронизации и одновременно к одному из входов блока сравнения периодов, другие входы которого соединены соответственно с выходами бл ка синхронизации и блока делителей частоты, две группы элементов совпадения, формирователь, генератор опорной частоты и счетчик, отличающийся тем, что, с целью расширения диапазона умножаемых частот, в него дополнительно введены дешифратор, второй реверсивный .счетчик и второй блок синхронизации один вход которого связан со входом умножителя, а другой - с выходом генератора опорной частоты, соединенным также со входом счетчика, второй вход которого подключен к выходу второго блока синхронизации и входу формирователя, два других входа которого соединены соответственно с выходом счетчика и выходом деишфратора,- одновременно подключенного к обоим входам реверсивного счетчика через соответствующие группы элементов совпадения, вторые входы которых подклк чены к выходам блока сравнения периодов, при этом вход дешифратора соединен с выходом формирователя через второй реверсивный счетчик. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 355624, кл. :, Об Q 7/16, Н 03 К 13/20, 1971. 2.Авторское свидетельство СССР 475620, кл. Q Об Г 7/39, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство одноканального фазового управления вентильным преобразователем | 1974 |

|

SU674182A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Преобразователь перемещений в код | 1978 |

|

SU746652A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Широкополосный умножитель частоты следования импульсов | 1979 |

|

SU855934A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

го

Авторы

Даты

1978-10-05—Публикация

1974-08-21—Подача