входу третьего счетчика, второму входу первого элемента ИЛИ, счетный вход третьего счетчика подсоединен к выходу второго делителя частоты, а выход третьего счетчика подключен к первому входу первого регистра памяти, второй вход синхронизатора, первьй вход первого счетчикд, первый вход второго счетчика и первый вход блока коррекции подключены к выходу генератора тактовых импульсов, вьпсод синхронизатора соединен с вторым входом блока коррекции, с входом блока выделения второго импульса, с вторыми входами первого счетчика, третьего триггера, четвертого элемента совпадения и второго счетчика, входом блока выделения первого импульса, с входом элемента задержки, с третьим входом сумматора, первым входом второго регистра памяти и вторым входом первого регистра памяти, второй вход четвертого триггера объединен с первым входом пятого триггера, второй вход которого соединен с вторым установочным входом пятого счетчика и с вькодом второго делителя частоты, счетный вход пятого счетчика подключен к выходу второго элемента совпадения, выход четвертого элемента совпадения подключен к в.торому входу второго элемента ИЛИ, выход которого подключен также к второму входу второго триггера, выход третьего элемента совпадения соединен с входом четвертого счетчика, выход которого подключен к третьему входу Третьего блока переноса кода, при |этом выход третьего элемента ИЛИ является выходом цифрового умножителя частоты.

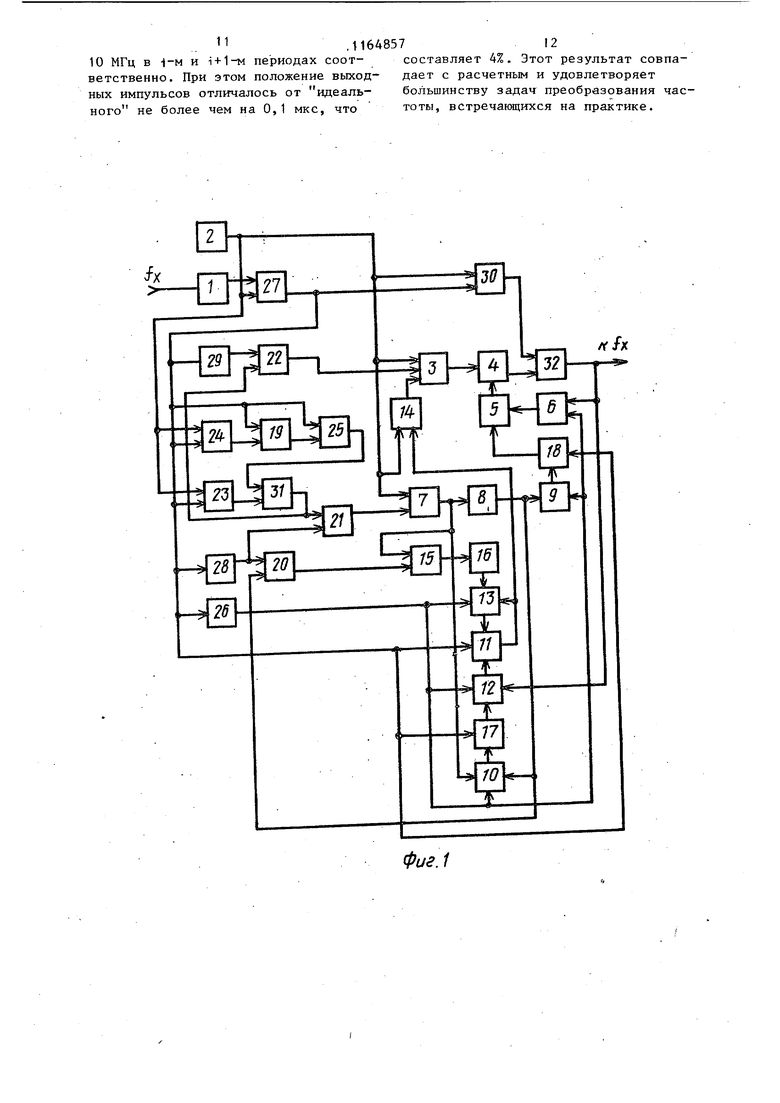

I 2. Умножитель частоты по п. 1, отличающийся тем, что блок коррекции выполнен в виде последовательно соединенных счетчика, регистра памяти, сумматора и элемента совпадения, выход которого является выходом блока коррекции, при этом первый вход счетчика является первым входом блока коррекции, другой вход сумматора объединен с входом регистра памяти, вторые входы счетчика, регистра памяти и элемента совпадения объединены и являются вторым входом блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Умножитель частоты следования периодических импульсов | 1981 |

|

SU1012247A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1290313A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

1. ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ, содержащий последовательно соединенные формирователь импульсов, вход которого является входом цифрового умножителя частоты, и синхронизатор, последовательно соединенные генератор тактовых импульсов, первый элемент совпадения и первый делитель частоты,- последовательно соединенные второй элемен-г совпадения, первый вход которого подключен к выходу генератора тактовых импульсов, и второй делитель частоты, последовательно соединенные первый регистр памяти и первый блок переноса кода, выход которого соединен с другим входом первого делителя частоты, последовательно соединенные второй регистр памяти, второй блок переноса кода и сумматор, к второму входу которого подсоединен выход третьего блока переноса кода, первый элемент ИЛИ и первый триггер, при этом выход первого элемента ИЛИ подключен к второму входу первого блока переноса кода, выход сумматора подключен к первому входу третьего блока переноса кода и к первому входу .первого триггера, второй вход которого подключен к выходу генератора тактовых импульсов, а выход которого подсоединен к второму входу первого элемента совпадения, третий элемент совпадения, первый вход которого подключен к выходу второго элемента сов-, падения, четвертый элемент совпадения, отличающийся тем, что, с целью повьшения точности умножения частоты, введены последовательно соединенные блок выделения второго импульса и второй триггер, выход которого подключен к третьему вхо.ду первого элемента совпадения, последовательно соединенные первый счетчик и третий триггер, выход которого подключен к первому входу четвертого (Л элемента совпадения, последовательно соединенные второй счетчик, второй элемент ИЛИ и четвертый триггер, выход которого подключен к второму входу второго элемента совпадения, последовательно соединенные блок выделения первого импульса и пятый 05триггер, выход которого подключен к 4; второму входу третьего элемента совоо падения, элемент задержки, третий, СП четвертый и пятый счетчики, последоvj вательно соединенные блок коррекции и третий элемент ИЛИ, второй вход которого подключен к выходу первого делителя частоты, а выход которого соединен с первым входом первого элемента ИЛИ и с вторым входом -второго блока переноса кода, при этом выход элемента эадержки подключен к второму входу третьего блока переноса кода, к третьему входу второго блока переноса кода, перввму установочному входу пятого счетчика, установочному

1

Изобретение относится к электросвязи, а также к измерительной и вычислительной технике и может быть использовано в информационно-измерительных системах различного назначения, в частности при создании высокоточных умножителей частоты.

Целью изобретения является повышение точности умножения частоты.

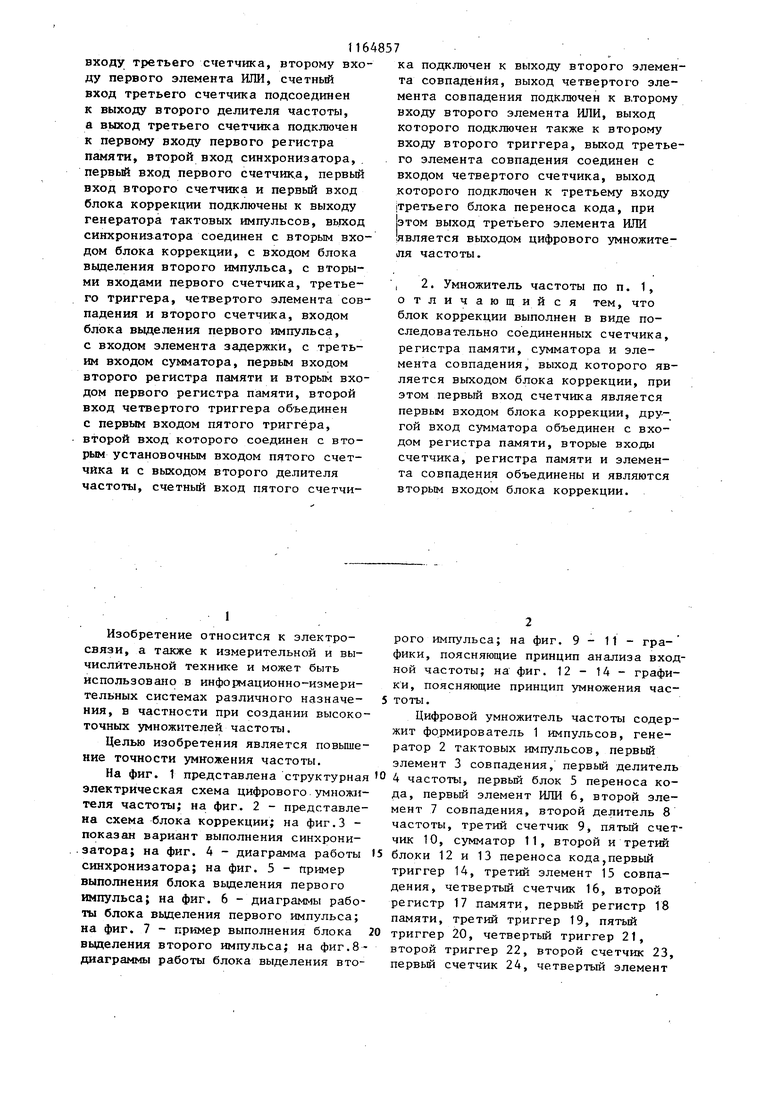

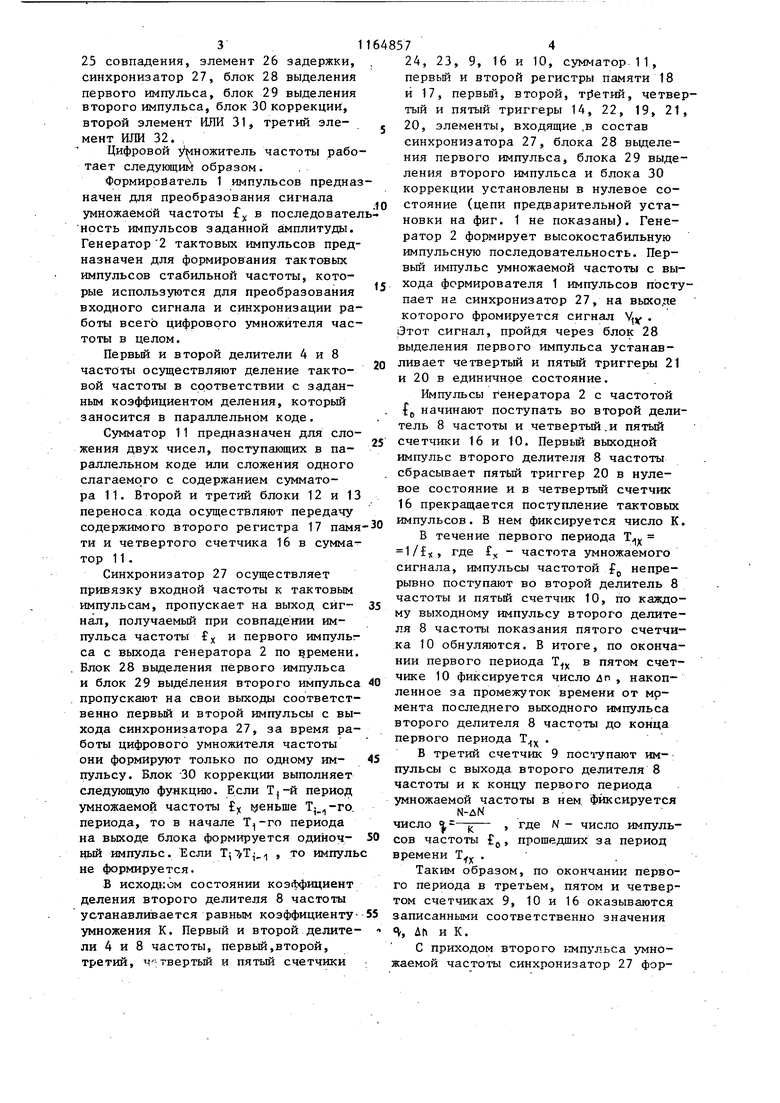

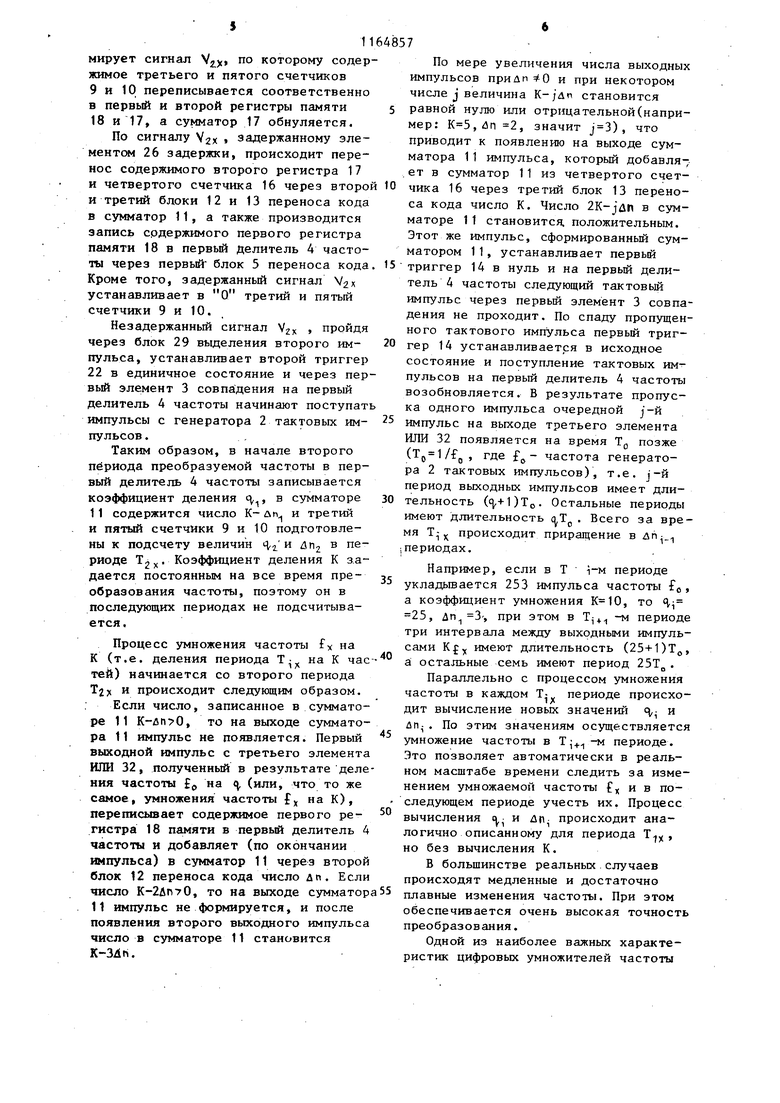

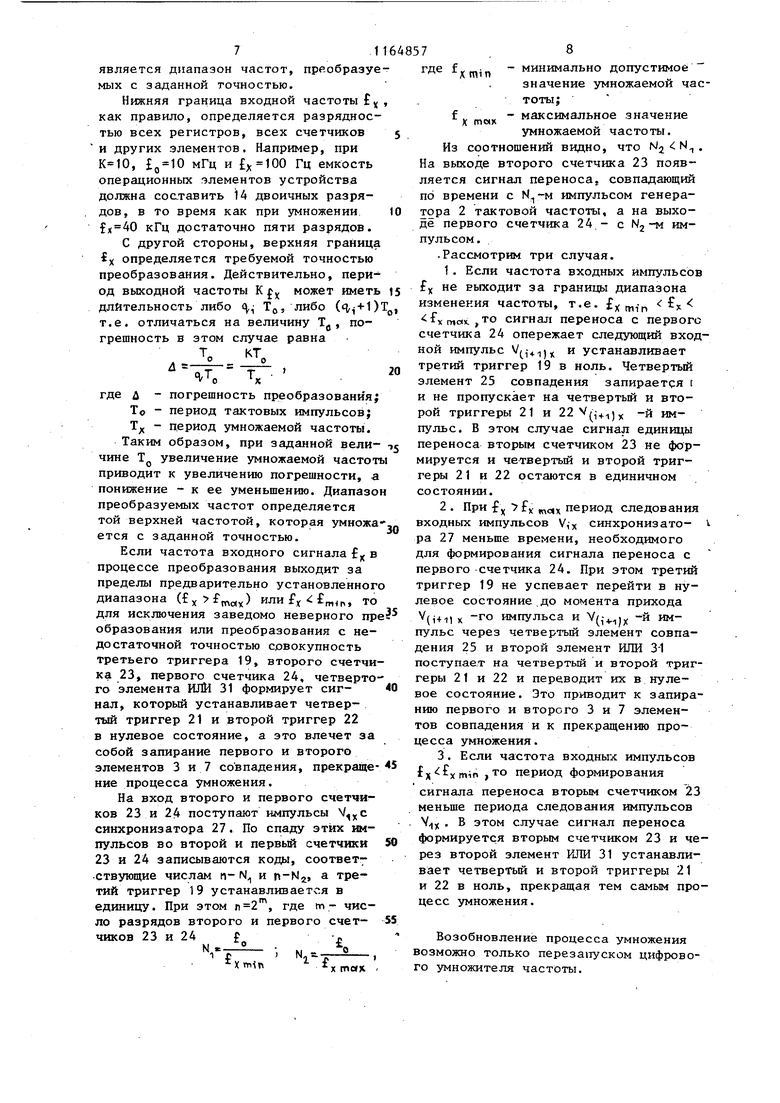

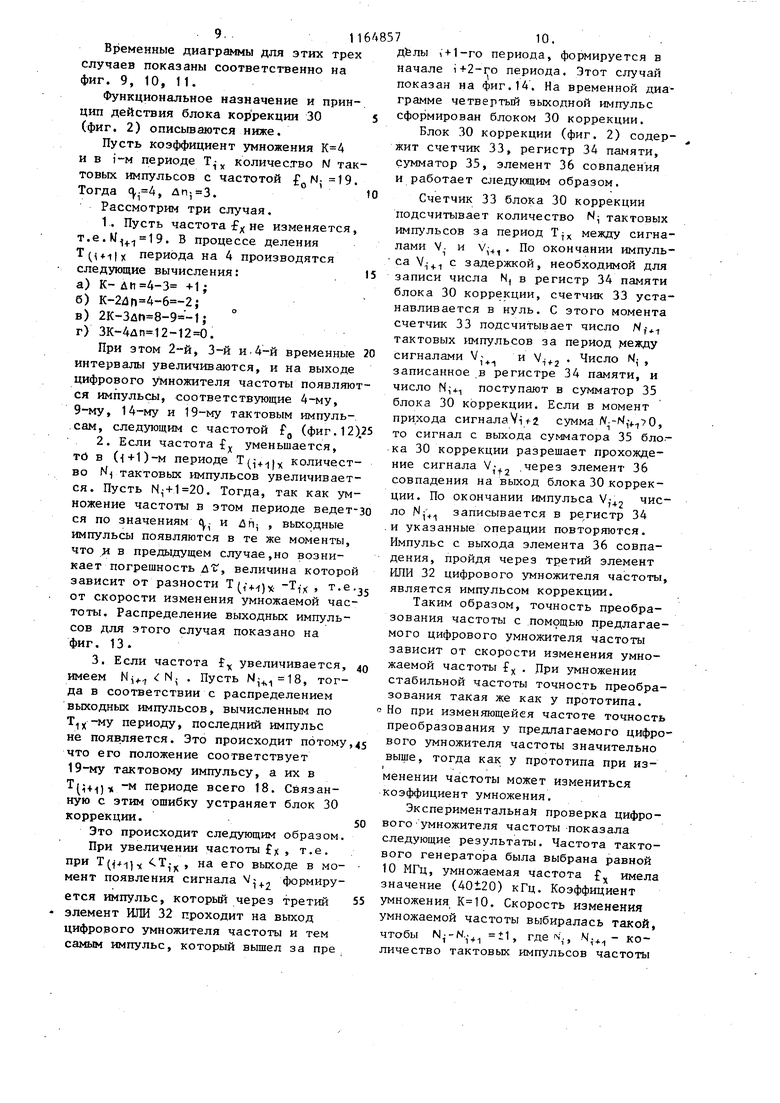

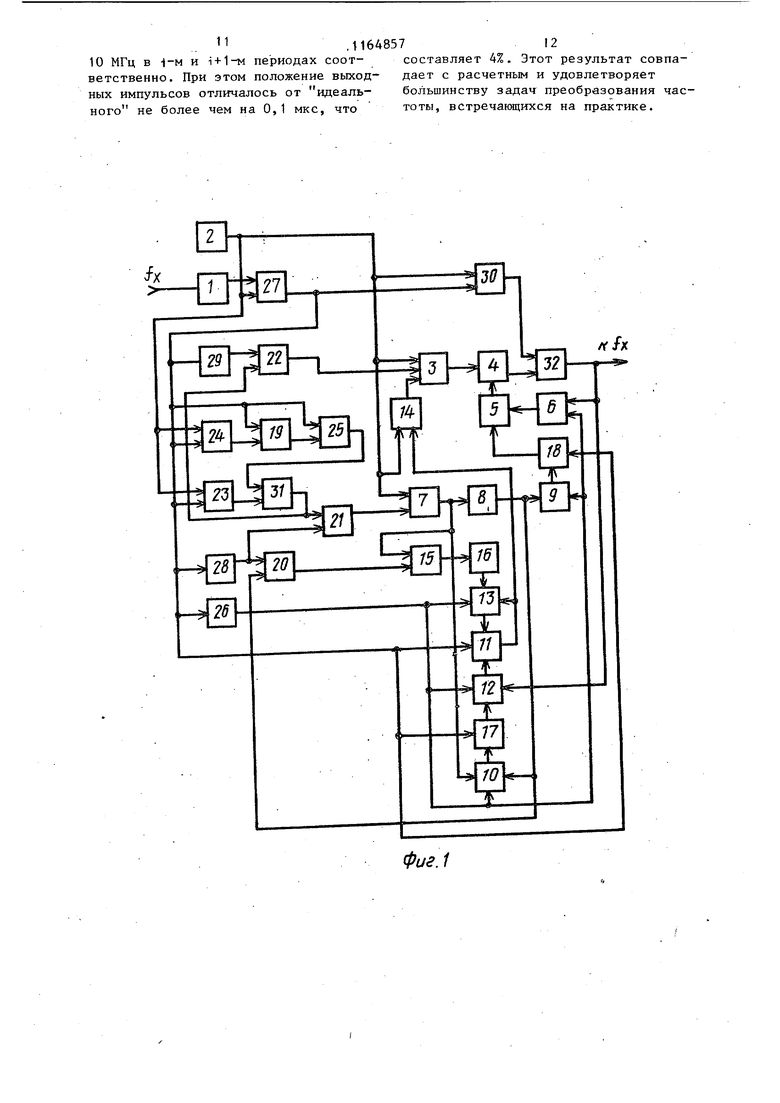

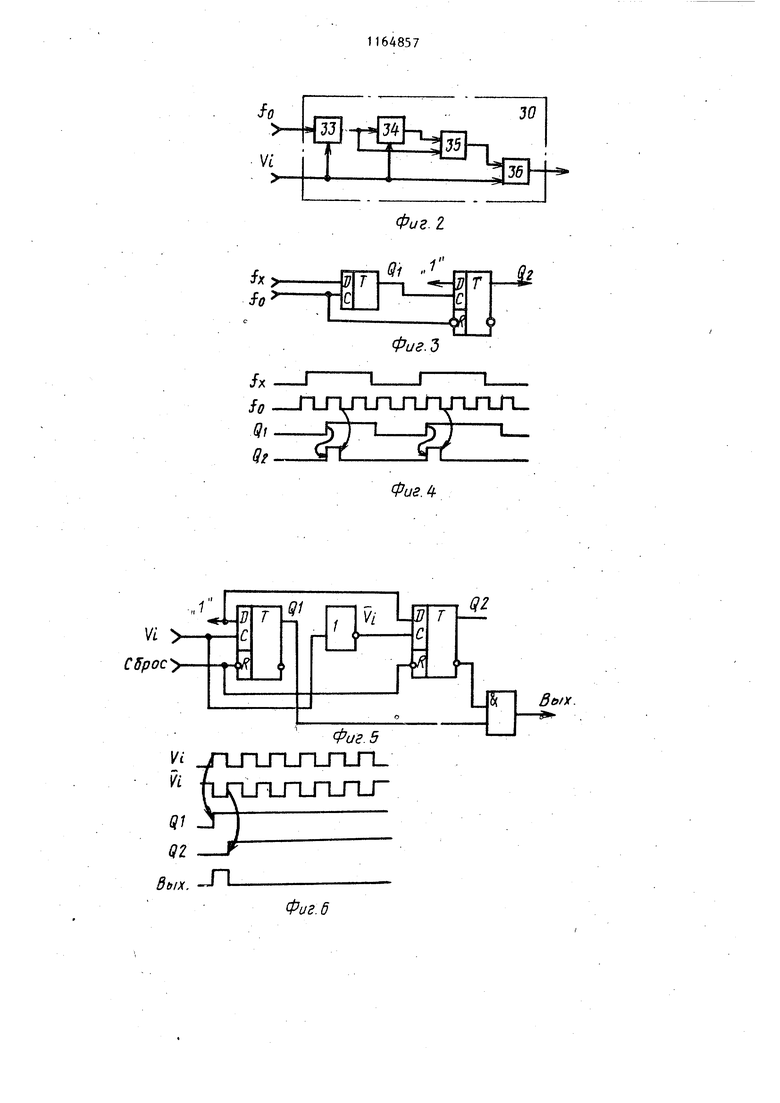

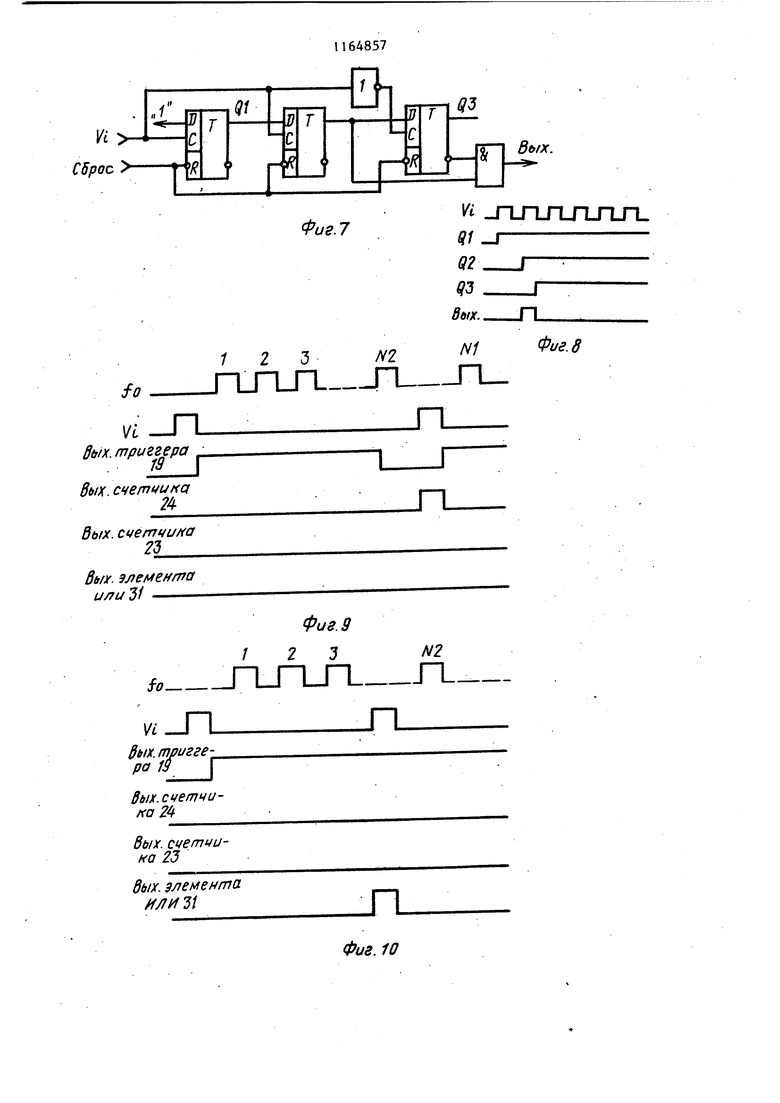

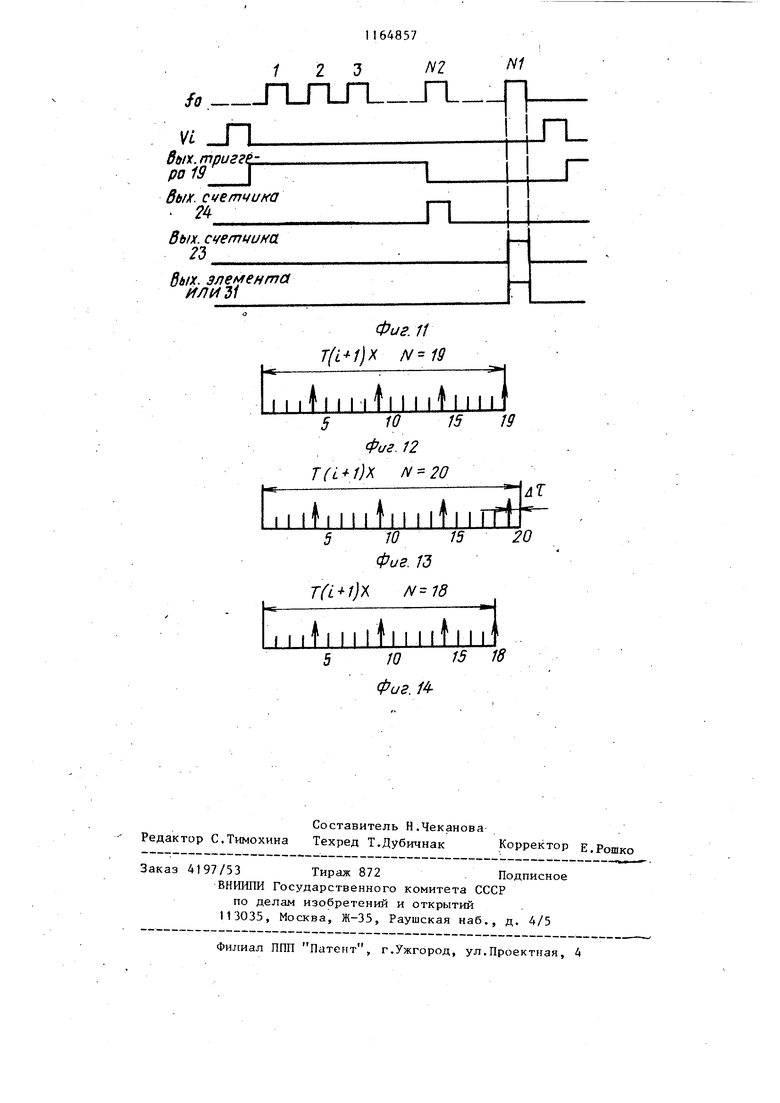

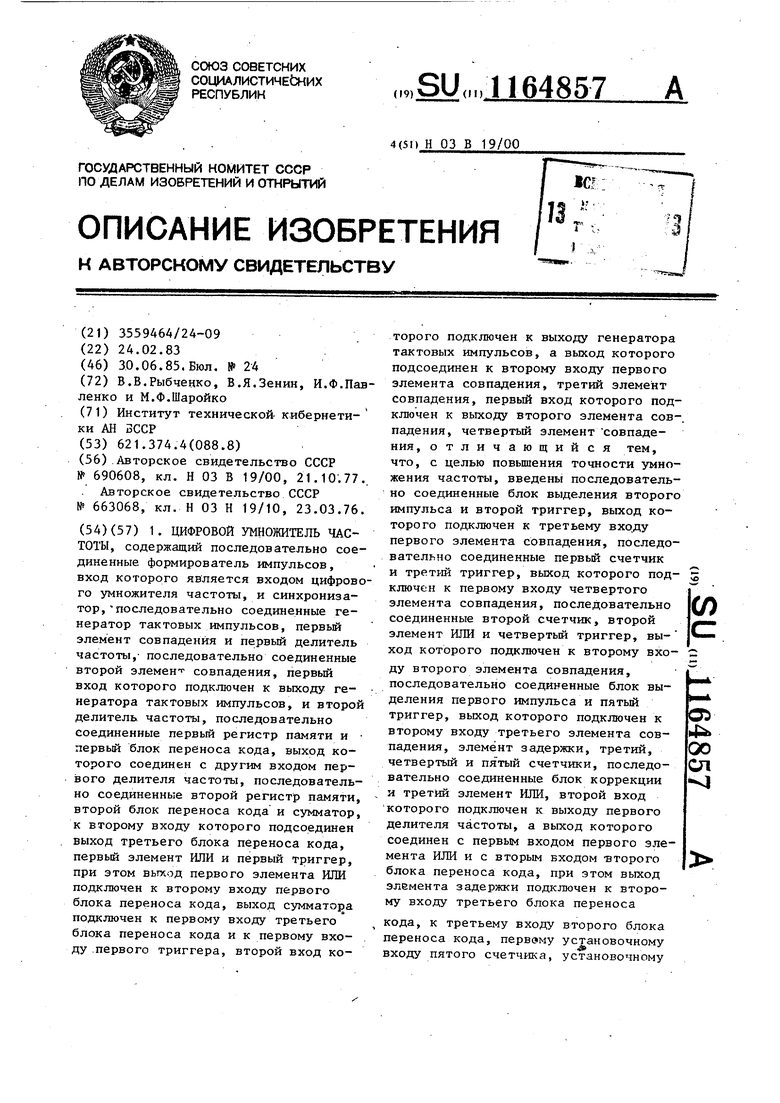

На фиг. 1 представлена структурная электрическая схема цифрового умножителя частоты; на фиг. 2 - представлена схема блока коррекции; на фиг.З показан вариант выполнения синхрони.затора; на фиг. 4 - диаграмма работы синхронизатора; на фиг. 5 - пример выполнения блока выделения первого импульса; на фиг. 6 - диаграммы работы блока выделения первого импульса; на фиг. 7 - пример выполнения блока вьщеления второго импульса; на фиг.8диаграммы работы блока выделения второго импульса; на фиг. 9 - 11 - графики, поясняющие принцип анализа входной частоты; на фиг. 12 - 14 - графики, поясняющие принцип умножения частоты.

Цифровой умножитель частоты содержит формирователь 1 импульсов, генератор 2 тактовых импульсов, первьй элемент 3 совпадения, первый делитель 4 частоты, первьй блок 5 переноса кода, первьй элемент ИЛИ 6, второй элемент 7 совпадения, второй делитель 8 частоты, третий счетчик 9, пятый счетчик 10, сумматор 11, второй и третий блоки 12 и 13 переноса кода,первый триггер 14, третий элемент 15 совпадения, четвертьй счетчик 16, второй регистр 17 памяти, первьй регистр 18 памяти, третий триггер 19, пятьй триггер 20, четвертьй триггер 21, второй триггер 22, второй счетчик 23, первьй счетчик 24, четвертьй элемент 25 совпадения, элемент 26 задержки, синхронизатор 27, блок 28 выделения первого импульса, блок 29 выделения второго импульса, блок 30 коррекции, второй элемент ИЛИ 31, третий элемент ИЛИ 32. Цифровой умножитель частоты рабо тает следующим образом. Формирователь 1 импульсов предна начен для преобразования сигнала умножаемой частоты в последовате ность импульсов заданной амплитуды. Генератор 2 тактовых импульсов предназначен для формирования тактовых импульсов стабильной частоты, которые используются для преобразования входного сигнала и синхронизации работы всего цифрового умножителя частоты в целом. Первый и второй делители 4 и В частоты осуществляют деление тактовой частоты в соответствии с заданным коэффициентом деления, который заносится в параллельном коде. Сумматор 11 предназначен для сложения двух чисел, поступающих в параллельном коде или сложения одного слагаемого с содержанием сумматора 11. Второй и третий блоки 12 и 13 переноса кода осуществляют передачу содержимого второго регистра 17 памя ти и четвертого счетчика 16 в сумматор 11 . Синхронизатор 27 осуществляет привязку входной частоты к тактовым импульсам, пропускает на выход сигнал, получаемый при совпадении импульса частоты х первого импулы са с выхода генератора 2 по чремени Блок 28 вьщеления первого импульса и блок 29 выделения второго импульса пропускают на свои выходы соответственно первый и второй импульсы с выхода синхронизатора 27, за время работы цифрового умножителя частоты они формируют только по одному импульсу. Блок -30 коррекции выполняет следующую фуякцию. Если период умножаемой частоты j( уеньше Tj.-ro. периода, то в начале периода на выходе блока формируется одиночный импульс. Если . , то импуль не формируется. В исходном состоянии коэффициент деления второго делителя 8 частоты устанавливается равным коэффициенту умножения К. Первый и второй делители 4 и 8 частоты, первый,второй, третий. Ч-твертый и пятый счетчики 24, 23, 9, 16 и 10, сумматор.11, первьй и второй регистры памяти 18 и 17, первый, второй, Т15етий, четвертый и пятый триггеры 14, 22, 19, 21, 20, элементы, входящие ,в состав синхронизатора 27, блока 28 выделения первого импульса, блока 29 выделения второго импульса и блока 30 коррекции установлены в нулевое состояние (цепи предварительной установки на фиг. 1 не показаны). Генератор 2 формирует высокостабильную импульсную последовательность. Первый импульс умножаемой частоты с выхода формирователя 1 импульсов поступает на синхронизатор 27, на выходе которого фромируется сигнал V,y . Зтот сигнал, пройдя через блок 28 выделения первого импульса устанавливает четвертый и пятый триггеры 21 и 20 в единичное состояние. Импульсы Генератора 2 с частотой (, начинают поступать во второй делитель 8 частоты и четвертый.и пятый счетчики 16 и 10. Первьй выходной импульс второго делителя 8 частоты сбрасывает пятый триггер 20 в нулевое состояние и в четвертый счетчик 16 прекращается поступление тактовых импульсов. В нем фиксируется число К. В течение первого периода Tj,, 1/fx где , - частота умножаемого сигнала, импульсы частотой f непрерывно поступают во второй делитель 8 частоты и пятьй счетчик 10, по каждому выходному импульсу второго делителя 8 частоты показания пятого счетчика 10 обнуляются. В итоге, по окончании первого периода Т в пятом счетчике 10 фиксируется число лп , накопленное за промежуток времени от мрмента последнего выходного импульса второго делителя 8 частоты до конца первого периода Т, . В третий счетчик 9 пос1упают импульсы с выхода второго делителя 8 частоты и к концу первого периода умножаемой частоты в нем фиксируется число , где N - число импульсов частоты р, прошедших за период времени . Таким образом, по окончании первого периода в третьем, пятом и четвертом счетчиках 9, 10 и 16 оказываются записанными соответственно значения V, ДП и К. С приходом второго импульса умноаемой частоты синхронизатор 27 формирует сигнал ° которому содер жимое третьего и пятого счетчиков 9 и 10 переписывается соответственно в первый и второй регистры памяти 18 и 17, а сумматор 17 обнуляется. По сигналу Угх задержанному элементом 26 задержки, происходит перенос содержимого второго регистра 17 и четвертого счетчика 16 через второ и третий блоки 12 и 13 переноса кода в сумматор 11, а также производится запись содержимого первого регистра памяти 18 в первьй делитель 4 частоты через первый блок 5 переноса кода Кроме того, задержанный сигнал V2x устанавливает в О третий и пятый счетчики 9 и 10. Незадержанный сигнал Vzx пройдя через блок 29 вьщеления второго импульса, устанавливает второй триггер 22 в единичное состояние и через пер вый элемент 3 совпадения на первый делитель 4 частоты начинают поступат импульсы с генератора 2 тактовых импульсов . Таким образом, в начале второго периода преобразуемой частоты в первый делитель 4 частоты записывается коэффициент деления с,, в сумматоре 11 содержится число К-дп и третий и пятый счетчики 9 и 10 подготовлены к подсчету величин ЛПг в периоде Т2X. Коэффициент деления К задается постоянным на все время преобразования частоты, поэтому он в последующих периодах не подсчитывается. Процесс умножения частоты fx на К (т.е. деления периода Т; на К час тей) начинается со второго периода Т2 и происходит следующим образом. Если число, записанное в сумматоре 11 , то на выходе сумматора 11 импульс не появляется. Первый выходной импульс с третьего элемента ИЛИ 32, полученный в результате деле ния частоты (, на ({ (или, что то же самое, умножения частоты f на К), переписывает содержимое первого регистра 18 памяти в первый делитель 4 частоты и добавляет (по окончании импульса) в сумматор 11 через второй блок 12 переноса кода число дп. Если ЧИСЛО К-2ДГ70, то на выходе сумматор

11 импульс не формируется, и после появления второго выходного импульса число в сумматоре 11 становится К-ЗЛп. 11

обеспечивается очень высокая точность преобразования.

Одной из наиболее важных характеристик цифровых умножителей частоты 7 По мере увеличения числа выходных импульсов придп и при некотором числеjвеличина K-jdn становится равной нулю или отрицательной(например: ,dn 2, значит ), что приводит к появлению на выходе сумматора 11 импульса, который добавляет в сумматор 11 из четвертого счетчика 16 через третий блок 13 переноса кода число К. Число 2K-jun в сумматоре 1 1 становится, положительным. Этот же импульс, сформированный сумматором 11, устанавливает первый триггер 14 в нуль и на первый делитель 4 частоты следующий тактовый импульс через первый элемент 3 совпадения не проходит. По спаду пропущенного тактового импульса первый триггер 14 устанавливается в исходное состояние и поступление тактовых импульсов на первый делитель 4 частоты возобновляется. В результате пропуска одного импульса очередной j-й импульс на выходе третьего элемента ИЛИ 32 появляется на время Т позже (1 1/fjj, где f - частота генератора 2 тактовых импульсов), т.е. j-й период выходных импульсов имеет длительность (tV+OXo. Остальные периоды имеют длительность аТ . Всего за время Т- происходит приращение в лп периодах. Например, если в Т I-M периоде укладьгоается 253 импульса частоты fо, а коэффициент умножения , то 4, 25, 4п 3, при этом в . -м периоде три интервала между выходными импульсами Kff имеют длительность (25+1)1, а остальные семь имеют период 25T. Параллельно с процессом умножения частоты в каждом Т- периоде происходит вычисление новых значений я-, и лп. По этим значениям осуществляется умножение частоты в Т-ц.-м периоде. Это позволяет автоматически в реальном масштабе времени следить за изменением умножаемой частоты С и в последующем периоде учесть их. Процесс вычисления и лп происходит аналогично описанному для периода Т, но без вычисления К. В больщинстве реальных.случаев происходят медленные и достаточно плавные изменения частоты. При этом является диапазон частот, преобразуе мых с заданной точностью. Нижняя граница входной частоты как правило, определяется разрядностью всех регистров, всех счетчиков и других элементов. Например, при , мГц и Гц емкость операционных элементов устройства должна составить 14 двоичных разрядов, в то время как при умножении. кГц достаточно пяти разрядов. С другой стороны, верхняя граница х определяется требуемой точностью преобразования. Действительно, период выходной частоты К может иметь длительность либо с, Tjj, либо (ч- + О т.е. отличаться на величину Т, погрешность в этом случае равна Т- о х где и погрешность преобразования; То - период тактовых импульсов; Тд - период умножаемой частоты. Таким образом, при заданной величине Т увеличение умножаемой частот приводит к увеличению погрешности, а понижение - к ее уменьшению. Диапазо преобразуемых частот определяется той верхней частотой, которая умножа ется с заданной точностью. Если частота входного сигнала в процессе преобразования выходит за пределы предварительно установленног диапазона () ,, то для исключения заведомо неверного пр образования или преобразования с недостаточной точностью совокупность третьего триггера 19, второго счетчи ка 23, первого счетчика 24, четверто го элемента ШШ 31 формирует сигнал, которьй устанавливает четвертый триггер 21 и второй триггер 22 в нулевое состояние, а это влечет за собой запирание первого и второго элементов 3 и 7 совпадения, прекращение процесса умножения. На вход второго и первого счетчиков 23 и 24 поступают импульсы с синхронизатора 27. По спаду этих импульсов во второй и первый счетчики 23 и 24 записываются коды, соответствующие числам п-N и , а третий триггер 19 устанавливается в единицу. При этом л 2, где т- число разрядов второго и первого счет- чиков 23 и 24 N -1-3«х тел . где f,(min минимально допустимое значение умножаемой частоты;f - максимальное значение умножаемой частоты. Из соотношений видно, что ,. На выходе второго счетчика 23 появляется сигнал переноса, совпадающий по времени с Ы.-м импульсом генератора 2 тактовой частоты, а на выходе первого счетчика 24,- с Nj-м импульсом. Рассмотрим три случая. 1. Если частота входных импульсов fx выходит за границы диапазона изменения частоты, т.е. f inin х max. , то сигнал переноса с первого счетчика 24 опережает следующий входной импульс V(,-+) и устанавливает третий триггер 19 в ноль. Четвертый элемент 25 совпадения запирается t и не пропускает на четвертый и второй триггеры 21 и 22 ) -и импульс. В этом случае сигнал единицы переноса вторым счетчиком 23 не формируется и четвертый и второй триггеры 21 и 22 остаются в единичном состоянии. 2 . При f FX с, период следования входных импульсов Vix синхронизато- v pa 27 меньше времени, необходимого для формирования сигнала переноса с первого счетчика 24. При этом третий триггер 19 не успевает перейти в нулевое состояние.до момента прихода V(+, -го импульса и . -и импульс через четвертый элемент совпадения 25 и второй элемент ИЛИ 3-1 поступае.т на четвертый и второй триггеры 21 и 22 и переводит их в нулевое состояние. Это приводит к запиранию первого и второго 3 и 7 элементов совпадения и к прекращению процесса умножения. 3. Если частота входных импульсов ,то период формирования сигнала переноса вторым счетчиком 23 меньше периода следования импульсов V. В этом случае сигнал переноса формируется вторым счетчиком 23 и через второй элемент ИЛИ 31 устанавливает четвертьй и второй триггеры 21 и 22 в ноль, прекращая тем самым процесс умножения. Возобновление процесса умножения возможно только перезапуском цифрового умножителя частоты. Временные диаграммы для этих трех случаев показаны соответственно на фиг. 9, 10, 11. Функциональное назначение и принцип действия блока коррекции 30 (фиг. 2) описьшаются ниже. Пусть коэффициент з множения и в периоде Т,- количество N так товых импульсов с частотой Nj 19. Тогда ({, . Рассмотрим три случая. 1.Пусть частота ;( не изменяется, т.е. Kf 1 9. В процессе деления Т(+1|х периода на 4 производятся следующие вычисления: а)К- +1; б)К-2Л( в)2K-3flh 8-9 -1j г)ЗК-4дп 12-12 0. При этом 2-й, 3-й и.4-й временные интервалы увеличиваются, и на выходе цифрового умножителя частоты появляю ся импульсы, соответствующие 4-му, 9-му, 14-му и 19-му тактовым импуль.сам, следующим с частотой (фиг.12 2.Если частота f, уменьшается, тО в (-i+O-M периоде Т, количест во N тактовых импульсов увеличивает ся. Пусть N, + . Тогда, так как ум ножение частоты в этом периоде ведет ся по значениям ( и лп , выходные импульсы появляются в те же моменты, что ti в предыдущем случае,но возникает погрешность л f, величина которо зависит от разности T(i4-()x- Tix от скорости изменения умножаемой час тоты. Распределение выходньсх импу;льсов для этого случая показано на фиг. 13. 3. Если частота f увеличивается, имеем Njv-j Пусть Nj,18, тогда в соответствии с распределением выходных импульсов, вычисленным по периоду, последний импульс не появляется. Это происходит потому что его положение соответствует 19-му тактовому импульсу, а их в {i+llK периоде всего 18. Связанную с этим ошибку устраняет блок 30 коррекции. Это происходит следующим образом. При увеличении частоты х , т.е. при ° ькоде в момент появления сигнала . Формируется импульс, которьв через третий элемент ИЛИ 32 проходит на выход цифрового умножителя частоты и тем самым импульс, который вышел за пре дЬлы -t-1-ro периода, формируется в начале i+2-го периода. Этот случай показан на фиг.14. На временной диаграмме четвертый выходной импульс сформирован блоком 30 коррекции. Блок 30 коррекции (фиг. 2) содержит счетчик 33, регистр 34 памяти, сумматор 35, элемент 36 совпадения и работает следукнцим образом. Счетчик 33 блока 30 коррекции подсчитывает количество i тактовых импульсов за период Т между сигналами V. и V,-4, . По окончании импульса . с задержкой, необходимой для записи числа N) в регистр 34 памяти блока 30 коррекции, счетчик 33 устанавливается в нуль. С этого момента счетчик 33 подсчитывает число N,- тактовых импульсов за период между Число М , сигналами V и V,2 записанное в регистре 34 памяти, и число Nij-T поступают в сумматор 35 блока 30 коррекции. Если в момент прихода сигналаVit2 сумма ,70, то сигнал с выхода сумматора 35 блока 30 коррекции разрешает прохождение сигнала V,- .через элемент 36 совпадения на выход блока 30 коррекции. По окончании импульса V ло Nj+ записывается в регистр 34 и указанные операции повторяются. Импульс с выхода элемента 36 совпадения, пройдя через третий элемент ИЛИ 32 цифрового умножителя частоты, является импульсом коррекции. Таким образом, точность преобразования частоты с пом9щью предлагаемого цифрового умножителя частоты зависит от скорости изменения умножаемой частоты f . При умножении стабильной частоты точность преобразования такая же как у прототипа. Но при изменяющейся частоте точность преобразования у предлагаемого цифрового умножителя частоты значительно выше, тогда как у прототипа при изI,. . менении частоты может измениться коэффициент умножения. Экспериментальная проверка цифрового умножителя частоты показала следующие результаты. Частота тактового генератора была выбрана равной 10 МГц, умножаемая частота имела значение (40120) кГц. Коэффициент умножения . Скорость изменения умножаемой частоты выбиралась такой, чтобы N--N..|. 11, где., N.. - количество тактовых импульсов частоты

11,И6485712

10 МГц в и i + 1-м периодах соот-составляет 4%. Этот результат совпаветственно. При этом положение выход- дает с расчетным и удовлетворяет ных импульсов отличалось от идеаль- большинству задач преобразования часного не более чем на 0,1 мкс, что тоты, встречаннцихся на практике.

Фиг.1

/fl

-JUj-rW

Vi

30

35

Фиг. г

Q1

-Л

г

и

W и

Ql

т

CSpocytf

Ljn

.

(f

Л

/t -4 Сброс -

Q

5о/дг.

Г

Фиг.7

3

«П

/б

П

8ь1Х. триггера

fr/A. счеп1 инс( /4

. счетчима 23

/j. элемента u/7i/di

0ЫХ. т/иггера 19

Вых. ct/етчиW/4

дых. счетчина 23

бых. элемента НЛИ5

3frf/5. /

П

/23N2/V/

.

Л

п Л.

Btii. rnpuz t: pa 19

Вых. С1 етчика

. cvemvu a 2Ъ

дых. ИЛИЪ Г()Х

510 15 19 T(i + l} N 20

T{L + I))(

11 Л11 (f 11 it

л

г

п

Фиг. 11

Фиг. 12

1015

20

Фиг. 13

Н

W15 18

Фиг. /4

| Умножитель частоты | 1977 |

|

SU690608A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой умножитель частоты | 1976 |

|

SU663068A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-06-30—Публикация

1983-02-24—Подача