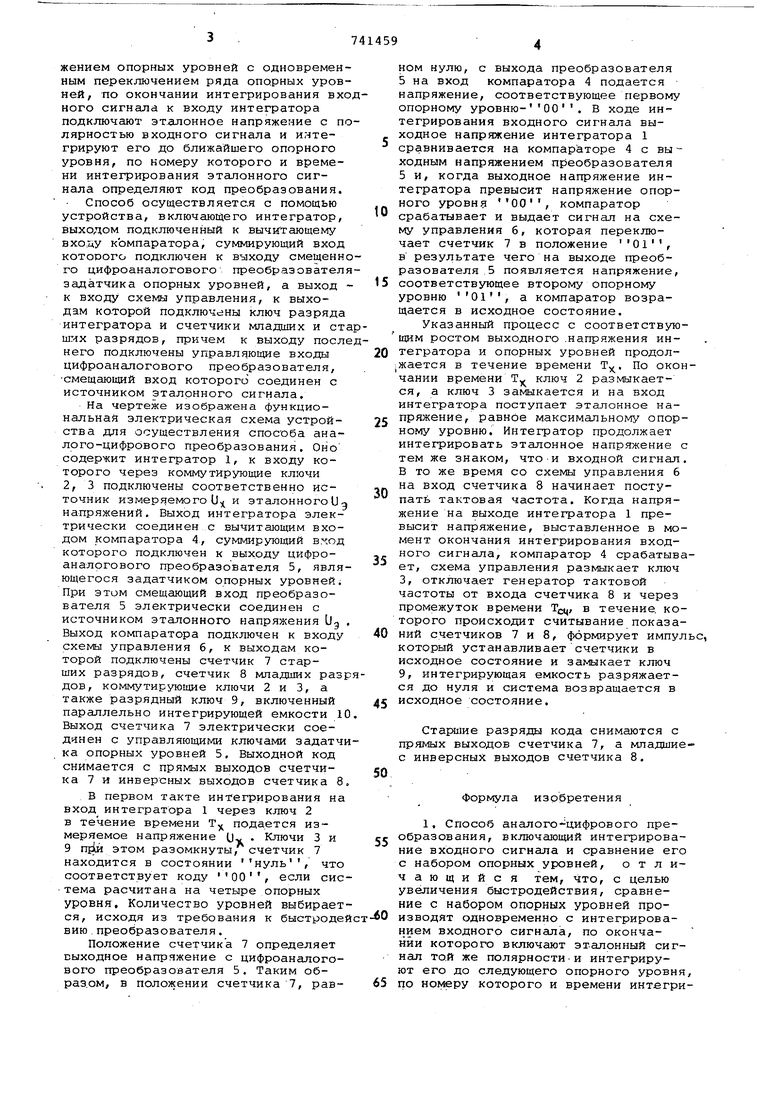

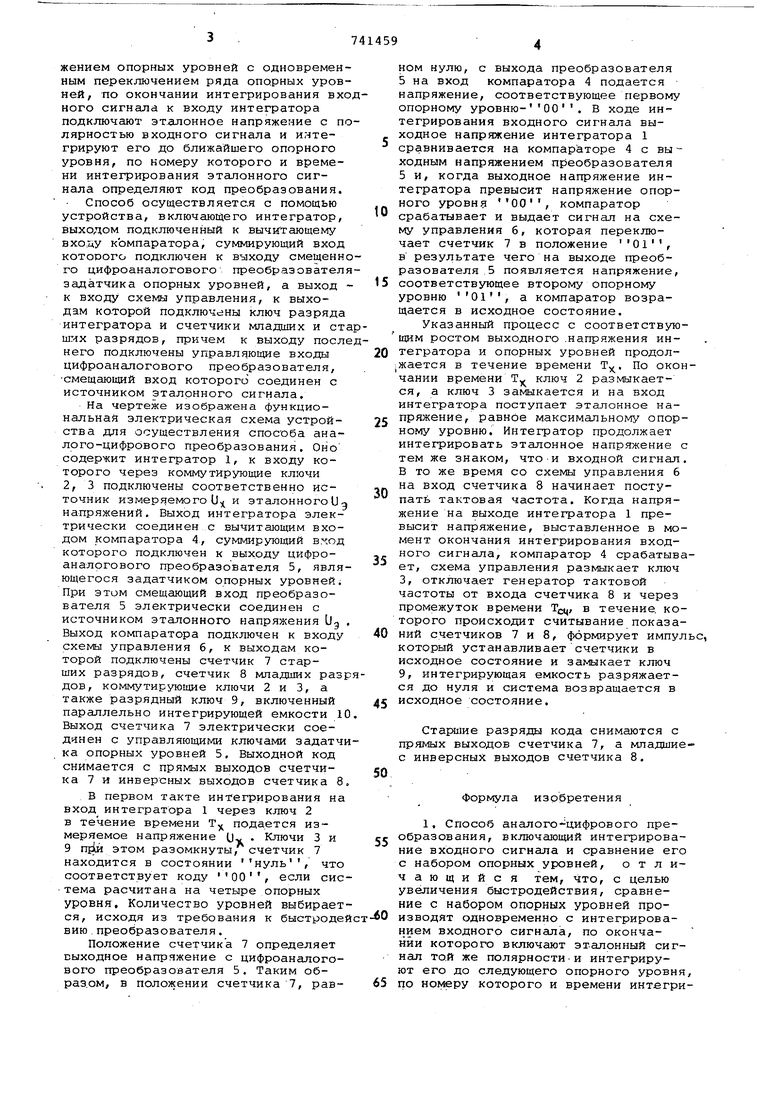

Изобретение относится к импульсной технике и может быть использовано в информационно-измерительных системах. Известен способ аналого-цифрового преобразования, заключающийся в том, что входной сигнал в первом такте.интегрируют, а затем во второ такте за ряд последовательных ша.гов разряжают интегратор от источника опорного напряжения, полярност которого противоположна полярности измеряемого напряжения, а величина его меняется., в. каждом шаге интегрирования и выбирается сравнением проинтегрированного входного сигналй с напряжением, определяющим вес каждого шага интегрирования. Ряд напряжений, определяющих количество шагов интегрирования и вес каждого шага, является набором опорных уров ней. Код преобразования определяют количеству шагов и времени разряда каждого шага интегрирования 1. Устройство, реализующее способ, содержит интегратор, задатчик опорных уровней, набор компараторов, определяюсцих сравнение проинтегрированного напряжения с набором опор ных уровней, схему управления, ана лизирующую результат сравнения и подключающ то с помощью входных ключей к входу интегратора соответствующиз напряжения опорного уровня, а к генератору тактовых импульсов - разрядные счетчики. Недостатками способа являются малое быстродействие преобразования и конструктивная сложность его реализации, поскольку устройство содержит число компараторов, равное количеству опорных уровней, т. е. числу шагов интегрирования, которое, в конечном итоге, определяет быстродействие преобразователя. Известны и другие, более быстродействующие способы преобразования, например способ поразрядного уравновешивания, параллельного действия, комбинированного типа, однако они обладают меньшей точностью и помехоустойчивостью 2. Целью изобретения является повышение быстродействия преобразования и упрощение конструкции преобразователя. Цель достигается тем, что входной сигнал интегрируют и в процессе интегрирования производят сравнение интегрируемого напряжения с напряжением опорных уровней с одновременным переключением ряда опорных уровней, по окончании интегрирования вхо ного сигнала к входу интегратора подключают эт-гшонное напряжение с по лярностью входного сигнала и интегрируют его до ближайшего опорного уровня, по номеру которого и времени интегрирования эталонного сигнала определяют код преобразования. Способ осуществляется с помощью устройства, включающего интегратор, выходом подключенный к вычнтающему входу компаратора, суммирующий вход КОТОРОГО подключен к выходу смещенн го цифроаналогового преобразовател зад атчик а опорных уровней, а выход к входу схемы управления, к выходам которой подключены ключ разряда интегратора и счетчики младших и ст ших разрядов, причем к выходу посл него подключены управляющие входы цифроаналогового преобразователя, смещающий вход которого соединен с источником эталонного сигнала, На чертеже изображена функциональнай электрическая схема устройства для осуществления способа аналого-цифрового преобразования. Оно содержит интегратор 1, к входу которого через коммутирующие ключи 2, 3 подключены соответственно источник измеряемого и и эталонногоUg напряжений. Выход интегратора электрически соединен с вычитающим входом компаратора 4, суммирующий вУчОД которого подключен к выходу цифроаналогового преобразователя 5, явля ющегося задатчиком опорных уровней. При этом смещающий вход преобразователя 5 электрически соединен с источником эталонного напряжения Ug Выход компаратора подключен к входу схемы управления б, к выходам которой подключены счетчик 7 старших разрядов, счетчик 8 младших раз дов, коммутирующие ключи 2 и 3, а также разрядный ключ 9, включенный параллельно интегрирующей емкости 1 Выход счетчика 7 электрически соеД {нен с управляющими ключами задатч ка опорных уровней 5. Выходной код снимается с прямых выходов счетчика 7 и инверсных выходов счетчика 8 В первом такте интегрирования на вход интегратора 1 через ключ 2 в течение времени Т подается измеряемое напряжение у„ . Ключи 3 и 9 njin этом разомкнуты, счетчик 7 находится в состоянии нуль, что соответствует коду 00, если сис тема расчитана на четыре опорных уровня. Количество уровней выбирает ся, исходя из требования к быстроде ВИЮ преобразователя. Положение счетчика 7 определяет выходное напряжение с цифроаналогового преобразователя 5. Таким образ.ом, в положении счетчика 7, равном нулю, с выхода преобразователя 5 на вход компаратора 4 подается напряжение, соответствующее первому опорному уровню-ОС. В ходе интегрирования входного сигнала выходное напряжение интегратора 1 сравнивается на компараторе 4 с выходным напряжением преобразователя 5 и, когда выходное напряжение интегратора превысит напряжение опорного уровня 00, компаратор срабатывает и выдает сигнал на схему управления б, которая переключает счетчик 7 в положение 01, в результате чего на выходе преобразователя 5 появляется напряжение, соответствующее второму опорному уровню 01, а компаратор возращается в исходное состояние. Указанный процесс с соответствующим ростом выходного .напряжения интегратора и опорных уровней продолЖается в течение времени Т, По окончании времени Т ключ 2 размыкается, а ключ 3 замыкается и на вход интегратора поступает эталонное напряжение, равное максимальному опорному уровню. Интегратор продолжает интегрировать эталонное напряжение с тем же знаком, чтОИ входной сигнал. В то же время со схемы управления б на вход счетчика 8 начинает поступать тактовая частота. Когда напряжение на выходе интегратора 1 превысит напряжение, выставленное в момент окончания интегрирования входного сигнала, компаратор 4 срабатывает, схема управления размыкает ключ 3, отключает генератор тактовой частоты от входа счетчика 8 и через промежуток времени Тся{ течение, которого происходит считывание показаний счетчиков 7 и 8, формирует импульс, который устанавливает счетчики в исходное состояние и замыкает ключ 9, интегрирующая емкость разряжается до нуля и система возвращается в исходное состояние. Старшие разряды кода снимаются с прямых выходов счетчика 7, а младшиес инверсных выходов счетчика 8. Формула изобретения 1. Способ аналого-цифрового преобразования, включающий интегрирование входного сигнала и сравнение его с набором опорных уровней, отличающийся тем, что, с целью увеличения быстродействия, сравнение с набором опорных уровней производят одновременно с интегрированием входного сигнала, по окончании которого включают эталонный сигнал то.й же полярности-и интегрируют его до следующего опорного уровня, по номеру которого и времени интегрирования эталонного сигнала определяют код преобразования.

2. Устройство для осуществления способа по п. 1 включает интегратор, выход которого подключен к вычитающему входу компаратора, суммирующи вход которого подключен к выходу цифроаналогового преобразователя, а- выход - к входу блока управления, к выходам которого подключены ключ разряда интегратора, счетчик младших разрядов и счетчик старших разрядов, к выходу которого подключены управ.ляющие входы цифроаналогового преобразователя, смещающий вход.которого соединен с источником эталонного сигнала.

Источники информации, принятые во внимание при экспертизе

1.Прянишников В.А. Интегрирующие цифровые вольтметры постоянного тока, Л., Энергия, 1976, с. 49-53.

2.Бахтиаров Г.Д., Дикий С,А. Аналого-цифровые преобразователи, Зарубежная радиоэлектроника , 1, 1975, с. 52-90 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU1056449A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 2003 |

|

RU2245000C2 |

| Аналого-цифровой преобразователь | 1979 |

|

SU782153A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Квадратирующий аналого-цифровой преобразователь | 1982 |

|

SU1051548A1 |

| Устройство для измерения дифференциальной нелинейности быстродействующих аналого-цифровых преобразователей | 1985 |

|

SU1282323A1 |

| Аналого-дискретное интегрирующее устройство | 1979 |

|

SU875407A1 |

| СИГМА-ДЕЛЬТА-АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2145149C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

Авторы

Даты

1980-06-15—Публикация

1978-10-23—Подача