ш (Л

00 О5

сл

со

28

J2

адреса, регистр 6 микрокоманд, второй регистр 7 адреса, регистр 8 нано команд, первый блок 9 контроля, второй блок 10 контроля, коммутатор 11, первый коммутатор 12 адреса, второй коммутатор 13 адреса, коммутатор 14 адреса, мультиплексор 15 ло гкческих условий, группу элементов И 16, триггер 17 запуска, триггер

5091

18 отказа, генератор 19 тактовых импульсов, группу элементов НЕ 20, первый 21, второй 22, третий 23, четвертый 2А элементы И, второй 25, первый 26 -элементы ИЛИ, одновибратор 27, операционный блок 28. Указанная цель достигается с помощью вышеуказанной совокупности признаков. 2 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для программного управления технологическими процессами | 1987 |

|

SU1495746A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных управляющих системах. Цель изобретения - повышение достоверности функционирования устройства. Устройство содержит блок 1 памяти микрокоманд, группу блоков памяти наноко- манд, блок 3 ассоциативной памяти, регистр 4 команд, первый регистр 5

1

Изобретение относится к вычислительной технике и может найти широкое применение в информационных, управляющих и вычислительных системах, в частности в микропроцессорных уп- равляющих системах.

Цель изобретения - повышение достоверности функционирования процессора.

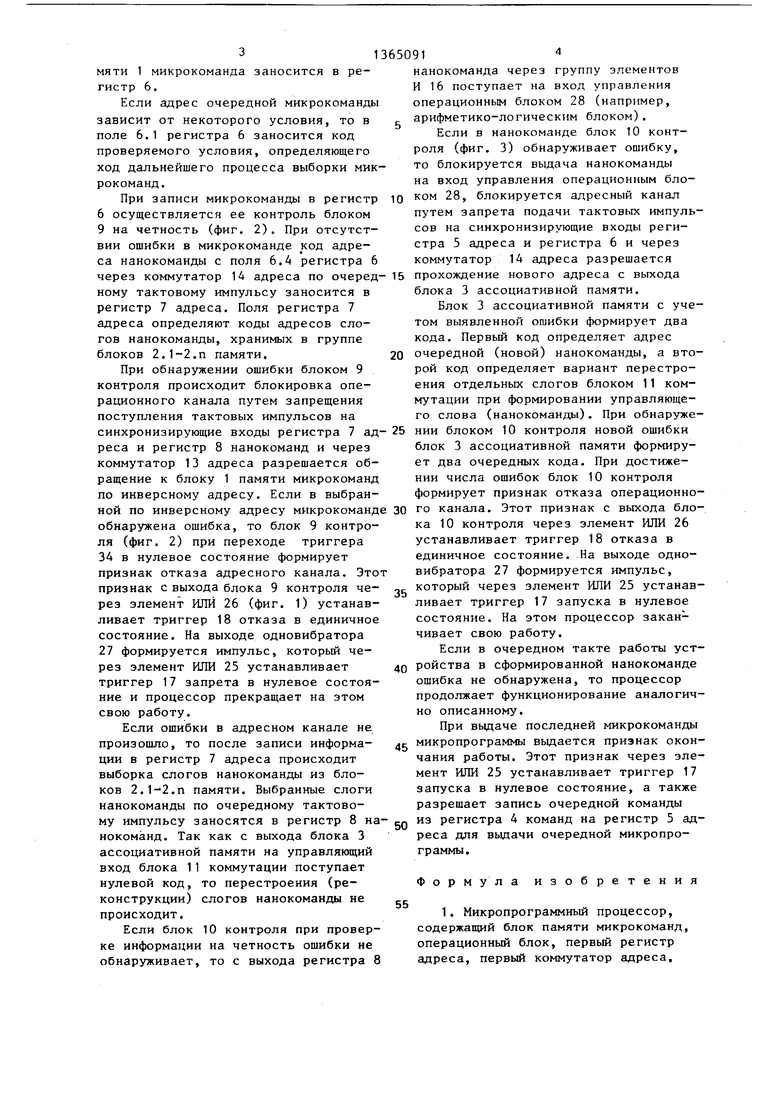

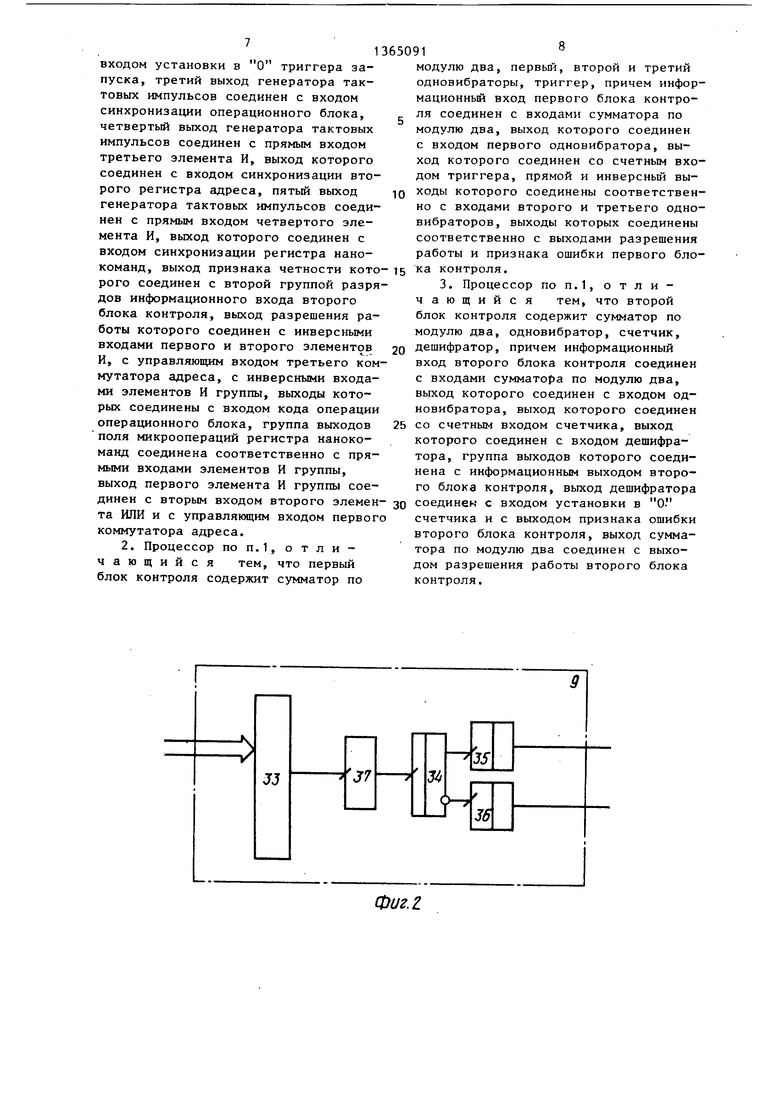

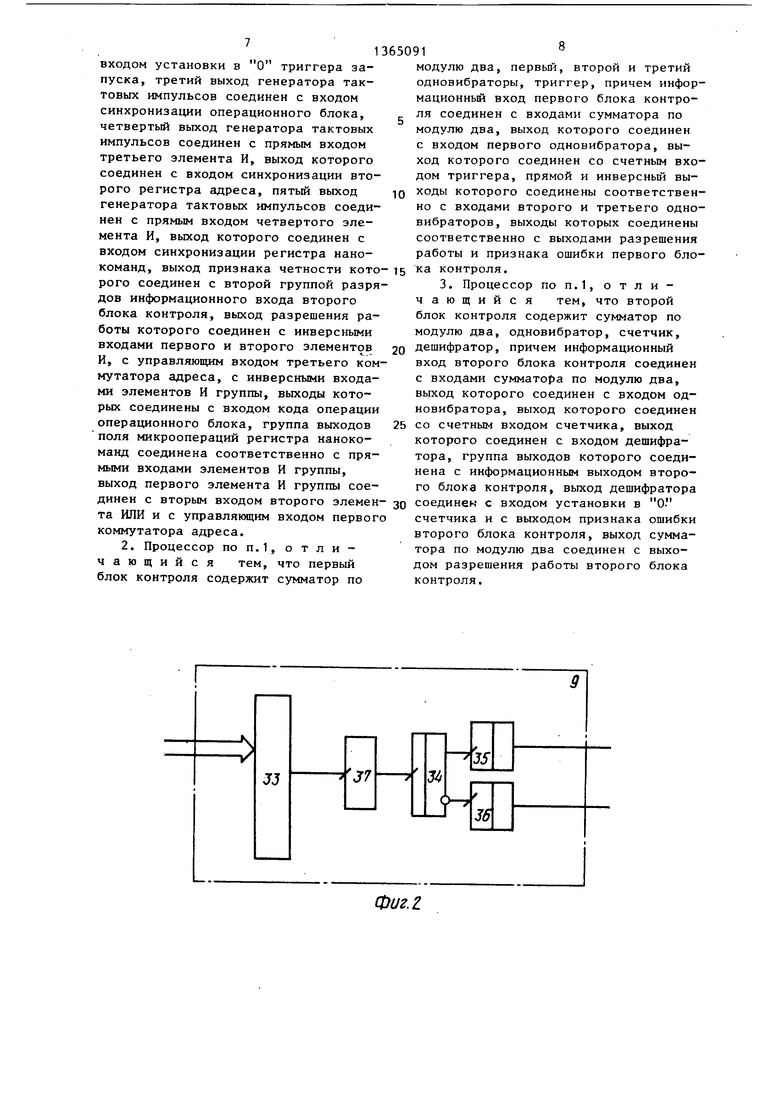

На фиг. 1 представлена функциональная схема микропрограммного процессора; на фиг. 2 - функциональная схема первого блока контроля; на фиг. 3 - функциональная схема второго блока контроля.

Микропрограммный процессор (фиг.1 содержит блок 1 памяти микрокоманд, группу блоков 2.1-2.п памяти нано- команд, блок 3 ассоциативной памяти, регистр 4 команд, первый регистр 5 адреса, регистр 6 микрокоманд с полями: полем 6.1 проверяемого логического условия, полем 6.2 модифицированного разряда адреса, полем 6.3 немодифицируемых разрядов адреса, полем 6.4 адреса нанокоманды и полем 6.5 признака четности информации, второй регистр 7 адреса, регистр 8 нанокоманд, первый 9 и второй 10 блоки контроля, коммутатор 11, пер- вь1й 12, второй 13 и третий 14 коммутаторы адреса, мультиплексор 15 логических условий, группу элементов И 1 триггер 17 запуска, триггер 18 отказа, генератор 19 тактовых импульсов, группу элементов НЕ 20, первый 21, второй 22, третий 23 и четвертый 24 элементы И, второй элемент ИЛИ 25, первый элемент ИЛИ 26, одновибратор 27, операционный блок 28, вход 29 кода команды, управляющий вход 30,

0

5

0

g 5

0

вход 31 данных и выход 32 процессора Хрезультата).

Первый блок 9 контроля (фиг. 2) содержит сумматор 33 по модулю два, счетный триггер 34, первый 35, второй 36 и третий 37 одновибраторы.

Второй блок 10 контроля (фиг. 3) содержит сумматор 38 по модулю два, счетчик 39, дешифратор 40, одновибратор 41.

Микропрограммный процессор работает следующим образом.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии (за исключением триггера регистра 8 нанокоманд, определяющего окончание выдачи управляющего слова на операционный блок 28).

Работа процессора начинается путем подачи на вход 29 процессора кода выполняемой команды. Данный код заносится в регистр 4 команд. При поступлении на вход 30 процессора сигнала на начало работы триггер 17 запуска устанавливается в единичное состояние и разрешает тем самым формирование тактовых импульсов с выходов генератора 19 для синхронизации работы процессора. Так как признак ошибки по операционному каналу отсутствует, то по первому тактовому импульсу с выхода генератора 19, поступающему через элемент И 21 на синх- ронизирующий вход регистра 5, код команды с выхода регистра 4 команд через коммутаторы адреса 12 и 13 занесен в регистр 5 адреса. Код команды определяет адрес первой микрокоманды соответствующей микрокоманды. По второму тактовому импульсу с выхода генератора 19 сосчитанная из блока памяти 1 микрокоманда заносится в регистр 6.

Если адрес очередной микрокоманды зависит от некоторого условия, то в поле 6.1 регистра 6 заносится код проверяемого условия, определяющего ход дальнейшего процесса выборки микрокоманд.

При записи микрокоманды в регистр 6 осуществляется ее контроль блоком 9 на четность (фиг. 2). При отсутствии ошибки в микрокоманде код адреса нанокоманды с поля 6.А регистра 6 через коммутатор 14 адреса по очеред ному тактовому импульсу заносится в регистр 7 адреса. Поля регистра 7 адреса определяют коды адресов слогов нанокоманды, хранимых в группе блоков 2.1-2.П памяти.

При обнаружении ошибки блоком 9 контроля происходит блокировка операционного канала путем запрещения поступления тактовых импульсов на синхронизирующие входы регистра 7 ад реса и регистр 8 нанокоманд и через коммутатор 13 адреса разрешается обращение к блоку 1 памяти микрокоманд по инверсному адресу. Если в выбранной по инверсному адресу микрокоманд обнаружена ошибка, то блок 9 контроля (фиг. 2) при переходе триггера 34 в нулевое состояние формирует признак отказа адресного канала. Это признак с выхода блока 9 контроля че- рез элемент ИЛИ 26 (фиг. 1) устанавливает триггер 18 отказа в единичное состояние. На выходе одновибратора 27 формируется импульс, который через элемент ИЛИ 25 устанавливает триггер 17 запрета в нулевое состояние и процессор прекращает на этом свою работу.

Если ошибки в адресном канале не произошло, то после записи информа- ции в регистр 7 адреса происходит выборка слогов нанокоманды из блоков 2.1-2.П памяти. Выбранные слоги нанокоманды по очередному тактовому импульсу заносятся в регистр 8 на нокоманд. Так как с выхода блока 3 ассоциативной памяти на управляющий вход блока 11 коммутации поступает нулевой код, то перестроения (реконструкции) слогов нанокоманды не происходит.

Если блок 10 контроля при проверке информации на четность ошибки не обнаруживает, то с выхода регистра 8

0 г 0

5 g

5

нанокоманда через группу элементов И 16 поступает на вход управления операционньм блоком 28 (например, арифметико-логическим блоком).

Если в нанокоманде блок 10 контроля (фиг. 3) обнаруживает ошибку, то блокируется выдача нанокоманды на вход управления операционным блоком 28, блокируется адресный канал путем запрета подачи тактовых импульсов на синхронизирующие входы регистра 5 адреса и регистра 6 и через коммутатор 14 адреса разрешается прохождение нового адреса с выхода блока 3 ассоциативной памяти.

Блок 3 ассоциативной памяти с учетом выявленной ошибки формирует два кода. Первый код определяет адрес очередной (новой) нанокоманды, а второй код определяет вариант перестроения отдельных слогов блоком 11 коммутации при формировании управляющего слова (нанокоманды). При обнаружении блоком 10 контроля новой ошибки блок 3 ассоциативной памяти формирует два очередных кода. При достижении числа ошибок блок 10 контроля формирует признак отказа операционного канала. Этот признак с выхода блока 10 контроля через элемент ИЛИ 26 устанавливает триггер 18 отказа в единичное состояние. На выходе одно- вибратора 27 формируется импульс, который через элемент ИЛИ 25 устанавливает триггер 17 запуска в нулевое состояние. На этом процессор заканчивает свою работу.

Если в очередном такте работы устройства в сформированной нанокоманде ошибка не обнаружена, то процессор продолжает функционирование аналогично описанному.

При вьщаче последней микрокоманды микропрограммы выдается признак окончания работы. Этот признак через элемент ИЖ 25 устанавливает триггер 17 запуска в нулевое состояние, а также разрешает запись очередной команды из регистра 4 команд на регистр 5 адреса для вьздачи очередной микропрограммы.

Формула изобретения

регистр микрокоманд, мультиплексор логических условий, триггер запуска, генератор тактовых импульсов, коммутатор, первый и второй элементы И, причем вход кода операции процессора соединен с первым информационным входом первого коммутатора адреса, вход пуска процессора соединен С входом установки в 1 триггера за пуска, выход которого соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с прямым входом первого элемента И, выход которого соединен с входом синхронизации первого регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля логических условий которого соединен с управляющим входом мультиплексора логических условий, вход данных процессора соединен с входом данных операционного блока, выход данных которого соединен с выходом процессора, выход поля модифицируемых разрядов адреса регистра микрокоманд соедлнен с первым информационным входом мультиплексора логических условий, выход поля немодифицируемых разрядов адреса регистра микрокоманд соединен с вторым информационным входом первого коммутатора адреса, выход признаков результата операционного блока соединен с вторым информационным входом мультиплексора логических условий, выход которого соединей с вторым информационным входом первого коммутатора адреса, второй выход генератора тактовых импульсов соединен с прямым входом второго элемента И, выход которого соединен с входом синхронизации регистра микрокоманд, отличающийся тем, что, с целью повьшения достоверности функционирования, процессор содержит группы блоков памяти наноксманд, блок ассоциативной памяти, первый и второй блоки контроля, второй и третий коммутаторы адреса, группу элементов И, второй регистр адреса, регистр нано- команд, триггер отказа, одновибратор ком гутатор, третий четвертый элементы И, первый и второй элементы ИЛИ, группу элементов НЕ, причем выход поля немодифицированных разрядов адреса регистра микрокоманд соединен с

65091

первой группой разрядов информационного входа первого блока контроля, выходы поля логических условий и пос ля адреса нанокоманды регистра микрокоманд соединены соответственно с второй и третьей группами разрядов информационного входа первого блока контроля, выход поля признака четнос- 10 ти регистра микрокоманд соединен с четвертой группой разрядов информационного входа первого блока контроля, выход разрешения работы которого соединен с управляющим входом второ-

15 го коммутатора адреса и с инверсными входами третьего и четвертого элементов И, выход первого коммутатора адреса соединен с входом элементов НЕ группы и первым информационным входом

20 второго коммутатора адреса, выходы элементов НЕ группы соединены с вторым информационным входом второго коммутатора адреса, выход которого соединен с информационным входом первого ре25 гистра адреса, выход поля адреса нанокоманды регистра микрокоманд соединен с первым информационным входом третьего коммутатора адреса и с первым адресным входом блока ассоциатив30 ной памяти, выход которого соединен с вторым информационным входом третьего коммутатора адреса, выход которого соединен с информационным входом второго регистра адреса, выходы полей адреса которого соединены с адресными входами соответствующих блоков памяти нанокоманд группы, выходы которых соединены соответственно с информационными входами коммутатора,

Q выходы которого соединены с информационными входами регистра наноксманд, выход поля микроопераций которого соединен с первой группой разрядов информационного входа второго блока

дс контроля, информационный выход которого соединен с вторым адресным входом бпока ассоциативной памяти, выход которого соединен с управляющим входом коммутатора, выход признака

ЗЬ

ошибки первого блока контроля и выход признака ощибки второго блока контроля соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с входом установки в 1 триггера отказа, выход которого соединен с входом одновибратора, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с

входом установки в О триггера запуска, третий выход генератора тактовых импульсов соединен с входом синхронизации операционного блока, четвертый выход генератора тактовых импульсов соединен с прямым входом третьего элемента И, выход которого соединен с входом синхронизации второго регистра адреса, пятьй выход генератора тактовых импульсов соединен с прямым входом четвертого элемента И, выход которого соединен с входом синхронизации регистра нано- команд, выход признака четности кото рого соединен с второй группой разрядов информационного входа второго блока контроля, выход разрешения работы которого соединен с инверсными

входами первого и второго элементов 20 дешифратор, причем информационный

И, с управляющим входом третьего коммутатора адреса, с инверсными входами элементов И группы, выходы которых соединены с входом кода операции операционного блока, группа выходов 25 поля микроопераций регистра наноко- манд соединена соответственно с прямыми входами элементов И группы, выход первого элемента И группы соединен с вторым входом второго элемен- зо соединен та ИЛИ и с управляющим входом первого счетчика коммутатора адреса.

вход второго блока контроля соедин с входами сумматора по модулю два, выход которого соединен с входом о новибратора, выход которого соедин со счетным входом счетчика, выход которого соединен с входом дешифра тора, группа выходов которого соед нена с информационным выходом втор го блока контроля, выход дешифрато с входом установки в 0. и с выходом признака ошиб второго блока контроля, выход сумм тора по модулю два соединен с выхо дом разрешения работы второго блок контроля.

модулю два, первый, второй и третий одновибраторы, триггер, причем информационный вход первого блока контроля соединен с входами сумматора по модулю два, выход которого соединен с входом первого одновибратора, выход которого соединен со счетным входом триггера, прямой и инверсный выходы которого соединены соответственно с входами второго и третьего одно- вибраторов, выходы которых соединены соответственно с выходами разрешения работы и признака ошибки первого блока контроля.

соединен счетчика

вход второго блока контроля соединен с входами сумматора по модулю два, выход которого соединен с входом одновибратора, выход которого соединен со счетным входом счетчика, выход которого соединен с входом дешифратора, группа выходов которого соединена с информационным выходом второго блока контроля, выход дешифратора с входом установки в 0. и с выходом признака ошибки второго блока контроля, выход сумматора по модулю два соединен с выходом разрешения работы второго блока контроля.

Фиг. 2.

38

1

39

V

0

(риг.з

| Микропрограммный процессор | 1981 |

|

SU1024927A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-07—Публикация

1986-05-16—Подача