(54) ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля состояния объекта | 1983 |

|

SU1119055A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство для контроля программ | 1983 |

|

SU1136172A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных устройств, например для управления технологическим обо рудованием. Известно устройство, допускающее обработку слов переменной длины, которое поз воляет работать со словами переменной длины, кратной длине слога 1. Недостатком этого устройства является невозможность логическойГ обработки слов переменной длины непосредственно в ячейках накопителя. Наиболее близким к предлагаемому техническим решением является устройство для параллельного суммирования двух чисел, выполненное на оперативной памяти с линейной выборкой и содержащее логический блок, блок циклического сдвига кодов, блок управления, контрольные импульсные формирователи тока, реверсивные ключи, входы которых подсоединены к выходам блока управления, а выходы соединены с адресными шинами оперативной памяти, вход одного из контрольных импульсных формлрователей тока подключен к объединенным вь1ходам всех усилителей чтения, а вход второГО контрольного импульсного формирователя тока подсоединен к выходу усилителя чтения старшего разряда, выход каждого усилителя чтения соединен через диод со входом каждого предыдущего ключа регистра регенерации блока циклического сдвига, кодов, кроме того, выход каждого усилителя чтения через блок задержки и диод соединен с дополнительным входом считывания ключа регистра регенерации следующего старшего разряда и с дополнительной шиной импульсного питания, а выход каждого ключа регистра регенерации подключен к дополнительным выходам считывания ключа следующего старшего разряда. Данное устройство позволяет осуществлять логическую обработку слов непосредственно в ячейках накопителя. Выходные сигналы накопителя усиливаются усилителями считывания, выходы которых соединяются с регистром регенерации либо без сдвига, либо со сдвигом на один разряд. Блок управления вырабатывает последовательность управляющих сигналов, которая определяется кодом операции, поступающим со вторых выходов регистра команды. Эта последовательность изменяется в зависимости от значения служебных разрядов считываемого из накопителя слова, в частности, от знакового разряда.

Для уплотнения информации в накопителе возможно расположение нескольких слов в одной ячейке. Такая структура позволяет осуществлять выборку этой информации и расположение ее в определенных, например младших разрядах второй группы ячеек накопителя за несколько циклов обращения к накопителю путем сдвигов на необходимое число разрядов впра-во 2.

Однако для выполнения логических и арифметических операций над словами переменной длины в такой структуре необходимо иметь набор констант, с помощью которых производится выделение из содержимого выбранной ячейки информации, находящейся в пределах заданного формата. Эти же константы необходимы для организации Циклического переноса при выполнении операции сложения над числами произвольных знаков. Это приводит к значительному увеличению времени выполнения логических и арифметических операций над слова.ми переменной длины, что дела-ет описанную структуру неэффективной при обработке слов переменной длины. Цель изобретения - повышение производительности устройства за счет увеличения быстродействия при обработке слов переменной длины. Поставленная цель достигается тем, что устройство, содержащее два блока оперативной памяти, две группы усилителей считывания, информационными входами соединенных с выходами соответствующих блоков оперативной памяти, регистр регеперации, две группы элементов И, регистр адреса, регистр команд, дешифратор адреса, дешифратор микрокоманд, входы регистра команд соединень с выходами элементов И первой группы, первый выход регистра команд соединен со входом регистра адреса, второй выход - с первым входом дещифратора микрокоманд, второй вход которого соединен с группой выходов элементов И второй группы, первый выход регистра адреса через дешифратор адреса соединен с адресными входами первого и второго блоков оперативной памяти, соответствующие выходы дешифратора микрокоманд соединены со входами считывания-записи первого и второго блоков оперативной памяти, с управляющими входами элементов И первой группы и регистра регенерации, содержит два шифратора, группу элементов ИЛИ, два дешифратора, сумматор, коммутатор, информационными входами соединенный с информационными входами усилителей считывания первой группы, а выходами - с первыми входами элементов И второй группы и регистра регенерации, а также с информационными входами элементов И первой группы, выходы усилителей считывания

второи группы соединены с первым входом сумматора, второй вход которого соединен со вторым информационным входом регистра регенерации и со вторым выходом регистра адреса, управляющие входыусилителей

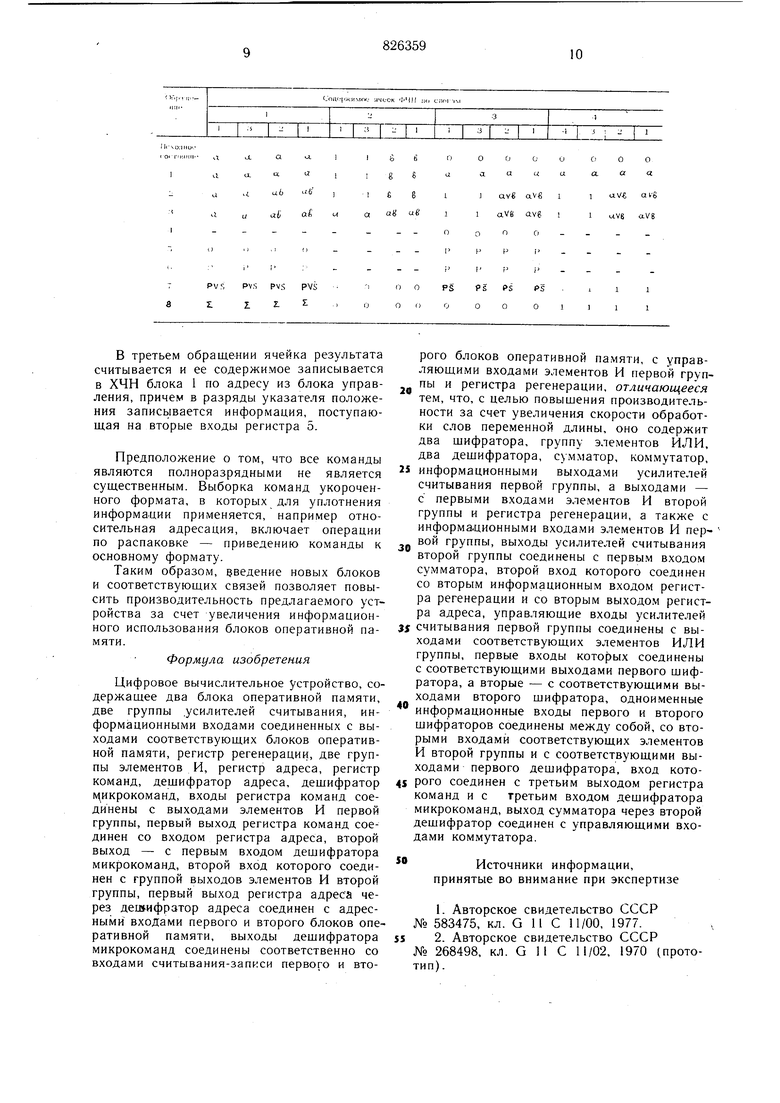

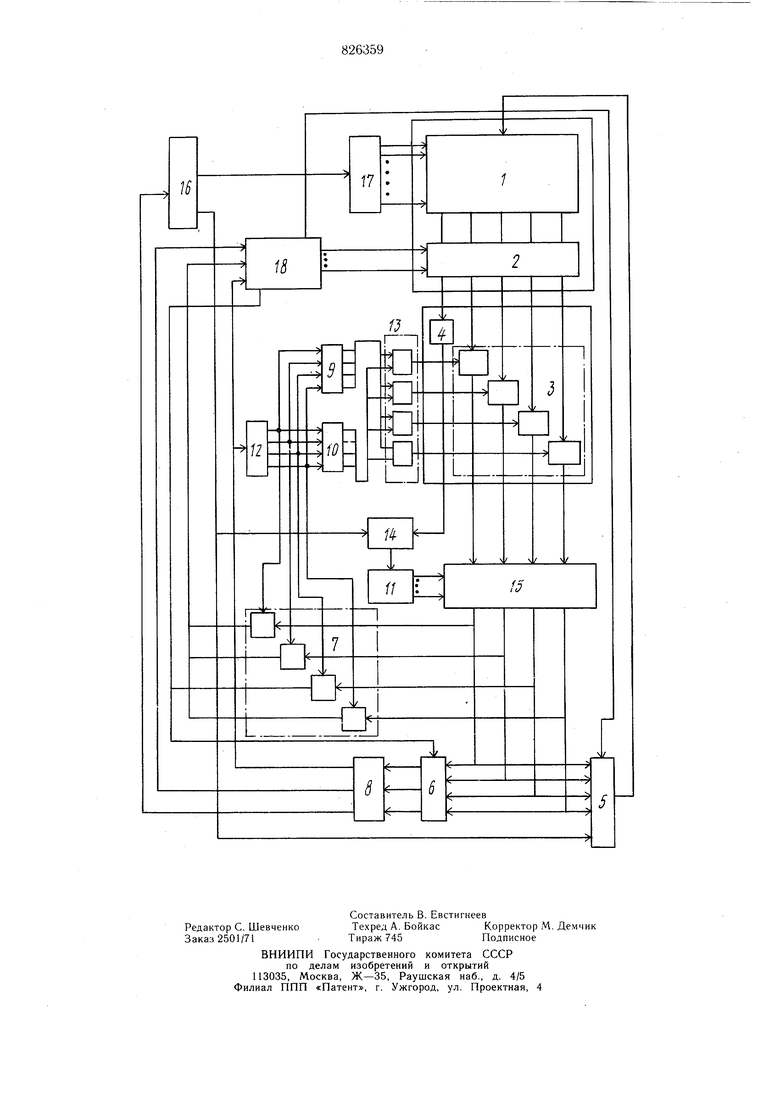

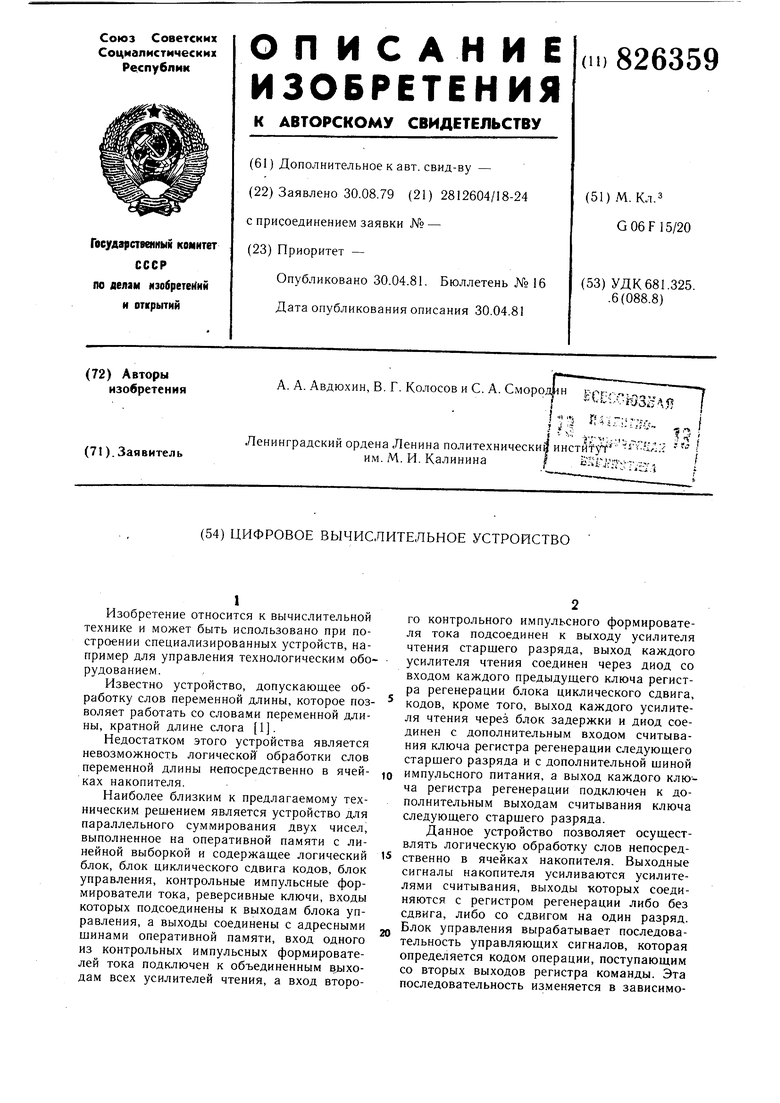

считывания первой группы соединены с выходами соответствующих элементов ИЛИ группы, первые входы которых соединены с соответствующими выходами первого шифратора, а вторые - с соответствующими выходами второго шифратора, одноименные информационные входы первого и второго шифраторов соединены между собой, со вторыми входами соответствующих элементов И второй группы и с соответствующими выходами первого дещифратора, вход которого соединен с третьим выходом регистра команд и с третьим входом дешифратомикрокоманд, выход сумматора через второй дещифратор соединен с управляющими входами коммутатора. На чертеже представлена блок-схема устройства. Устройство содержит первый и второй блоки 1 и 2 оперативной памяти, первую и вторую группы усилителей 3 и 4 считывания, регистр 5 регенерации, первую и вторую группы элементов И 6 и 7, регистр 8 команд, первый и второй шифраторы 9 и 10, первый и второй дешифраторы 11 и 12, группу элементов ИЛИ 13, сумматор 14, коммутатор 15, регистр 16 адреса, дешифратор 17 адреса, дещифратор 18 микрокоманд. Назовем первый блок оперативной, памяти хранящей частью накопителя (ХЧН), а второй блок оперативной памяти - функциональной частью накопителя (ФЧН). Блоки оперативной памяти и группы усилителей считывания имеют разрядность knw-t где k - максимальное число слогов, котоpgg можно разместить в одной ячейке блока оперативнои памяти, m - разрядность одного слога, а 1 log - разрядность той ячейки блока оперативной памяти, которая предназначена для хранения информации о расположении группы из k слогов относительно младшего разряда ячейки. Таким образом, усилители считывания первой группы представляют собой k групп по m усилителей, а усилители считывания второй группы - группу из 1 усилителей. На черте е изображена схема для k 4. Коммутатор 15 предназначен для передачи поступающего на его входы кода с циклическим сдвигом на jm разрядов, где j 0,l,...,(k-I), под управлением сигналов с выхода дешифратора И. Для организации в микропрограммах условных переходов в зависимости от значений служебных разрядов считываемого из блоков оперативной памяти слова устройство содержит вторую группу элементов И 7. Первые входы элементов И 7 подключены к тем выходам блока коммутатора 15, которые соответствуют разрядам, от значения которых зависит выборка очередной микрокоманды. В данном устройстве в качестве таких разрядов выступают те разряды, в которых может располагаться знак считываемого из блоков оперативной памяти числа. Такими разрядами являются старшие разряды каждого из k слогов. (Предполагается, что слова могут иметь дли, ну 1, 2, ..., k слогов). Третий выход регистра 8 команд соответствует тем разрядам команды, в которых содержится информация о длине oneранда. Шифраторы 9 и 10 отличаются тем, что первый из них обеспечивает работу тольКО тех усилителей 3 считывания, которые находятся в пределах длины слова, заданного кодом с третьего выхода регистра 8 команд. Шифратор 10 обеспечивает работу усилителей тех разрядов, которые находятся за пределами заданного формата. Устройство работает следующим образом. Работу его рассмотрим на примерах выборки команды, выборки операнда и выполнения операции сложения. Выборка команды производится следующим образом. Для упрощения полагаем, что команды только полноразрядные, т. е. занимают km разрядов. По адресу, поступающему с регистра 16 адреса в блоки 1 и 2 оперативной памяти, производится считывание информации из ХЧН и запись содержимого выбранной ячейки в регистрах 5 через информационный вход в блок 8 управления, например в его регистр команд. Во втором такте обращения команда регенерируется по старому адресу. -На этом выборка команды из ХЧН завершается. Операция выборки операнда имеет ряд отличий. По предположению, операнд может иметь длину jm слогов (J 1, 2, ..., k), т. е. младший слог выбираемого слова может занимать положение, не совпадающее с положением младщего слога полноразрядного операнда. Поэтому в процессе выборки операнда необходимо расположить его в соответствующих разрядах ячейки ФЧН, Нумеруем группы разрядов ячейки блоков оперативной памяти, начиная с младщего, присваивая им номера от О до k-1. Такие же номера присвоим слогам содержимого ячейки. Последние номера являются адресами этих слогов. В процессе расположения выбираемых слогов в нужных позициях с помощью блока 15 производится цикличный сдвиг всей группы из k слогов. Располагаем в разрядах, соответствующих выходам второй группы усилителей 4, номер того же из слогов, который к моменту обращения находится в младщей (нулевой) группе разрядов ячейки. Назовем это число указателем положения. Тогда для расположения младшего слога выбираемого слова в нулевой группе разрядов регистра 5 необходим сдвиг слова вправо на jm разрядов, где j - разность между адресом слога, поступающим с регистра 16 адреса и указателем положения. Эта разность вйчисляется в сумматоре 14. Так как слог с номером, равным адресу слога, оказывается в нулевой группе разрядов, то новому положению всей группы слогов соответствует новое значение указателя положения, равное адресу слога, поступающему на второй вход сумматора 14. Таким образом, выборка операнда сводится к следующему. В первом обращении к накопителю в такте считывания производится .считывание группы слогов из ХЧН. Одновременно адрес слога второго выхода регистра 16 адреса поступает в сумматор 14, на другой вход которого поступает указатель положения. Код, соответствующий разности этих величин, поступает на входы дешифратора II. Под управлением сигнала с выходов последнего блок коммутатора 15 осуществляет передачу слогов с выходов усилителей 3 считывания первой группы на входы регистра 5 регенерации с соответствующим сдвигом так, что младшие разряды выбираемого слова оказываются записанными в младших разрядах регистра 5. На другие входы этого регистра поступает адрес слога со второго выхода регистра 16, адреса, значение которого соответствует новому положению считанной группы слогов. В такте записи данная группа слогов регенерируется в той же ячейке ХЧН, но в новом положении и с новым значением указателя положения. В том же такте эта группа слогов записывается в ячейку ФЧН блока 2. Информация о длине слова со второго информационного выхода блока 8 управления поступает на вход дешифратора 12. Если длина слова равна k, то по выполнении описанных действий выборка операнда завершается. Если длина слова i меньше k слогов, то во втором обращении производится считывание из ФЧН блока 3 той же группы слогов. Под действием сигналов с выходов шифратора 9 и элементов ИЛИ 13 в момент считывания работает только i младших групп усилителей 3. В регистр 5 записываются тольг ко те слоги, которые входят в состав выбираемого слова. Во втором такте обращения производится запись выделенных слогов в ФЧН. Одновременно со считыванием через открытый сигналом с выхода дешифратора 12 элемент И 7 в блок управления поступает содержимое знакового разряда слова длиной i. Если выбираемое число положительно, то операция завершается. В противном случае производится считывание с инверсией любой свободной ячейки ФЧН блока 3. Сигналами с выходом шифратора 10 и элементов ИЛИ 13 открываются те усилители 3, которые соответствуют разрядам, находящимся за иреде.чами заданного формата. В соответствующие разряды регистра 5 с выходов усилителей 3 считывания через блок коммутатора 15 записываются единицы. В такте записи содержимое регистра 5 за11нс1)1ваетея е дизъюнкцией в ту ячейку ФЧН б.юка 2, в которой находится выбранное слово. В результате во всех разрядах чис.Та левее знакового занисываются единицы, что иеобходи.мо для выполнения арифметических операций. Выполнение операции сложения раесмот РИМ па примере еуммирования чисел А и В, длина которых равна четырем и двум слогам соответственно, нричем В 0. Суммирование выполняем по фор.мулам: ZL - PiSi V(Pe V SL). SL (QL V bj.) Vai. b{, Pi+i a-,bi V ( Ы) PI где J.- -значение i-ro разряда результата;l -значение i-го разряда норазрядной су.ммы по модулю два; PU -значение переноса в J-й разряд, которое формируется при считывании слова дизъюнкции слагаемых А и В, сдвинутого на один разряд влево, словом конъюнкции сла1аемых, также сдвинутым па одип разряд влево. O-j. j8i. -значения i-го разряда слагаемых. Процесс вынолнения операции сложения поясняется таблицей. При описании ячейки ФЧН функциональная ячейка сокращенно обозначается ФЯ) (i - номер ячейки ФЧН). В результате операций выборки слагаемые расиолагаются в ФЯ1 и ФЯ2 - исходное состояние (первая строка таблицы). Буквами а; и Ь; обозначены слоги чисел А и В, аналогично через Sj и Р.; обозначены соот.оо ветствующие j-му слогу груипы разрядов суммы МО модулю два и слова переноса. В таблице обозначены состояния соответствующих разрядов ФЯ: которые они принимают по окончании данного обращения к ФЧН 3. Первое обращение: считывание ФЯ1 и запись ее содержимого (с дизъюнкцией) в ФЯ1, ФЯЗ и ФЯ4. Второе обращение: считывание ФЯ2 и запись ее содержимого с дизъюнкцией в ФЯ2, ФЯЗ и ФЯ4, а также в том же такте запись с конъюнкцией в ФЯ1. Третье обращение: считывания ФЯ1 и запись ее содержимого с дизъюнкцией в ФЯ1 и с конъюнкцией в ФЯ2. Таким образом, в двух ячейках ФЧН блока 2 сформирована поразрядная дизъюнкция слагаемых, а в двух других - поразрядная конъюнкция слагаемых А и В. В трех следующих обращениях формируется слово переноса. Четвертое обращение: в первом такте производится считывание ФЯЗ со сдвигом влево на один разряд, а во втором такте считывание регистра 5 не производится, таким образом, после данного обращения в регистре 5 регенерации записана поразрядная дизъюнкция слагаемых, сдвинутая на один разряд влево. Пятое обращение: в первом такте производится считывание ФЯ1 со сдвигом на один разряд влево. На выходе (i-f 1)-го разряда регистра 5 появляются импульсы только в том случае, если формирователь этого разряда подготовлен (. 1) и считан либо сигналом с выхода блока коммутатора 15 ( 1), либо импульсом с формирователя соседнего младщего разряда регистра 5, т. е. Pi 1. Таким образом, на выходах регистра 5 в этом такте появляется слово переноса, вычисленное по приведенной формуле. В том же такте возбуждается формирователь тока записи с дизъюнкцией в ФЯЗ. Шестое обращение: считывание ФЯЗ и запись в ФЯ и ФЯЗ. В двух последующих обращениях формируется результат суммирования. Седьмое обращение: считывание с инверсией ФЯ4 и одновременно считывание ФЯ2 в первом такте с получением в регистре 5 инверсии поразрядной суммы по модулю два (S и запись этого слова в ФЯ1 с дизъмнкцией и в ФЯЗ с конъюнкцией. Восьмое обращение: считывание с инверсией ФЯ1 и одновременное считывание ФЯЗ с получением в регистре 5 окончательного результата суммы (2;) по приведенной формуле. Во втором такте запись с конъюнкцией результата в ФЯ1. Операция записи результата выполняется в следующем порядке. В первом обращении производится считывание ячейки ХЧН блока I по адресу с выходов регистра 16 адреса с коммутацией в коммутаторе 15 в соответствии со значениями адреса младшего слога, поступающего на второй вход сумматора 14, и указателя положения с выходов усилителей 4 аналогично первому такту операции выборки числа. Во втором такте обращения считывания група слогов записывается в ячейку ФЧН блока 2. . Во втором обращении эта ячейка считывается и обнуляются те разряды, которые находятся в пределах .заданного формата. В такте записи производится запись с дизъюнкцией оставщейся за пределами формата информации в ячейку ФЧН, хранящую результата (ФЯ1 в примере из таблицы).

L

ati

at a

pvs pvs pvi;

PV z

z

В третьем обращении ячейка результата считывается и ее содержимое записывается в ХЧН блока 1 по адресу из блока управления, причем в разряды указателя положения записывается информация, поступающая на вторые входы регистра 5.

Предположение о том, что все команды являются полноразрядными не является существенным. Выборка команд укороченного формата, в которых для уплотнения информации применяется, например относительная адресация, включает операции по распаковке - приведению команды к основному формату.

Таким образом, ведение новых блоков и соответствующих связей позволяет повысить производительность предлагаемого устройства за счет увеличения информационного использования блоков оперативной памяти.

Формула изобретения

Цифровое вычислительное устройство, содержащее два блока оперативной памяти, две группы .усилителей считывания, информационными входами соединенных с выходами соответствующих блоков оперативной памяти, регистр регенерации, две группы элементов И, регистр адреса, регистр команд, дещифратор адреса, дещифратор М икрокоманд, входы регистра команд соединены с выходами элементов И первой группы, первый выход регистра команд соединен со входом регистра адреса, второй выход - с первы.м входом дещифратора микрокоманд, второй вход которого соединен с группой выходов элементов И второй группы, первый выход регистра адреса через дешифратор адреса соединен с адресными входами первого и второго блоков оперативной памяти, выходы дещифратора микрокоманд соединены соответственно со входами считывания-записи первого и втоо a

о a.

Ci

о a

6

a.

a

u

8

1 av« ak-g

QY« aV«

6

ий

aVe av6 1 uV6 aVe

о о p I

i

PS

PS

PS

о о

О

О

рого блоков оперативной памяти, с управляющими входами элементов И первой группы и регистра регенерации, отличающееся тем, что, с целью повыщения производительности за счет увеличения скорости обработки слов переменной длины, оно содержит два щифратора, группу элементов ИЛИ, два дещифратора, сумматор, коммутатор,

i информационными выходами усилителей считывания первой группы, а выходами - с первыми входами элементов И второй группы и регистра регенерации, а также с информационными входами элементов И первой группы, выходы усилителей считывания второй группы соединены с первым входом сумматора, второй вход которого соединен со вторым информационным входом регистра регенерации и со вторым выходом регистра адреса, управляющие входы усилителей

t считывания первой группы соединены с выходами соответствующих элементов ИЛИ группы, первые входы которых соединены с соответствующими выходами первого щифратора, а вторые - с соответствующими выходами второго щифратора, одноименные

информационные входы первого и второго щифраторов соединены между собой, со вторыми входами соответствующих элементов И второй группы и с соответствующими выходами первого дещифратора, вход которого соединен с третьим выходом регистра команд и с третьим входом дещифратора микрокоманд, выход сумматора через второй дещифратор соединен с управляющими входами коммутатора.

50

Источники информации, принятые во внимание при экспертизе

1 Авторское свидетельство СССР № 583475, кл. G 11 С 11/00, 1977. S5 2. Авторское свидетельство СССР

№ 268498, кл. G 11 С 11/02, 1970 (прототип) .

Авторы

Даты

1981-04-30—Публикация

1979-08-30—Подача