Изобретение относится к вычислительной технике и может быть использовано Б различных цифровых вычислительных системах обработки информации. Известно каскадное устройство быстро го преобразования Фурье, содержащее И блоков памяти, соединенных последовател но, И арифметических блоков, каждый из которых соединен входом (выходом) с вьрсодом (входом) соответствующекр блока памяти l. Наиболее близким по технической сущности и достигаемому результату к изобретению является каскадньй процессор, содержащий VI арифметических блоков, две группы по Y блоков памяти последовательного Доступа, i -ые блоки памяти последовательного доступа соединены соответственно со входами i -го арифметического блока, выходы которого соединен с первыми входами ( it- 1) -ых блоков памяти последовательного доступа,, выход i-ro арифметического блока соединен с третьим входом ( i + 1)-го арифме- тического блока, четвертый вход i -го арифметического блока является входом ввода констант, при этом входы первых блоков памяти и третий вход первого арифметического блока соединены со вхо дом процессора 2. Недостатком этиз{ устройств являются узкие функциональные возможности, которью заключаются в следующем; их структура рассчитана на одну длину исходного массива, что существенно снижает применяемость таких процессоров; ввод исходного массива информации и вывод массива результата проводятся в различном порядке следования операндов массивов, что при значительном быстродействии каскадных процессоров выливается в дополнительное оборудование для переиндексации массивов; невозможность на том же оборудовании производить весовую обработку и вычноление корреляционных функций. Цель изобретения - расширение функциональных возможностей за счет вычнслвния корпекционных функций, а также за счет возможности ввода и вывода информации в любом порядке

Это достисгается тем, что в каскадный процессор спектральной обработки сигналов, содержащий И арифметических блоков, две группы по и блоков памяти последовательного доступа, выходы -i -к блоков памяти последовательного дсстугЕа первой и второй групп соединены СОСУТветфтвенно с первым и вторым входамк 1 -го арифмшического блока, первый и второй выходы которого (кроме соединены с первыми входами (i i-i)-K блоков памяти последовательного доступа соответственно первой и второй группы третий выход т-го арифметического блока кроме (и-1)-го и .П ГО арифмети-ггеских блоков, подключен к третьему входу

( fl)-ro арифметического блока, третий Вход первого арифметического блоха соедилен со входом ввода констант процэссора, введены коммутатор, блок памяти произвользного доступа, индексный блок памяти,

1ретья группа из Y блоков памяти довательного доступа причем вход ввода констант процессора соединен с иервыми входами ()-х блоков памяти последовательного доступа третьей групшлр выходы которых соединены соответственно со своими вторыми входами и с четвертыми входами {-i-t-l -x арифмет гчески блоков, первый выход блока памяти произвольного доступа соединен через (И-1)ый блок памяти произвольного доступа третьей группы с пер вым входом коммутатора, через п-ый блок памяти произвольного доступа третьей гругшы со вторым входом коммутатора и непосредственно с третьим входом Y -го арифметического блока, первый и втрой выходы которого соединены соответственно с первым и вторым входаш блоки памяти произвольного доступа и с первым и вторыми вы ход а ми процессора, третий выход блока памяти произвольного -isjcryii подключен ко второму входу VI-го блока памяти последовательного в оступа. третьейгруппы, к четвертому входу И-го арифметвнеского блока к к третьемзг входу коммутатора, выход которого является третьим выходом процессора, первый к второй выход первого арифметического блока соединены со вторыми входами Кь блокоБ памяти последовательного доступа соответственно первой и второй группы, а его четвертый вход является входом процессора.

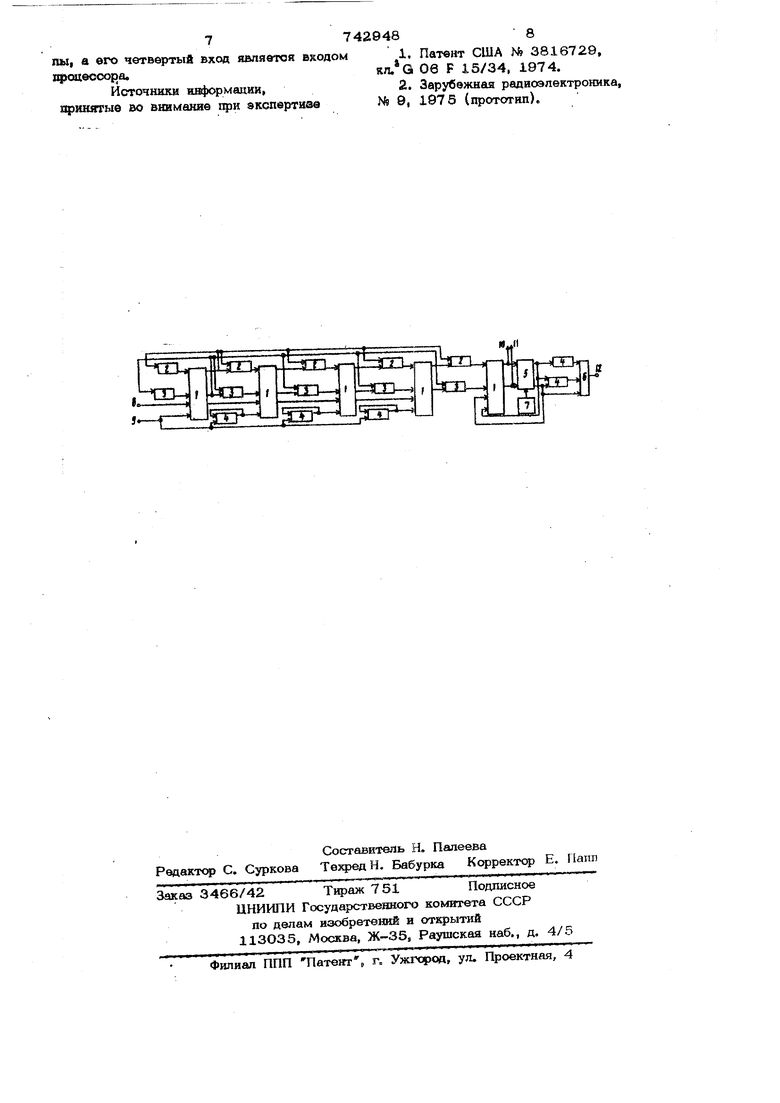

На чертежа приведена блок-схема каска :1кого процессора спектральной обработки сигна.лов.

Процессор содержит арифметические баски .1, блоки. 2, 3 и 4 памяти последовательного доступа, блок 5 памяти проiKEcau iorx доступа, коммутатор 6, шадек: ...;; блок 7 5 вход 8 лроцессора, вход 9 ;:i::Cv- a кскстажг процессора, выходы 1О, ,1 i ;:. 1.2 процбссорэ... Приведеш ый вариакт ст-рукт;;гры рассчитан на ы&кстлальпую длкку ;еходного массива в Н 64 точки.

процессор рвбот-ает следую-

г./ cCj-OtiSOfvI

По входу 8 в процессор подается ксэсод:еш й масс;ш, который первым арифметйчеслнм блоком умножаете и на константы ьесовок iffywaiMK, поступающие по вход 9 1о же входу 9 во время весовсй обработки в первом арифметическом блоке в процессор поступают необхоаим- ш константы для прове.а,ения прямого л.кбо обрйтного преобразованкя Фурье. Эти коксгаяты поступают в баокк 4 паiyjETH последовательного доступа.

Рзаультат Бесовой обработ-ки в первом арифметическом блоке по первому и второму .выходу этого блока распределяется в соответст.зующке б.чокк2иЗ памяти поледоаатель.чого .р.оступа Порядок поступления эяементов (отдельных операндов) ;4С51одного массива может быть любым, Е том числе озш мопут поступать в естесстве.гшоьл порядке В какой конкретно блок памяти из 3 и 4-ой группы будут записываться очередные операнды определяются блоков: упре ления всего устройства, который на чертеже не показан. Для того ч .гобы процессор мог приступить к своей оснойкой опередии; в его блоках памяти .должны находиться сам исходный массив (либо умясжояьи:;й на весовую функцию) % Cic), k Оз1.-,. N-1 и массив конста -ы ( j -;р-),К.-О,М--1Блоа 5 лтамят;;: прокапсльнего доступа под управлением индексного б.1ока мгноrciffpesTKo записывает:- промежуточные результаты и .выдает их на последний ариф 1ет41че(31шй блок 1с

f.5осг,сдшг8 др. а блока 4 памяти последовательно х) доотупа совместно с коммутаторо1Л 6 обеспечивают выдачу результата (дискретного спектра Фурье) в естественном ,ке следования.

При необходимости вынисленкк взаимн корреляционной функцки требуется обеспб;-;: гть вычисление; прямое дискретное преобразование Фурье, результат умножить на опорный спектр и наконец провести обратное дискретное преобразование Фурье от произведения. Так, результат с промежуточных выходов 10, 11 можно сразу завести на вход 8 и вводить через первое арифметическое уст ройство, которое к этому моменту време ни закончило свою работу по прямому дискретному преобразованию Фурье (первый этап). На втором этапе это арифметическое устройство обеспечит умножение результата первого этапа на опорный спект и устройство управления разнесет произв дение по соответствующим блокам памят второй группы. Далее процессор обеспечи вает выполнение обратного дискретного преобразования Фурье. Автокорреляционная функция вычисляется аналогично, только в начале второго этана вычислений первый арифметический блок от каждого комплексного значения в массиве результата первого этапа биределит модуль. Каскадный процессор может работать и с меньшими массивами исходной инфор мации. Если процессор содержит Т арифметических блоков, то это значит максимальный размер массива комплексных чисел, с которым он может работать, равен . В случае подачи на его в меньшего массива, он устройством управления распределяется в старшие блоки памяти второй группы (начал® счета блоков со входа nponisccopa). Работа процессора в этом случае по реализации алгоритма быстрого преобразования Фурь длится во столько раз быстрее, во сколь ко раз исходнь1Й массив меньше максимального, на который расчитан каскадный процессор. Таким образом, изобретение позволяе существенно расширить практически на том же оборудовании функциональные воз можности каскадного процессора. Каскад ный процессор может вычислять спектр и корреляционные функции с любым, массивом исходной информации, не превышающим , где Щ- число каскадов в процессоре. Ввод и вы вод информации обес печивается в процессоре в естественном порядке. Расширение функциональных возможностей каскадного процессора спектральной обработки сигналов позволяет расширить область его применения. Формула изобретения Каскадный процессор спектральной обра ботки сигналов,содержащий п арифметических блоков, две группы по И блоков па мяти последовательного доступа, выходы i -X блоков памяти последовательного доступа первой и второй групп соединены соответственно с первым и вторым входами i -го арифметического блока, первый и второй выходы каждого (кроме И-го), соединены с первыми входами ( i +1 )-х блоков памяти последовательного доступа соответственно первой и второй группы, третий выход i -го арифметического блока, кроме (n-l)-ro арифметических блоков, подключен к третьему Входу (i +1)-го арифметического блока, третий вход первого арифметического блока соединен со входом ввода констант процессора, отличающийся тем, что. с целью расширения функциональных возможностей за счет вычисления корреляционных функций, а также за счет возможности ввода и вывода информации в любом порядке, в него введены коммутатор, блок памяти произвольного доступа, индексный блок памяти, третья группа из Я блоков памяти последовательного доступа, причем вход ввода констант процессора соединен с первыми входакет (h-2)-x блоков памяти последовательного доступа третьей группы, выходы которых соединены соответственно со своими вторыми входами ;И с четвертыми входами ()x арифметических блоков, первый выход блока памяти произвольного доступа соединен через(п -1) ый блок памяти произвольного доступа третьей группы с первым входом коммутатора, через 7-ый блок памяти произвольного доступа третьей группы со вторым входом коммутатора и непосредственно с третьим входом и -го арифметического блока, первый и втсрой выходы которого соединены . соответственно с первым и вторым входами памяти произвольного доступа и с первым и вторым выходами процессора, третий выход блока памяти произвольного дсхггупа подключен ко второму входу /| -го блока памяти последовательного доступа третьей группы, к четвертому входу h-ro ифметического блока и к третьему входу коммутатора, выход которого являет третьим выходом процессора, первый и второй выход, первого арифметического. блока соединены со вторыми входамиИ блоков памяти последовательного доступа соответственно первой и второй груп-

77429488

1Ш, а его четвертый вход является входом1. Патент США 3816729,

iqjoueccofja.кл. G 06 F 15/34, 1974.

Источники информации,2. Зарубежная радиоэлектроника,

арикягые во внимание при экспертиавNj 8, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Каскадное устройство быстрого преобразования фурье | 1978 |

|

SU723584A1 |

| Программируемый процессор спектральной обработки сигналов | 1978 |

|

SU744603A1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734708A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734707A1 |

| Многоканальное устройство для определения координат множества одновременно действующих источников акустических сигналов | 1984 |

|

SU1201753A1 |

| Устройство для вычисления преобразования Уолша (его варианты) | 1982 |

|

SU1075269A1 |

| Процессор быстрого преобразования Фурье | 1980 |

|

SU928362A1 |

| Программируемый процессор спектральной обработки сигналов | 1982 |

|

SU1092517A1 |

я.

Авторы

Даты

1980-06-25—Публикация

1978-01-06—Подача