Изобретение относится к радиотех нике и может использоваться в когерентно-импуль сных радиолокационных станциях. Известно цифровое устройство для подавления пассивных помех, содержа щее два канала, каждый из которых состоит из трех основных перемножителей, сумматора и последовательно соединенных фазового детектора, ана лого-цифрового преобразователя, пер вого и второго блоков памяти, приче первые входы фазовых детекторов каналов объединены, а выходы первого блока памяти и аналого-цифрового преобразователя подк.71ючены соответственно ко входу первого основного перемножителя и первому входу сумматора, второй и третий входы которого соединены соответственно с выходами второго и третьего основных перемножителей, при этом на вторые входы фазовых детекторов поданы опорные сигналы 1. Однако известное цифровое устрой ство не обеспечивает достаточной эффективности подавления пассивных /помех. Цель изобретения - повышение эффективности подавления пассивных помех.. Для этого в цифровое устройство для подавления пассивных помех, содержащее два канала, каждый из которых состоит из трех основных перемножителей, сумматора и последовательно соединенных фазового детектора, аналого-цифрового преобразователя, первого и второго блоков памяти, причем первые входы фазовых детекторов каналов объединены, а выходы первого блока памяти и аналого-цифрового преобразователя подключены соответственно ко вхОду первого основного перемножителя и первому входу сумматора, второй и третий входы которого соединены соответственно с выходами второго и третьего основных перемножителей, при этом на вторые входы фазовых детекторов поданы опорные сигналы, введены вычислительный блок и последовательно соединенные блок измерения и усреднения междупериодного сдвига фазы помехи и функциональный преобразователь, а в каждый канал введены два дополнительных перемножителя, причем первый вход

по,;,зого дополнительного перемножителя одного канала соединен с выходом второго блока памяти другого канала, первый вход и выход второго дополнительного перемНожителя соединены соответственно с выходом второго блока памяти и одним из дополнительных входов сумматора, другой дополнительный вход которого соединен с выходом первого дополнительного.перемножителя, а вторые входы дополнительных перемножителей соединены с выходами вычислительного блока, ко входу кот.орого подключен выход блока измерения и усреднения междупе иодного сдвига .фазы помехи, входы которого соединены соответственно с выходами аналогоцифровых преобразователей и первых блоков памяти, при этом выход -первого основного перемножителя одного канала подключен к первому входу третьего основного перемножителя этого же канала и первому входу второго основного перемножителя другого канала, а вторые входы вторых и третьи .основных перемножителей соединены с выходами функционального Преобразователя, при этом блок измерения и усренения междупериодного сдвига фазы помехи содержит последовательно соединенные делитель, функциональный преобразователь и логический блок, соответствующие входы которого соединены со входами делителя, а также два канала, каждый из которых- состоит из первого накопителя, первого перемножителя и последовательно соединенных второго накопителя, второго перемножителя и- усредняющего сумматора, выход которого подключен к соответствующему входу делителя, при этом второй вход усредняющего сумматора одного канала соединен с выходом первого перемножителя другого канала, входы которого соединены с выходами первого и второго накопителей, причем входы накопителей являются входами блока измерения и усреднения междупериодного сдвига фазы помехи, выходом которого является выход логического блока, при этом .вычислительный блок содержит последовательно соединенные блок памяти, сумматор и функциональный преобразователь, выходы которого являются выходами вычислительного блока, входом которого является вход блока памяти, соединенный с вторым входом сумматора.

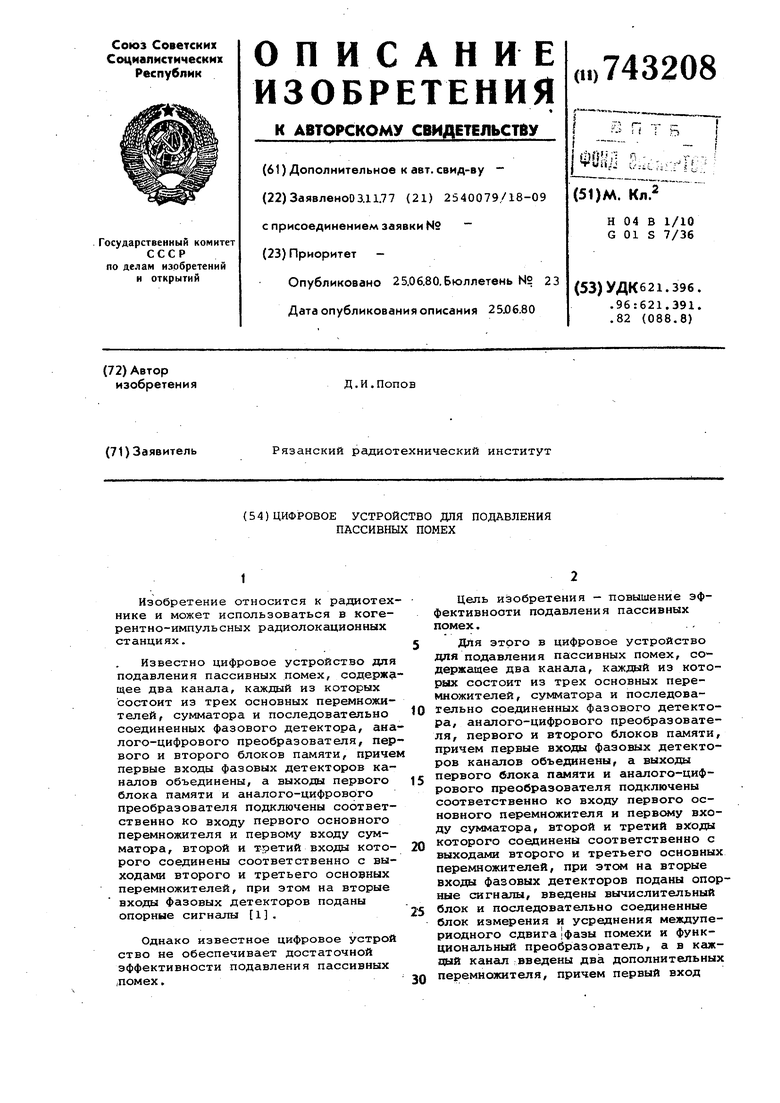

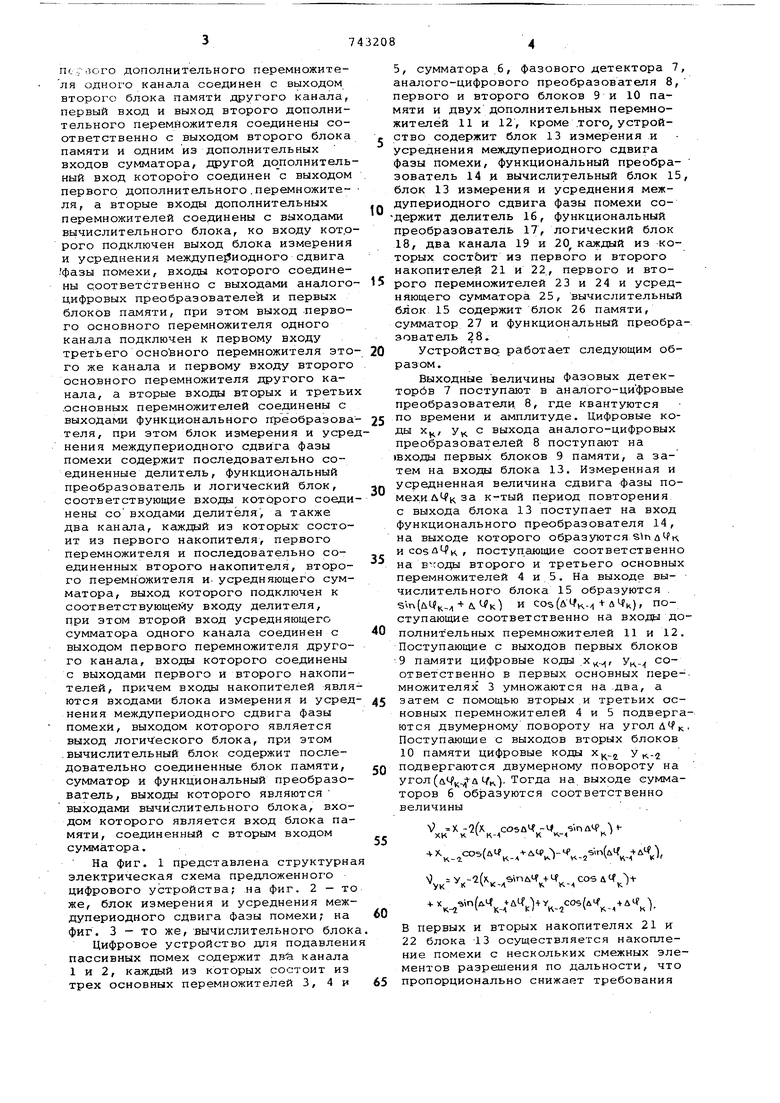

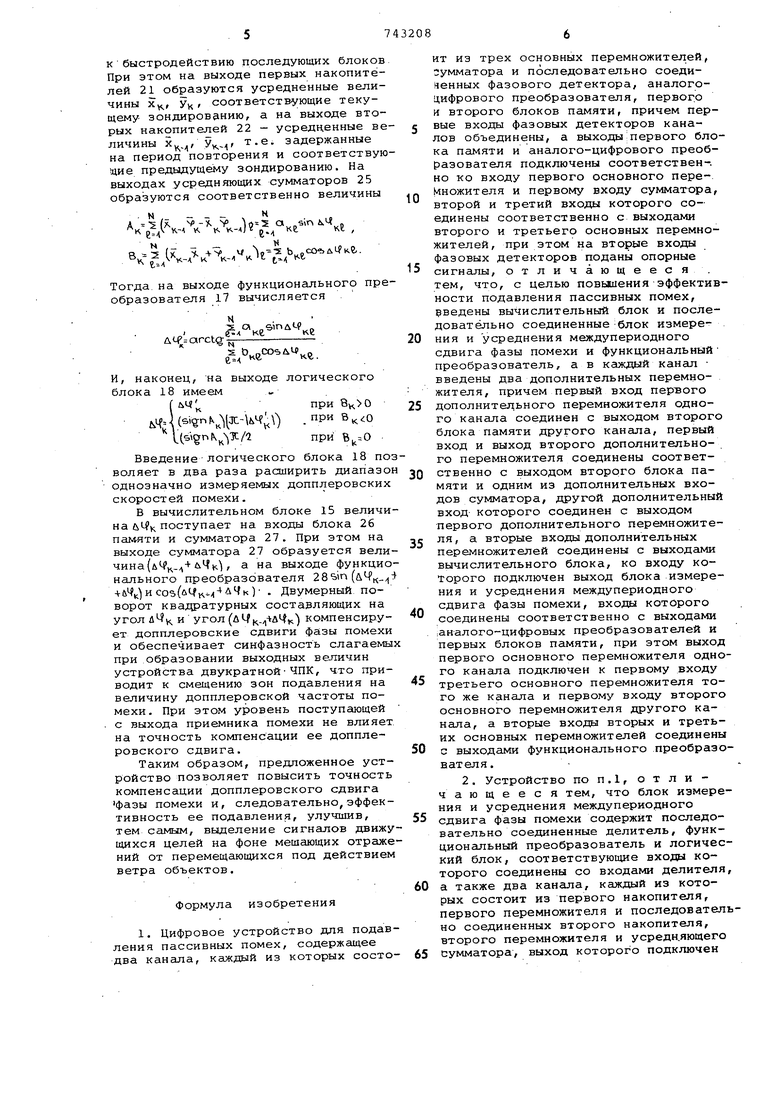

На фиг. 1 представлена структурна электрическая схема предложенного цифрового устройства; на фиг. 2 - то же, блок измерения и усреднения междупериодного сдвига фазы помехи; на фиг. 3 - то же, вычислительного блока

Цифровое устройство для подавлени пассивных помех содержит дв-а канала 1 и 2, ка.ждый из которых состоит из трех основных перемножителей 3, 4 и

5, сумматора 6, фазового детектора 7 аналого-цифрового преобразователя 8, первого и второго блоков 9 и 10 памяти и двух дополнительных перемножителей 11 и 12, кроме .того, устройство содержит блок 13 измерения и усреднения междупериодного сдвига фазы помехи, функциональный преобразователь 14 и вычислительный блок 15 блок 13 измерения и усреднения междупериодного сдвига фазы помехи содержит делитель 16, функциональный преобразователь 17, логический блок 18, два канала 19 и 20 каждый из которых состЬит из первого и второго накопителей 21 и 22, первого и второго перемножителей 23 и 24 и усредняющего сумматора 25, вычислительный блок 15 содержит блок 26 памяти, сумматор 27 и функциональный преобразователь 28.

Устройства работает следующим образом.

Выходные величины Фазовых детекторбв 7 поступают в аналого-цифровые преобразователи. 8, где квантуются по времени и амплитуде. Цифровые ко К УК выхода аналого-цифровых преобразователей 8 поступают на шходы первых блоков 9 памяти, а затем на входы блока 13. Измеренная и усредненная величина сдвига фазы помехи дМ к за к-тый период повторения с выхода блока 13 поступает на вход функционального преобразователя 14, на выходе которого образуются л 4. и соедЧк, , поступающие соответственно на вгоды второго и третьего основных перемножителей 4 и 5. На выходе вычислительного блока 15 образуются . sm{ul -b ) и cosfuLfKM )f поступающие соответственно на входы дополнительных перемножителей 11 и 12. Поступающие с выходов первых блоков -9 памяти цифровые коды х,., у соответственно в первых основных перемножителях 3 умножаются на два, а затем с помощью вторых и третьих основных перемножителей 4 и 5 подвергаются двумерному повороту на уголд Поступающие с выходов вторых блоков 10 памяти цифровые коды х. У к-2 подвергаются двумерному повороту на угол ( Тогда на выходе сумматоров б образуются соответственно величины . .

.,

(.,(),

V к-( .V

Х,1ПИ.Д).У.С05(Д,.Л.

В первых и вторых накопителях 21 и 22 блока -13 осуществляется накопление помехи с нескольких смежных элементов разрешения по дальности, что пропорционально снижает требования кбыстродействию последующих блоков При этом на выходе первых накопителей 21 образуются усредненные величины х, у, соответствующие текущему зондированию, а на выходе вторых накопителей 22 - усредненные ве личины х., у, т.е. задержанные на период повторения и соответствую дие предыдущему зондированию. На выходах усредняющих сумматоров 25 образуются соответственно величины А 5 (Я . Y а sin J „ . ке. кг , N ч « В 2 (х - -VV W --5 Ь„рСО й1 ке,. к {t - - - fl Тогда на выходе функционального пре образователя 17 вычисляется Atf arctq; .,. и, наконец, на выходе логического блока 18 имеем Введение логического блока 18 по воляет в два раза расширить диапазо однозначно измеряемых допплеровских скоростей помехи. В вычислительном блоке 15 величи на uL поступает на входы блока 26 памяти и сумматора 27. При этом на выходе сумматора 27 образуется вели чина (л, лЧк , а на выходе функцио нального преобразователя (лЧц -к)и со5() Двумерный поворот квадратурных состазляющих на угол . и угол (.-VA4i) компенсирует допплеровские сдвиги фазы помехи и обеспечивает синфазность слагаемы при образовании выходных величин устройства двукратной-ЧПК, что приводит к смещению зон подавления на величину допплеровской частоты помехи. При этом уровень поступающей с выхода приемника помехи не влияет на точность компенсации ее допплеровского сдвига. Таким образом, предложенное устройство позволяет повысить точность компенсации допплеровского сдвига фазы помехи и, следовательно, эффективность ее подавления, улучшив, тем самым, выделение сигнашов движу щихся целей на фоне мешающих отраже ний от перемещающихся под действием ветра объектов. Формула изобретения 1. Цифровое устройство для подав ления пассивных помех, содержащее два канала, каждый из которых состо ит из трех основных перемножителей, зумматора и последоватегльно соедиЯенных фазового детектора, аналогоцифрового преобразователя, первого и второго блоков памяти, причем первые входы фазовых детекторов каналов объединены, а выходы первого блока памяти и аналого-цифрового преобС азователя подключены соответствен-, но ко входу первого основного переМножителя и первому входу сумматора, второй и третий входы которого соединены соответственно с выходами второго и третьего основных перемножителей, при этом на вторые входы фазовых детекторов поданы опорные сигналы, отличающеес я. тем, что, с целью повышения эффективности подавления пассивных помех, введены вычислительный блок и последовательно соединенные блок измерения и усреднения междупериодного сдвига фазы помехи и функциональный преобразователь, а в каждый кангш введены два дополнительных перемножителя, причем первый вход первого дополнительного перемножителя одного канала соединен с выходом второго блока памяти другого канала, первый вход и выход второго дополнительного перемножителя соединены соответственно с выходом второго блока памяти и одним из дополнительных входов сумматора, другой дополнительный вход которого соединен с выходом первого дополнительного перемножителя, а вторые входы дополнительных перемножителей соединены с выходами вычислительного блока, ко входу которого подключен выход блока измерения и усреднения междупериодного сдвига фазы помехи, входы которого соединены соответственно с выходами |аналого цифровых преобразователей и первых блоков памяти, при этом выход первого основного перемножителя одного канала подключен к первому входу третьего основного перемножителя того же канала и первому входу второго основного перемножителя другого канала, а вторые входы вторых и третьих основных перемножителей соединены с выходами функционального преобразователя . 2. Устройство ПОП.1, отличающеес я тем, что блок измерения и усреднения междупериодного сдвига фазы помехи содержит последовательно соединенные делитель, функционсшьный преобразователь и логический блок, соответствующие входы которого соединены со входами делителя, а также два канала, каждый из которых состоит из первого накопителя, первого перемножителя и последовательно соединенных второго накопителя, второго перемножителя и усредняющего сумматора, выход которого подключен

к соответс.твующему входу делителя, при этом второй вход усредняивдего сумматора одного канала соединен с выходом первого перемножителя другого канала, входы которого соединены с выходами первого и второго накопителей, причем входы накопителей являются входами блока измерения и усреднений междупериодного сдвига фазы помехи, выходом которого является выход логического блока.

3, Устройство ПОП.1, отличающееся тем, что вычислительный блок содержит последовательно соединенные блок памяти, сумматор и функциональный преобразователь, выходы которого являются выходами вычислительного блока, входом которого является вход блока памяти, соединенный с вторым входом сумматора.

Источники информации, принятые во внимание при экспертизе

1. Лихарев В.А. Цифровые методы и устройства в радиолокации. М., Советское радио , 1975, с. 135 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для подав-лЕНия пАССиВНыХ пОМЕХ | 1979 |

|

SU809018A1 |

| Устройство для подавления пассивных помех | 1976 |

|

SU578781A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1977 |

|

SU778514A2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛА | 2012 |

|

RU2498343C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1977 |

|

SU1015757A1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1977 |

|

SU711849A1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2409822C1 |

| РЕЖЕКТОРНЫЙ ФИЛЬТР | 1980 |

|

SU934816A1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1980 |

|

SU875960A2 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

Г

I

I

1

I

L Г

Авторы

Даты

1980-06-25—Публикация

1977-11-03—Подача