Изобретение относится к радиолокации и может использоваться в когерентно-импульсных радиолокационных станциях для подавления мешающих отражений от перемещающихся под действием ветра дипольных отражателей или метеообразований.

Известно устройство подавления пассивных помех, содержащее последовательно включенные блок измерения и усреднения междупериодного сдвига фазы помехи, блок вычисления полного сдвига фазы помехи и функциональный преобразователь, а также первый и второй каналы, каждый из которых содержит первый перемножитель и последовательно включенные второй перемножитель, сумматор и режекторный фильтр, при этом в каждом из каналов выход первого перемножителя соединен с вторым входом сумматора, а первые входы первого и второго перемножителей обоих каналов попарно соединены между собой и с одноименным из выходов функционального преобразователя, причем блок измерения и усреднения междупериодного сдвига фазы помехи содержит последовательно включенные блок деления, функциональный преобразователь и логический блок, а также первый и второй каналы, каждый из которых содержит накопитель, первый перемножитель и последовательно включенные второй перемножитель, сумматор и блок усреднения, в каждом из каналов первые входы первого и второго перемножителей соединены между собой, выход накопителя первого канала соединен с вторыми входами первых перемножителей обоих каналов, выход накопителя второго канала соединен с вторыми входами вторых перемножителей обоих каналов, выход блока усреднения первого канала соединен с первым входом блока деления и вторым входом логического блока, выход блока усреднения второго канала соединен с вторым входом блока деления и третьим входом логического блока, а выход первого перемножителя одного канала соединен с вторым входом сумматора другого канала, причем первым и вторым входами и выходом блока измерения и усреднения междупериодного сдвига фазы помехи соответственно являются вход накопителя первого канала, вход накопителя второго канала и выход логического блока, блок вычисления полного сдвига фазы помехи содержит последовательно включенные блок сложения, нормализатор и блок памяти, выход которого соединен с первым входом блока сложения, при этом входом и выходом блока вычисления полного сдвига фазы помехи соответственно являются второй вход блока сложения и выход нормализатора [1].

Однако известное устройство имеет большую динамическую ошибку при компенсации помехи, имеющей доплеровское смещение средней частоты, так как введение соответствующей компенсирующей поправки с учетом задержек в разных цепях, а именно в накопителях и сглаживающем фильтре, осуществляется для элементов разрешения, находящихся за пределами той группы элементов, по которой производилось определение сигнала рассогласования, и имеющих свою величину доплеровкой скорости помехи.

Цель изобретения - уменьшение динамической ошибки.

Для этого в устройство подавления пассивных помех, содержащее последовательно включенные блок измерения и усреднения междупериодного сдвига фазы помехи, блок вычисления полного сдвига фазы помехи и функциональный преобразователь, а также первый и второй каналы, каждый из которых содержит первый перемножитель и последовательно включенные второй перемножитель, сумматор и режекторный фильтр, при этом в каждом из каналов выход первого перемножителя соединен с вторым входом сумматора, а первые входы первого и второго перемножителей обоих каналов попарно соединены между собой и с одноименным из выходов функционального преобразователя, причем блок измерения и усреднения междупериодного сдвига фазы помехи содержит последовательно включенные блок деления, функциональный преобразователь и логический блок, а также первый и второй каналы, каждый из которых содержит накопитель, первый перемножитель и последовательно включенные второй перемножитель, сумматор и блок усреднения, в каждом из каналов первые входы первого и второго перемножителей соединены между собой, выход накопителя первого канала соединен с вторыми входами первых перемножителей обоих каналов, выход накопителя второго канала соединен с вторыми входами вторых перемножителей обоих каналов, выход блока усреднения первого канала соединен с первым входом блока деления и вторым входом логического блока, выход блока усреднения второго канала соединен с вторым входом блока деления и третьим входом логического блока, а выход первого перемножителя одного канала соединен с вторым входом сумматора другого канала, причем первым и вторым входами и выходом блока измерения и усреднения междупериодного сдвига фазы помехи соответственно являются вход накопителя первого канала, вход накопителя второго канала и выход логического блока, блок вычисления полного сдвига фазы помехи содержит последовательно включенные блок сложения, нормализатор и блок памяти, выход которого соединен с первым входом блока сложения, при этом входом и выходом блока вычисления полного сдвига фазы помехи соответственно являются второй вход блока сложения и выход нормализатора, в каждый из каналов введен блок задержки, вход которого соединен с соответствующим из входов блока измерения и усреднения междупериодного сдвига фазы помехи, а выход - с вторым входом второго перемножителя одноименного канала и с вторым входом первого перемножителя другого канала, а в каждый их каналов блока измерения и усреднения междупериодного сдвига фазы помехи введен блок памяти, включенный между выходом накопителя и первым входом первого перемножителя, накопитель содержит генератор импульсов и последовательно включенные блок памяти, сумматор и элемент И, второй вход которого соединен с тактовым входом блока памяти и выходом генератора импульсов, а выход сумматора соединен с информационным входом блока памяти, при этом входом и выходом накопителя соответственно являются второй вход сумматора и выход элемента И, блок усреднения содержит N последовательно включенных блоков задержки, выходы которых и вход первого из которых соединены с соответствующими входами сумматора, при этом входом и выходом блока усреднения соответственно являются вход первого из N блоков задержки и выход сумматора.

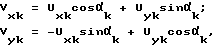

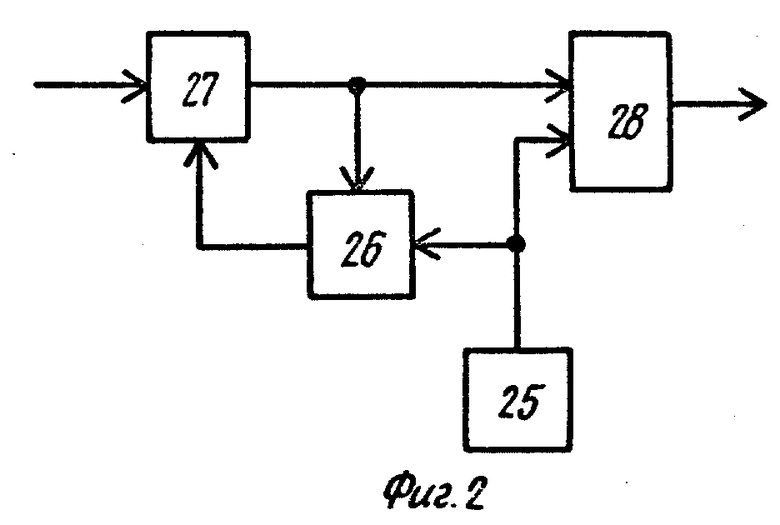

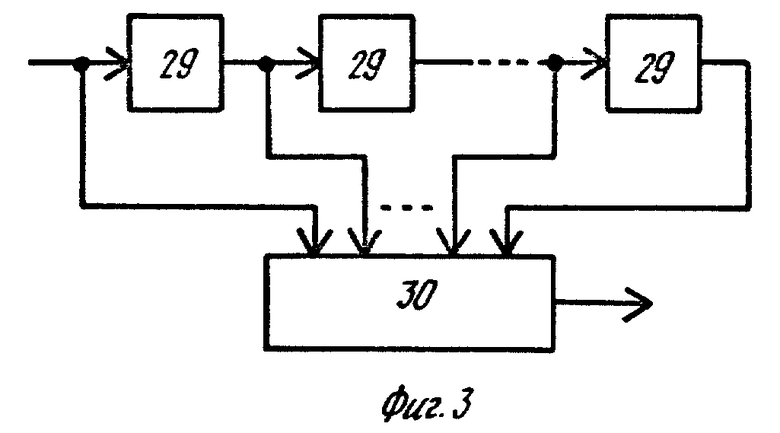

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная электрическая схема накопителя; на фиг. 3 - структурная электрическая схема блока усреднения.

Устройство подавления пассивных помех содержит блок 1 измерения и усреднения междупериодного сдвига фазы помехи, блок 2 вычисления полного сдвига фазы помехи, функциональный преобразователь 3, первый и второй каналы 4 и 5, каждый из которых содержит первый и второй перемножители 6 и 7, сумматор 8, режекторный фильтр 9 и блок 10 задержки, блок 1 измерения и усреднения междупериодного сдвига фазы помехи содержит блок 11 деления, функциональный преобразователь 12, логический блок 13 и первый и второй каналы 14 и 15, каждый из которых содержит накопитель 16, блок 17 памяти, первый и второй перемножители 18 и 19, сумматор 20 и блок 21 усреднения, блок 2 вычисления полного сдвига фазы помехи содержит блок 22 сложения, нормализатор 23 и блок 24 памяти, накопитель 16 содержит генератор 25 импульсов, блок 26 памяти, сумматор 27 и элемент И 28, блок 21 усреднения содержит N блоков 29 задержки и сумматор 30.

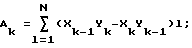

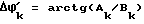

Устройство подавления пассивных помех работает следующим образом. Цифровые коды квадратурных составляющих полезного сигнала и пассивной помехи или только одной помехи с выходов аналого-цифровых преобразователей (на фиг. 1 не показаны) или предыдущих каскадов режекции помехи (на фиг.1 не показаны) поступают на входы накопителей 16 и блоков 10 задержки. В накопителях 16 осуществляется накопление помехи с нескольких смежных элементов разрешения по дальности, что пропорционально снижает требования к быстродействию последующих блоков. С выходов накопителей 16 цифровые коды Xк, Yк, соответствующие текущему зондированию, поступают на вторые входы первого и второго перемножителей 18 и 19, на первые входы которых с выходов блоков 17 памяти поступают цифровые коды Xк-1, Yк-1, соответствующие предыдущему зондированию, т.е. задержанные на период повторения. Выходные величины сумматоров 20 поступают на входы блоков усреднения 21, в которых осуществляется скользящее вдоль дальности равновесное суммирование поступающих кодов и образуются соответственно величины

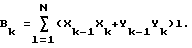

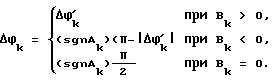

Величины Ак и Вк с выходов блоков 21 усреднения поступают на соответствующие входы блока 11 деления и логического блока 13. На выходе функционального преобразователя 12 вычисляется допплеровский сдвиг фазы помехи за k-й период повторения  . На выходе логического блока 13 имеем

. На выходе логического блока 13 имеем

Логический блок 13 позволяет в два раза расширить диапазон однозначно измеряемых доплеровских скоростей помехи.

Итак, на выходе логического блока 13 образуется величина усредненного по N отсчетам доплеровского сдвига Δϕk за текущий (k-й) период повторения. В блоке 22 раздельно по каждому элементу или группе элементов решения по дальности эта величина суммируется с соответствующей выходной величиной блока 24 памяти, в результате чего на выходе блока 22 образуется величина полного сдвига фазы помехи за k периодов повторения

Если полный сдвиг по абсолютной величине превышает 2π, то в нормализаторе 23 из него вычитается 2π. С выхода нормализатора 23 полученная величина поступает на входы блока 24 памяти и функционального преобразователя 3, на выходах которого образуются величины sinαk и cosαk. С помощью первого и второго перемножителей 6 и 7 и сумматоров 8 осуществляется компенсация полного доплеровского сдвига αk путем двухмерного поворота поступающих с выходов блоков 10 задержки исходных квадратурных составляющих Uхk, Uуk на тот же угол, но в противоположном направлении. В результате этого квадратурные составляющие помехи на выходе сумматоров 8 определяются в соответствии с выражениями

и практически не содержат доплеровской модуляции.

В режекторном фильтре 9 происходит режектирование помехи и выделение сигналов движущихся целей.

Накопитель 16 образует сумму нескольких, например четырех, последовательно поступающих с соседних элементов разрешения по дальности кодов. В результате накопления темп поступления данных снижается в 4 раза, что пропорционально снижает объем блоков 17 памяти и значительно упрощает техническую реализацию первого и второго перемножителей 18 и 19, сумматоров 20 и блоков 21 усреднения.

Сравнительный анализ известного и предложенного устройства показал, что использование предложенного устройства обеспечит полную компенсацию доплеровской скорости помехи, что позволяет осуществить режектирование помехи с помощью произвольного режекторного фильтра 9, т.е. такого фильтра, на структуру, тип (рекурсивный или нерекурсивный) и порядок которого не накладывают каких-либо ограничений, кроме требований реализации заданного качества режектирования. При этом соответствующим выбором величины задержки в блоках 10 задержки обеспечивается соответствие между исходными доплеровскими сдвигами помехи и вводимыми с целью их компенсации первым и вторым перемножителями 6 и 7 и сумматором 8, что приводит к повышению точности компенсации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1977 |

|

SU711849A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1982 |

|

SU1090136A1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1980 |

|

SU875960A2 |

| РЕЖЕКТОРНЫЙ ФИЛЬТР | 1980 |

|

SU934816A1 |

| Цифровое устройство для подав-лЕНия пАССиВНыХ пОМЕХ | 1979 |

|

SU809018A1 |

| Цифровое устройство для подавления пассивных помех | 1977 |

|

SU743208A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1977 |

|

SU778514A2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2409822C1 |

| УСТРОЙСТВО АДАПТИВНОЙ РЕЖЕКЦИИ ПАССИВНЫХ ПОМЕХ | 1981 |

|

SU1098399A1 |

1. Устройство подавления пассивных помех, содержащее последовательно включенные блок измерения и усреднения междупериодного сдвига фазы помехи, блок вычисления полного сдвига фазы помехи и функциональный преобразователь, а также первый и второй каналы, каждый из которых содержит первый перемножитель и последовательно включенные второй перемножитель, сумматор и режекторный фильтр, при этом в каждом из каналов выход первого перемножителя соединен с вторым входом сумматора, первые входы первого и второго перемножителей обоих каналов попарно соединены между собой и с одноименным из выходов функционального преобразователя, причем блок измерения и усреднения междупериодного сдвига фазы помехи содержит последовательно включенные блок деления, функциональный преобразователь и логический блок, а также первый и второй каналы, каждый из которых содержит накопитель, первый перемножитель и последовательно включенный второй перемножитель, сумматор и блок усреднения, в каждом из каналов первые входы первого и второго перемножителей соединены между собой, выход накопителя первого канала соединен с вторыми входами первых перемножителей обоих каналов, выход накопителя второго канала соединен с вторыми входами вторых перемножителей обоих каналов, выход блока усреднения первого канала соединен с первым входом блока деления и вторым входом логического блока, выход блока усреднения второго канала соединен с вторым входом блока деления и третьим входом логического блока, а выход первого перемножителя одного канала соединен с вторым входом сумматора другого канала, причем первым и вторым входами и выходом блока измерения и усреднения междупериодного сдвига фазы помехи соответственно являются вход накопителя первого канала, вход накопителя второго канала и выход логического блока, блок вычисления полного сдвига фазы помехи содержит последовательно включенные блок сложения, нормализатор и блок памяти, выход которого соединен с первым входом блока сложения, при этом входом и выходом блока вычисления полного сдвига фазы помехи соответственно являются второй вход блока сложения и выход нормализатора, отличающееся тем, что, с целью уменьшения динамической ошибки, в каждый из каналов введен блок задержки, вход которого соединен с соответствующим из входов блока измерения и усреднения междупериодного сдвига фазы помехи, а выход - с вторым входом второго перемножителя одноименного канала и с вторым входом первого перемножителя другого канала, а в каждый из каналов блока измерения и усреднения междупериодного сдвига фазы помехи введен блок памяти, включенный между выходом накопителя и первым входом первого перемножителя.

2. Устройство по п. 1, отличающееся тем, что накопитель содержит генератор импульсов и последовательно включенные блок памяти, сумматор и элемент И, второй вход которого соединен с тактовым входом блока памяти и выходом генератора импульсов, а выход сумматора соединен с информационным входом блока памяти, при этом входом и выходом накопителя соответственно являются второй вход сумматора и выход элемента И.

3. Устройство по п. 1, отличающееся тем, что блок усреднения содержит N последовательно включенных блоков задержки, выходы которых и вход первого из которых соединены с соответствующими входами сумматора, при этом входом и выходом блока усреднения соответственно являются вход первого из N блоков задержки и выход сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1977 |

|

SU711849A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1998-11-27—Публикация

1977-12-05—Подача