(54) ПРОЦЕССОР ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ ч МАШИНЫ С КАНАЛАМИ ПЕРЕДАЧИ ДАННЫХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с дискретными каналами связи | 1980 |

|

SU907538A1 |

| Устройство управления вводомвыводом информации | 1975 |

|

SU714385A1 |

| Устройство для сопряжения ЭВМ с телеграфными аппаратами | 1984 |

|

SU1251092A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Ассоциативное оперативное запоминающее устройство | 1981 |

|

SU978197A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU771719A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU773729A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1985 |

|

SU1322300A1 |

Изобретение относится к вычислительной технике и предназначено для ввода в ЦВМ информации,гтоинимаемой по каналам передачи данных.

Известно специализированное устройство, выполняющее Лункции приема, анализа и выдачи в универсальную ЦВМ информации, прийимаемой в виде две-ичных кодов по каналам передачи дай- Ю ных. Это устройство, разработанное для сопряжения 1ДВМ Минск-32 с каналами передачи данных, позволяет вести обмен информацией с 32абонентами ПО телеграфным ителефоннь1М ли- 15 ниям связи. Оно содержит 32 линейных блока, предназначенных для побитной , регистрации информации и побитной выдачи ее в каналы, а также гоупповое оборудование, включающее блоки 20 управления, сканирование линий, групповое ,ооорудование Формирования и анализа знаков, оперативную память накопления знакови блок выдачи данных в ЦВМ 11.25

Однако устрЬйство Кинск-1560 .имеет громоздкое индивидуальное оборудование каналов, выполненное, с применением электромеханических реле, и низкую производительность, что 30

лпйЧПЛГгтСТиГ

св-язано с последовательным характером обслуживания каналов передачи данных.

Наиболее близким по технической сущности к предлагаемому является мультиплексор , содержащий линейное оборудование 125 каналов и муль.типлексор, осуществляюишй сканирование линейных блоков, формирование знаков и их анализ с целью выделения служебных кодов, а также управление обмена с мультиплексным каналом ЦВМ. Хранение накапливаемых знаков и всей управляющей информации каналов осуществляется в блоке оперативной памяти, где за каждым входящим каналом закреплен буфер на 2 знака. Для выполнения всех функций, связанных с обслуживанием каналов, в схему введен специальный операционный блок, в котором осуществляется формирование / и анализ принимаемых знаков при последовательном опросе каналов 2,

Недостаток устройства заключается в низкой производительности и сложности оборудования, связанных с наличием в нем группового операционного устройства, обслуживающего каналы путем их сканирования.

Цель изобретения - сокращение обЬёма оборудования и повышение с-фодействия устройства.

Поставленная цель достигается тем, что в процессор для сопряжения цифровой вычислительной машинМ с каналами передачи данных, содержащий блок приема да:нннх, блок управления, блок выдачи данных, счетчик разрядов дешифратор, шифратор, регистр, группу, элементов ИЛИ, первую группу коммтаторов, ВТорзпо группу коммутаторов, причем входы блока приема данных явлются входами устройства, входы блОка выдачи данных соединены с первой групой выходов коммутаторов первой , первая группа выходов блока выдачи данных подключена к первой группе входов коммутаторов второй группы, вторая группа выходов блока выдачи данных соединена со входами

шифратора, выходы которого являются первой группой выходов процессора, а управляющий вход блока выдачи данных подключен к первому выходу блока управления, второй выход которого подключен ко входу счетчика, выходы которого соединены со входами дешифратора, выходы которого подключены к первым входам элементов ИЛИ группы, вторые входы которых подключены к третьему выходу блока управления, выходы регистра являются второй группо выходов процессора, введены первый и второй блоки ассоциативнойПамяти, четыре группы элементов И, группа триггеров совпадения, группа триггеров коммутации, третья группа коммутаторов, при этом пезрвая групйа выходов блока приема данных соединена с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к вы- ходам первого блока ассоциативной памяти, первая группа входов которозго соединена с выходагди счетчика, вторая группа выходов блока приема данных подключена к первым входам соответствующих элементов И второй группы, выходы которых объединены с соответствующими выходами третьей группы выходов блока приема данных и подключены к первым входам коммутаторов третьей группы, выходы которых со- . единены с первой группой входов вторго блока ассоциативной памяти, rtepвая группа выходов которого подключена к первым входам соответствующих кo мyтaтopoв первой группы, вторые входы которых объединены/с вторыми входами соответствующих коммутаторов второй, и третьей групп и подключены к выходам соответствующих триггеров коквиутации группы, входы которых соединены с выходами элементов И третьей группы, первые входы которых соединены с выходами дешифратора, вторые входы элементов И соединены с четвертым выходом блока уп744541

равления, а третьи выходы элементов И третьей группы объединены с первыми входами элементов И четвертой группы, вторыми входами элементов И второй группы и подключены к выходам соответствующих триггеров совпадения группы, первые входы которых соединены с выходами элементов И первой группы, а вторые входы триггеров совпадения группы подключены .к пятому выходу блока управления, шестой выход которого соединен со вторыми входами элементов И четвертой группы, выходы которых подключены ко второй группе входов первого блока ассоциативной памяти, группа входов регистра соединена со второй группой выходов второго блока ассоциативной памяти, вторая группа входов которого соединена с выходами элементов ИЛИ группы, а третья группа входов второго ;блока ассоциативнойпамяти подключена к Выходам коги1мутаторов второй группы.

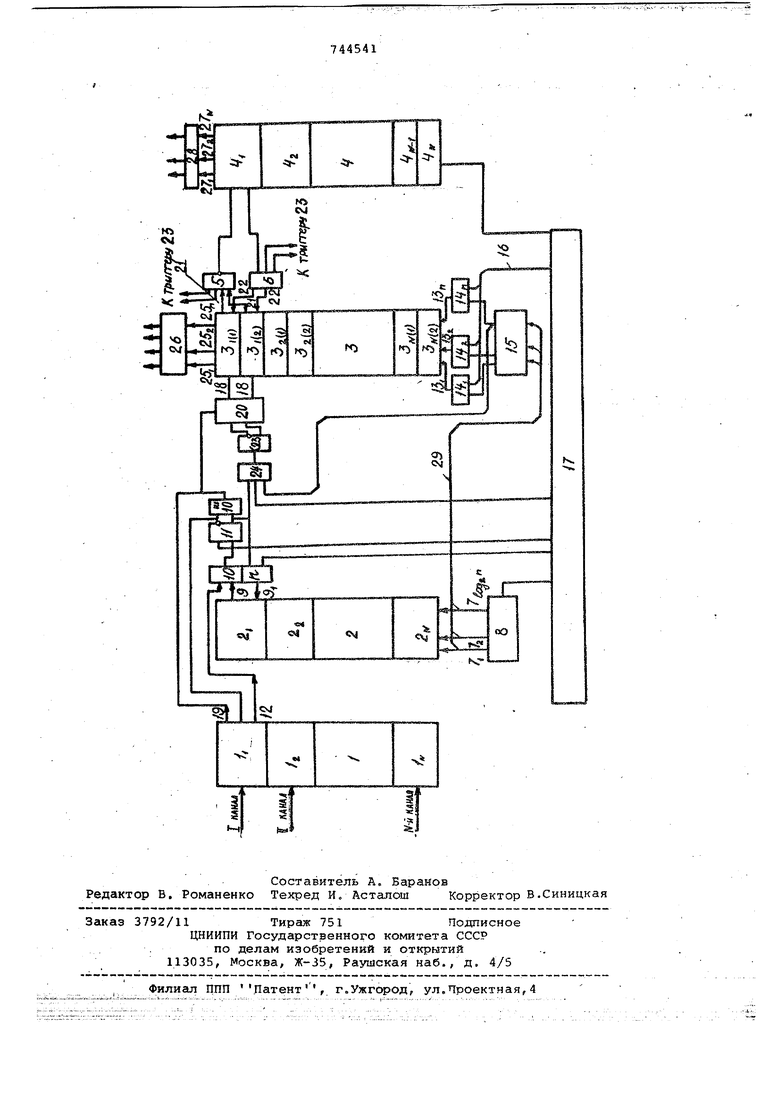

На чертеже изображена структурная схема процессора.,:

Устройство содержит Влок 1 поразрядного приема данных (БПП) от N ка(по

налов с ячейками 1

N

1

-2

ОДНОЙ ячейке на каждый канал); первый блок 2 ассоциативной памяти (БСР) с ячейками 2j, 22, .. , 2, по разрядов в каждой; второй блок 3 ассоциативной памяти(БНА) с ячейками

(по

3ia

г((П

N(2)

1(21

две п-разрядных ячейки на канал) и блок 4 выдачи данных (BOB) с ячейками 4 , 42, 4fj.

,Каждая ячейка BOB 4 соединена с коммутатором 5 первой группы и коммутатором 6 второй группы (на чертеже дано изображение для одного канала) . Первый блок 2 ассоциативной . памяти шинами 7 , 1, ..., gotfj. опроса-записи подключен к выходам счетчика 8 разрядов, а шина 9 совпадения каждой ячейки подсоединена через элемент 10 И первой группы к установочному входу триггера 11 индикатора совпадения группы. Ча второй вход элемента 10 И подключен выход 12 синхронизации соответствующего канала БПП.

Второй блок 3 ассоциативной памяти шинами, 13, 132 Зп опросазаписи через элементы 14, 142 ...14 ИЛИ группы подключен к выходам деишфратора 15 номера разрядов. Вторые вхды элементов 14.} .. , 14 ИЛИ объединены шиной 16 анализа знаков, подключенной к блоку 17 управления.

Шины 18 разрешения записи каждой пары ячеек БНА 3 подключены к соответствующим информационным выходам 19 БПП через коммутаторы 20 третьей группы. Шины 21 совпадения каждой пары ячеек подключены к коммутатору 5 первой группы, а шины 22 разрешения чтения - к коммутатору б второй группы. .

Счетные вхолы триггеров 23 коммутации ячеек БНА через 24 И третьей группы подключены к выходу дешифратора 15 номера разрядов.

Кроме того, блок БНА 3 шинами 25 252 25f) соединен с выходным регистром 26, а блок БОВ 4 - шинами 27j, 272 м шифратором 28 номера читаемого знака.

Входы дешифратора 15 номера разрядов шиной 29 соединены с выходами счетчика 8 разрядов первого блока 2 ассоциативной памяти.

Устройство работает следующим образом.

Блок 1 поразрядного приема данных фиксирует сигналы поразрядной синхро низации и информационных сигналов принимаемых разрядов по каждому каналу и хранит эти сигналы до их опроса в течение времени -| В - скорость модуляции в канале.

На ассоциативную память (АП) возлагаются подсчет разрядов принимаемых знаков по каждому каналу, формирование знаков из принимаемых разрядов и их хранение до выдачи в ЦВМ, анализ принятых знаков с целью выделния служебных кодов и охфильтровывания тех знаков, которые не передаются в ЦВМ (например, комбинации покоя или синхрокомбинации).

. Первый блок 2 ассоциативной памяти осуществляет подсчет разрядов принимаемых знаков, для чего шины опроса-записи этого блока подключены к счетчику 8 разрядов, работающему по модулю с тактовой частотой рг Вп,

Юина 9 совпадения каждой ячейки 2j, 22 2 подключены к триггеру 11 совпадения через элемент Ю и, на ее второй вход подается синхросигнал сопровождающий каждый брт принимаемо информации.

Единичное состояние триггера 11 разрешает запись (по шине разрешения записи) очередного состояния счетчика 8 разрядов в соответствующую ячейку 2j, 2 ... 2„ блока 2, чем и достигается решение первой задачи параллельно по всем каналам устройства за время одного цикла счетчика (Т«,ег i ) .

Накопление знаков и их анализ реализуются вторым .блоком 3 ассоциативной памяти, в котором за каждым из N каналов закрепляется по две

ячейки разрядности п

В одной из

этих ячеек знак формируется, а во второй хранится., до выдачи в ЦВМ.

Запись принимаемых битов в некоторый разряд второго блока 3 ассоциатив ной памяти разрешается в том случае, если триггер 11 индикатора совпадения И, первого блока 2 ассоциативной памяти при опросе ячейки счетчика разрядов этого блока установлен в-, единицу. Запись всех одноименных

разрядов по всем каналам производится одновременно..

Коммутация каждой пары ячеек одного канала второго блока 3 ассоциативной памяти осуществляется с помоШью триггера 23, переключаемого по счетному входу сигналом с п-го выхода дешифратора 15 номера разрядов, если очередной знак по данному каналу полностью принят.

Третья задача-анализ принятых знаков выполняется путем опроса этих знаков кодомслужебных комбинаций, подаваемым на пшны 13, 13 ... 13 опроса-записи через элементы 14, 142 14,ИЛй, на вторые входы которых подключены выходы деигифратор,а 15 номера разрядов.

При совпадении кодой, принятых в ячейки памяти с кодом опроса, на выходах этих ячеек возникают сигналы совпадения, которые инвертируются и поступают на входы БОВ 4 через KOfteiv|таторы 5, управляемые триггерами 23. 4 сигналы готовности знака фиксируются и знаки ставятся в очередь на выдачу в ЦВМ.

БОВ 4 содержит триггеры запоминания сигналов готовности знаков и логические элементы очередности их выдачи в ЦВМ, удойлетворяюиие запросы на выдачу знаков, в соответствии с номерами кана:лов.

Шифратор 28 номера читаетюго знака подключен к выходам БОВ 4 для формирования номера знака, поступившего в данный момент в выходной регистр 2 для выдачи в ЦВМ.

Блок 17 управления формирует сигналы управления всеми блоками процессора.

Таким образом, работа процессора осуществляется в следующей последовательности: опрос БСР кодом номера раряда (счетчик 8); запись очередного разряда знака в БНА, запись состояния счетчика 8 разрядов в БС ;-переключение триггеров 23, опрос БНА служебным кодом, добавление единицы в счетчик 8; чтение очередного знака из БНА; гашение триггера 11 индикатора сойпадёнйя.

Указанный цикл повторяется регулярно с периодом Т -|г 6 g , при этом осуществляется прием и анаЛиз знаков по всем обслуживаемым каналам одновременно и последовательная выдача их параллельным крдом в ЦВМ,

Предлагаемое устройство выигрывае в производительности и объеме оборудования. Отдельное операционное устройство в процессоре отсутствует. Управление предлагаемым устройством проще, чем связано с регулярностью и малым числом сигналов цикла управления. Производительность процессора характеризуется предельной скоростью передачи по каналам и

числом обматйгсимально допустикым

ёйу й%аейдх каНалЬй.

Формула изобретения - -- Процессор для сопряжения цифровой вычислительной мшиины с каналами передачи данных, содержащий блок приема данных, блок управления, блок звыда 1й данных, счетчик азрядов, дешифратор, шифратор регистр, группу элёментов ИЛИ, liepfeyw группу) ком,S fa opOB; вторую группу коммутаторов, причем входы блока приёма Sa Hlieix являготся входами устройства, входы блоКа вшачи данных соединены с первой группой выходов коммутаторов первой группы, первая группа выходов блОКа Данных подключена к первой груп«ё йходов ксммутаторов второй груп Ш, вторая группа выходов блока выЙачи данных соединены со входами шиф psfdipa, выходы которого являются первой группой вй1сод;ов процессора, а управляющий вход блока выдачи данных 1Убдключен к первому выходу блока управления, второй выход которого подйЛючён ко входу счетчика, выходы

соединены со входами дешифl aT вйхбда1 бт 6г о п 6НЮ1к)«с енж к первым входам элементов ИЛИ группы, вторые входы которых подключены к третьему выходу блока управления, выходы регистра являются второй груп поЙ ваз 6дЬй Процессора, о т л и ч а ю щ и и с я тбм, что, с целью сокращения объема оборудования и повышения быстродействия, в него введены первый и второй блоки асеоциатив ной пайяти, четыре группы.элементов И, группа триггеров совпадения, труп 1та 5йггёрйв коммутации, третья гр,упИа комкута торов, при этом первая группа выходов блойа приема данных соединена с первыми входами соответствую аих элементов И первой группы, втбJ SiS входы которых подключены к выходам первого блока ассоциативной памяти, первая группа входов которого

йОёдШнёна с выходами счетчика, вторая группа выходов блока приема дан- ных подключена к первым входам соответс11ующих элементов и второй группа, выходы которых объединены с соответствующими выходами третьей группы выходов блока приема данных и подключены к первым входам коммутаторов третьей группы, выходы которых соединены с первой группой входов второго блока ассоциативной памяти, первая труппа выходов которого подключена к первым входам соответствующих.коммутаторов первой группы, вторые входы которых объединены с вторыми входами соответствующих коммутаторов второй и третьей групп и подключены к выходам соответствующих, триггеров коммутаций группы, входы которых соединены с выходами элементов И третьей группы, первые входы которых соединены с выходами дешифратора, вторые входы элементов И соединены с четвертым выходом блока управле1 ия, а третьи выходы элементов И третьей группы объединены с первыми входами элементов Ичетвертой группы, втбрыми входами элементов И второй группы и подключены к выходам соответствую-ших трипперов совпадения группы, первйе ВХОДИ которых соединены с выходами элементов и первой группы, а вторые входил триггеров совпадения группы подключены к пятому выходу блока управления, шестой которогосоединен со вторыми входами элементов И четвертой группы,выходы которых подключены ко второй группе входов первого блока ассоциативной памяти, группа входов регистра соединена со второй группой выходов ВТОрбгб блока ассоциативной памяти, вторая Труппа вз4 5цой которого соединена с выходами элементов ИЛИ группы, а третья группа входов второго блока ассоциативной памяти подключена к выхода коммутаторов второй группы.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-06-30—Публикация

1978-02-13—Подача