Сканирование по знакам (вместо побитного сканирования в известных устройствах) позволяет существенно повысить пропускную способность устройства, а следовательно, и скорост ввода данных из каналов связи 2.

Недостаток данного устройства со стоит в сложности и большом объеме оборудования.Кроме этого,устройство не позволяет организовать вывод данных из ЦВМ в каналы связи,для чего также может потребоваться устройство значительной сложности.

Цель изобретения --сокращение объема оборудования и совмещение функций приема и передачи в одном устройстве.

Поставленная цель достигается тем что в устройствоf содержащее линейный блок, группа входов-выходов которого является группой линейных входов-выходов устройства, коммутатор, регистр коммутации, блок управления коммутацией, блок синхронизации , бло памяти, первые вход и выход которого являются соответственно информационными входом и выходом устройства, и блок очередности выдачи знаков, выход которого является управляющим выходом устройства-, введены буферный регистр, регистр информации и регист маркеров, причем информационный выход линейного блока подключен к первому информационному входу буферного регистра, выходом соединенного с nepBHiM входом блока управления коммутацией и информационным входом коммутатора, а вторым информационным входом - с информационными входами регистра маркеров и линейного блока к выходом регистра информации, информационный вход которого подключен ко второму выходу блока памяти, а управляющий вход - к выходу регистра коммутации, входу блока очередности выдачи знаков и управляющему входу коммутатора, выходом соединенного с вторым входом блока памяти, выход синхронизации линейного блока соединен с входом блока синхронизации и вторым входом блока управления коммутацией, группа выходов блока синхронизации соединена с синхронизирующими входами буферного регистра, линейного блока, регистра маркеров и регистра коммутации, информационный вход которого подключен к выходу блока управления коммутацией, третьим входом соединенному с выходом регистра- маркеров, а четвертым входом - Свыходом управления направлением обмена устройства и управляющим входом линейного блока, а также тем, что блок управления коммутацией содержит элементы И, выходы которых являются выходом блока, и элементы ИЛИ, причем первый и второй входы i-ro элемента И {i-l,N) подключены соответственно к 1-ым разрядным

шинам первого и второго входов блока, а третий вход - к выходу элемента ИЛИ, первый и второй входы которого соединены соответственно с i-ыми разрядными шинами третьего и g четвертого входов блока.

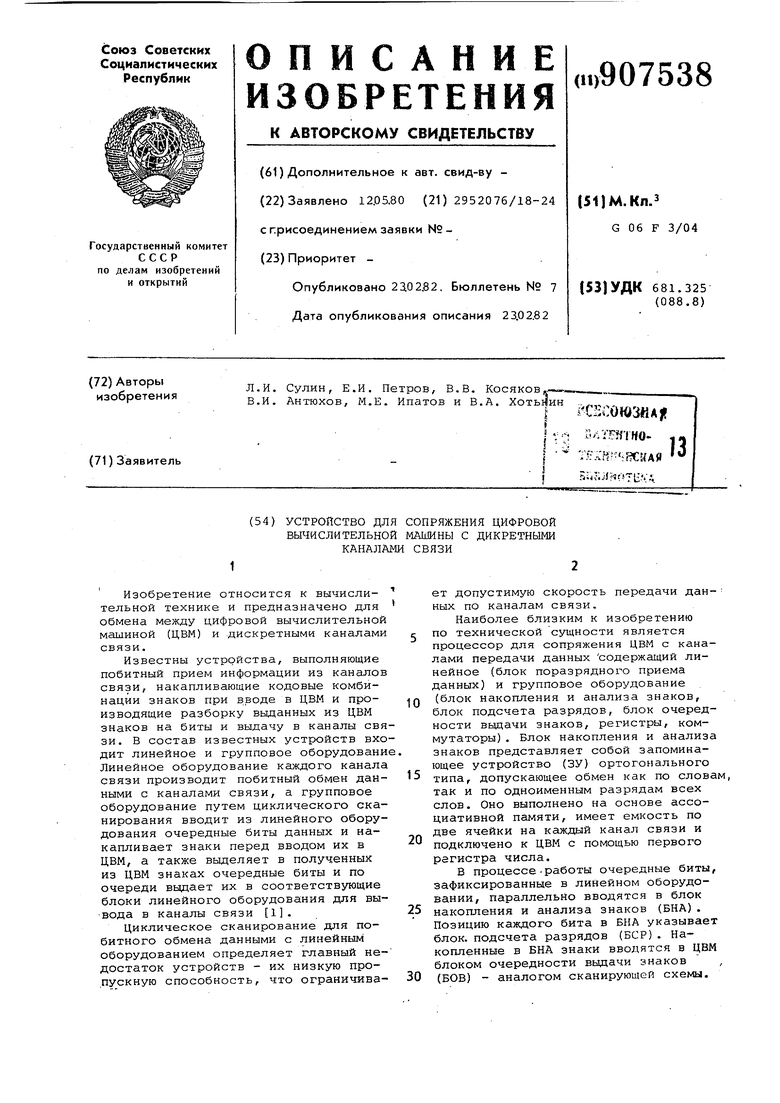

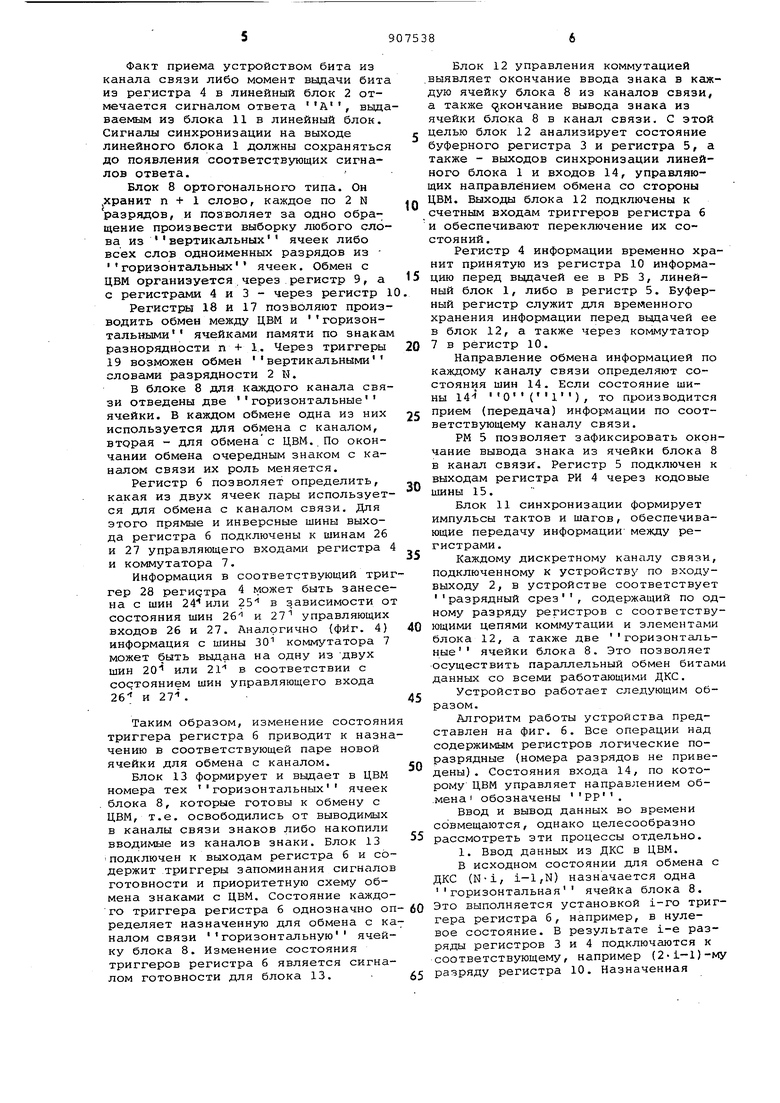

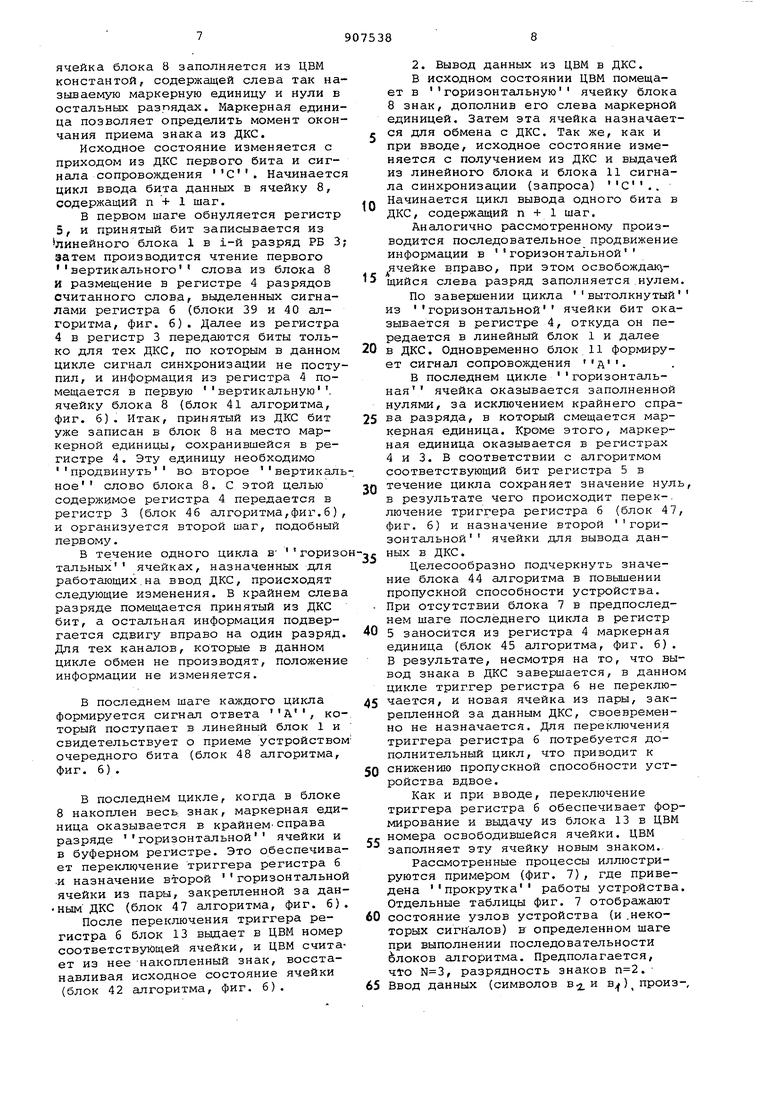

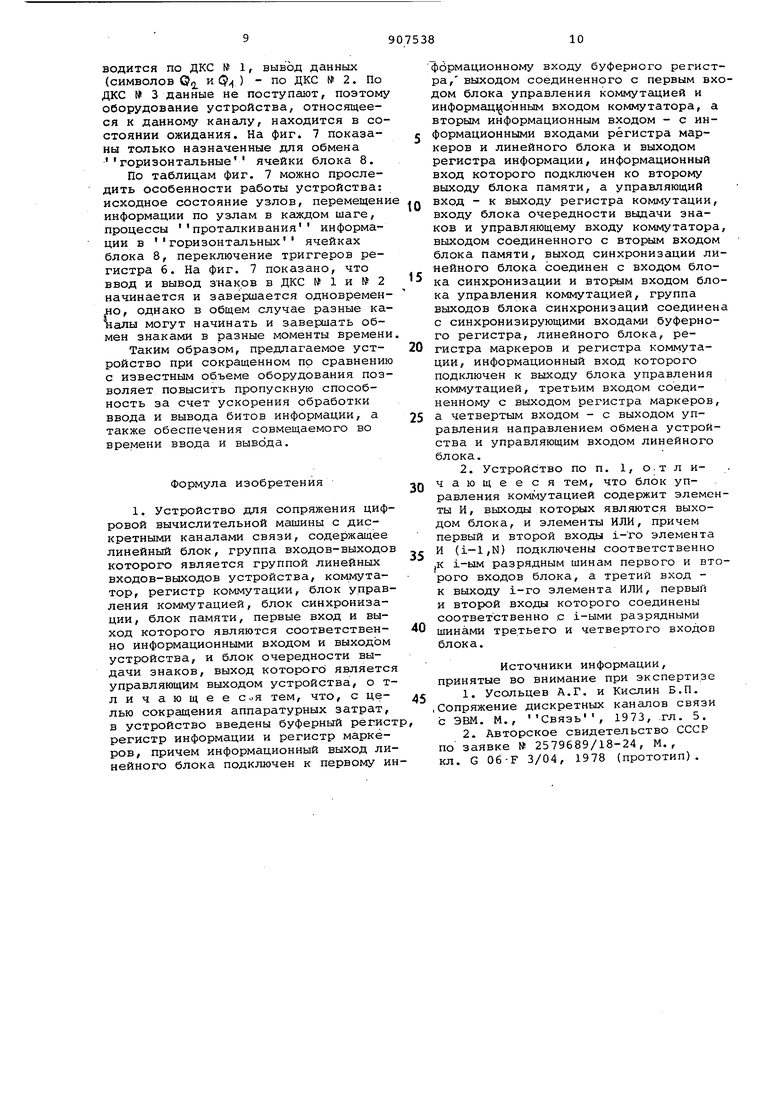

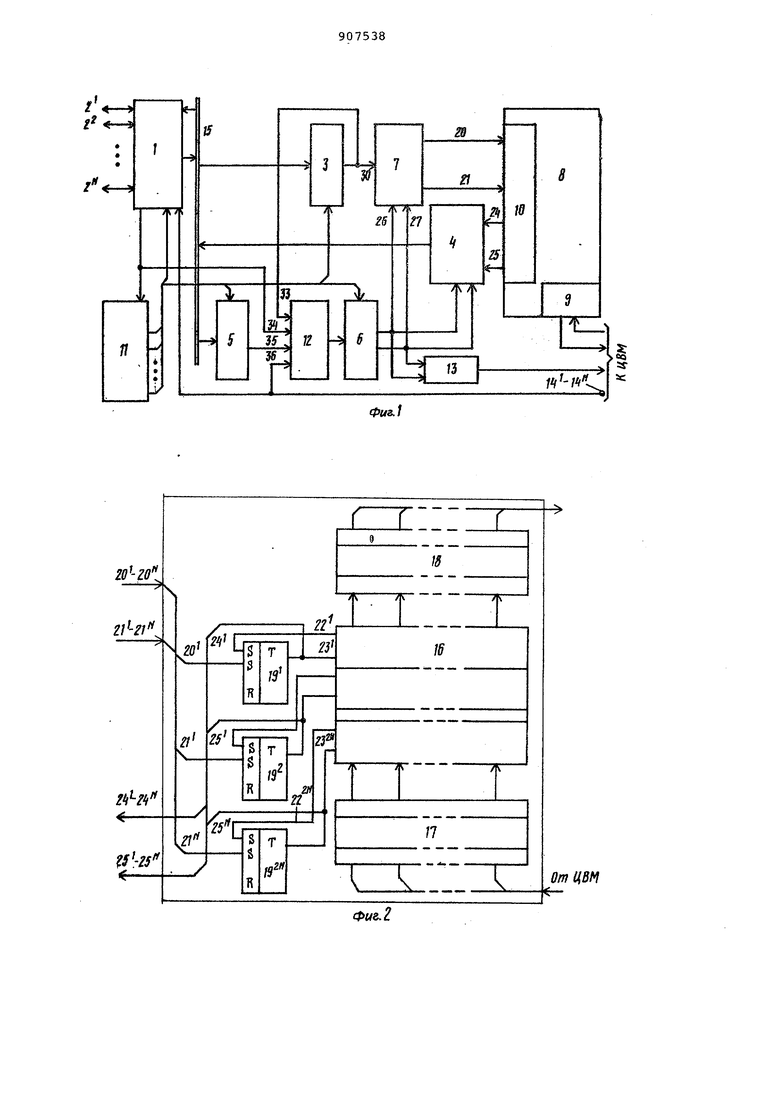

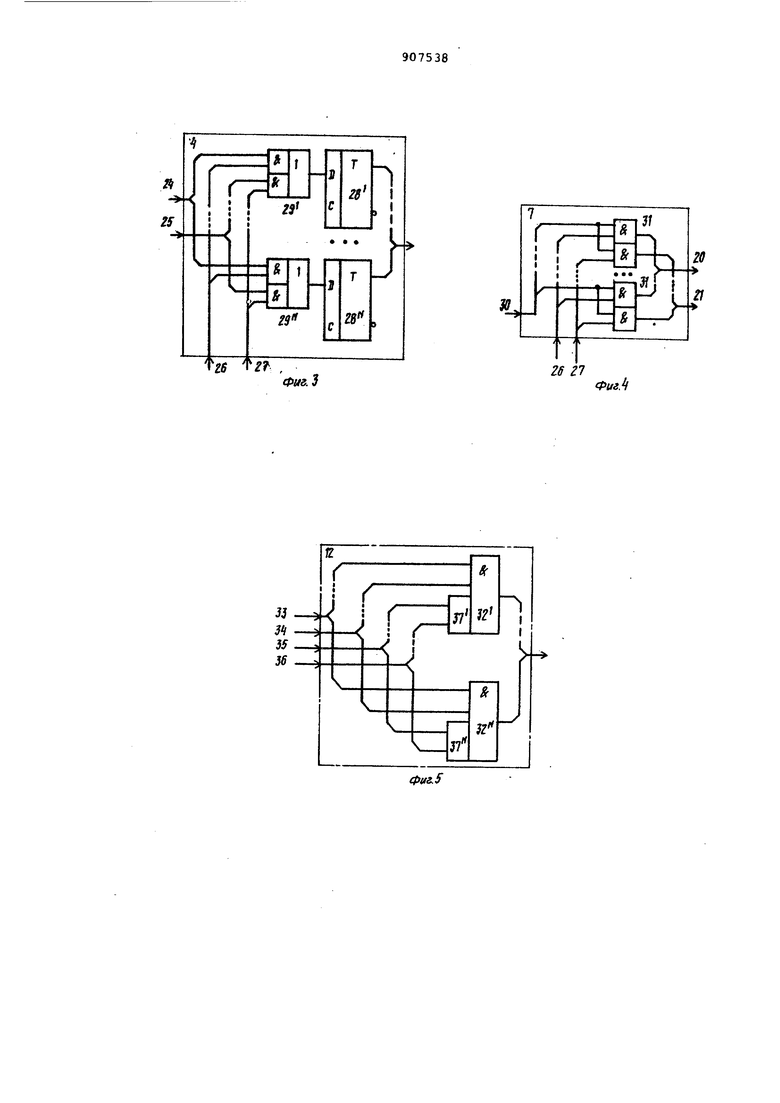

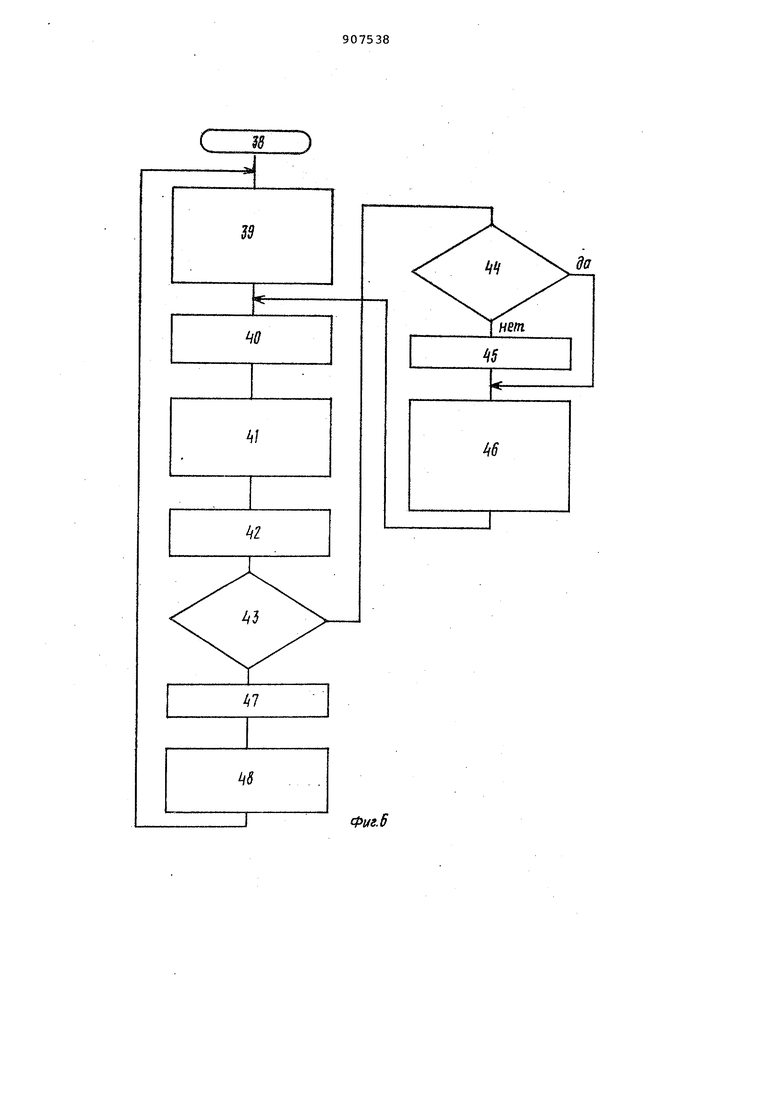

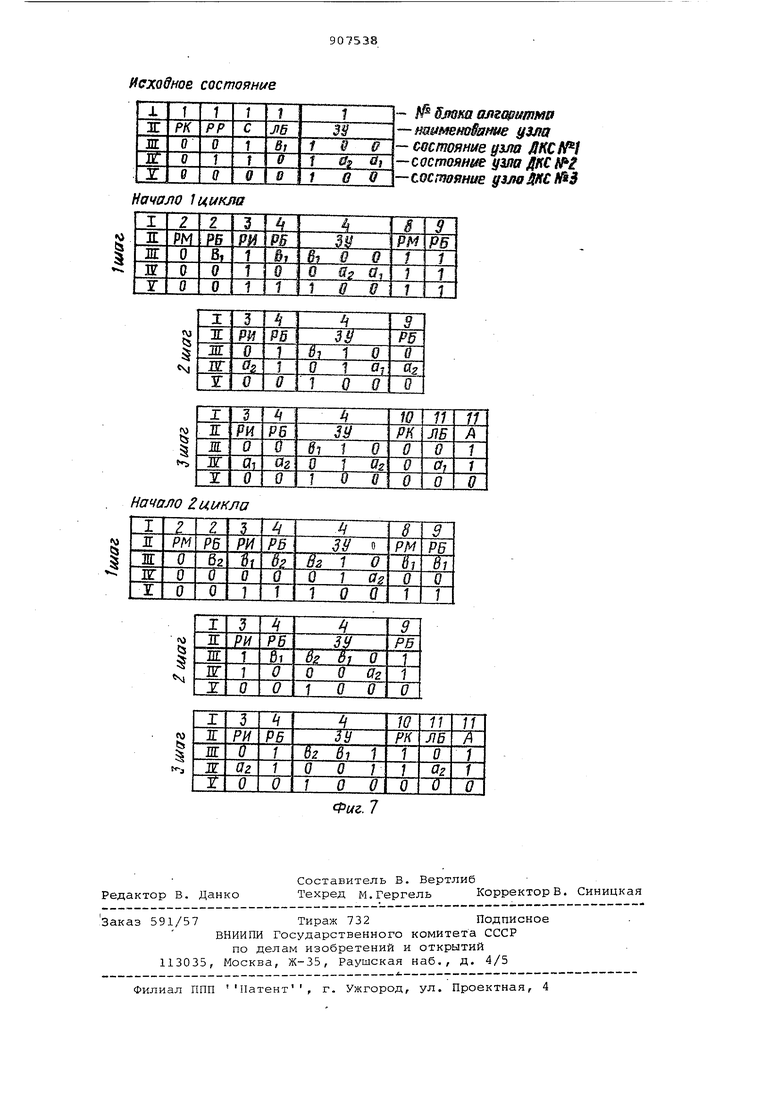

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - пример реализации блока памяти на базе ассоциативjHoro запоминающего устройства; на,,

.0 фиг. 3 - функциональная схема регистра информации; на фиг.4 - функциональная схема коммутатора; на фиг. 5 функциональная, схема блока управления коммутацией; на фиг. б - блок-схема алгоритма функционирования; на 5, фиг. 7 - таблицы состояний устройства.

Устройство содержит (фиг. 1) линейный блок 1, линейные входы-выходы 2 группы устройства N-разрядный буферный регистр (РБ) 3, регистр 4

0 информации (РИ), регистр 5 маркеров (РМ), регистр 6 коммутации (РК), коммутатор 7, блок 8 памяти (ЗУ) с ре. гистрами 9 и 10 числа (РЧ и Р%), блок 11 синхронизации, блок 12 управления (БУК) коммутацией, блок 13 очерёдности выдачи знаков, вход 14 управления направлением обмена устройства, кодовые шины 15 выхода регистра 4 ,

« Блок 8 памяти построен на базе ассоциативного запоминающего устройства ортогонального типа и включает (рис. 2) массив из 2 N ячеек 16 памяти разрядностью (п+1) бит каждая, первый регистр числа, состоящий из

регистра 17 записи-опроса и выходного регистра 18,2 N триггеров 19 индикаторов совпадения, образующих второй регистр числа, шины 20 и 21 второго входа блока, шины 22 совпадения, шины 23 разрешения записи и шины 24 и 25 выхода блока.

РИ 4 содержит (фиг. 3) шины 26 и 27 управляющего входа, триггеры 28 и элементы И-ИЛИ 29, коммутатор

5 (фиг. 4) информационных входов 30 и элементы И 31. БУК 12 (фиг. 5) включает элементы И 32, входы 33-36 блока и элементы ИЛИ 37. Устройство включает также блоки 38-48 алгоритQ ма (фиг. 6).

Линейный блок 1 обеспечивает побитный .обмен данными с дискретными каналами связи (ДКС), временное хранение очередных бит и ввод из в РБ 3

через кодовую шину 15, при этом сигналы сопровождения из линейного блока 1 поступают в блоки 11 и 12. При выводе данных в каналы связи линейный блок 1 выдает в блок 11 (ив

0 блок 12) запросы на очередные биты

и принимает информацию из регистра 4.

В дальнейшем сигналы сопровождения и запросов названы в описании :игналами синхронизации и обозначаются С. Факт приема устройством бита из канала связи либо момент выдачи бита из регистра 4 в линейный блок 2 отмечается сигналом ответа А, выда ваемым из блока 11 в линейный блок. Сигналы синхронизации на выходе линейного блока 1 должны сохраняться до появления соответствующих сигналов ответа. Блок 8 ортогонального типа. Он .хранит п + 1 слово, каждое по 2 N разрядов, и позволяет за одно обращение произвести выборку любого слова из вертикальных ячеек либо всех слов одноименных разрядов из горизонтальных ячеек. Обмен с ЦВМ организуется,через регистр 9, а с регистрами 4 и 3 - через регистр Регистры 18 и 17 позволяют производить обмен между ЦВМ и горизонтальными ячейками памяти по знакам разнорядности п + 1. Через триггеры 19 возможен обмен вертикальными словами разрядности 2 W. В блоке 8 для каждого канала свя зи отведены две горизонтальные ячейки. В каждом обмене одна из них используется для обмена с каналом, вторая - для обмена с ЦВМ. По окончании обмена очередным знаком с каналом связи их роль меняется. Регистр 6 позволяет определить, какая из двух ячеек пары использует ся для обмена с каналом связи. Для этого прямые и инверсные шины выхода регистра б подключены к шинам 26 и 27 управляющего входами регистра и коммутатора 7. Информация в соответствующий три гер 28 регистра 4 может быть занесе на с шин 24 или 25 в зависимости о состояния шин 26 и 27 управляющих входов 26 и 27. Аналогично (фиг. 4) информация с шины 30 коммутатора 7 может быть выдана на одну из двух шин 20 или 21 в соответствии с содтоянием шин управляющего входа 26 и 27 . Таким образом, изменение состояни триггера регистра 6 приводит к назна чению в соответствующей паре новой ячейки для обмена с каналом. Блок 13 формирует и выдает в ЦВМ номера тех горизонтальных ячеек блока 8, которые готовы к обмену с ЦВМ, т.е. освободились от выводимых в каналы связи знаков либо накопили вводимые из каналов знаки. Влок 13 подключен к выходам регистра 6 и со держит триггеры запоминания сигналов готовности и приоритетную схему обмена знаками с ЦВМ. Состояние каждого триггера регистра 6 однозначно оп ределяет назначенную для обмена с ка налом связи горизонтальную ячейку блока 8. Изменение состояния триггеров регистра 6 является сигналом готовности для блока 13. Влок 12 управления коммутацией выявляет окончание ввода знака в каждую ячейку блока 8 из каналов связи, а также (.кончание вывода знака из ячейки блока 8 в канал связи. С этой целью блок 12 анализирует состояние буферного регистра 3 и регистра 5, а также - выходов синхронизации линейного блока 1 и входов 14, управляющих направлением обмена со стороны ЦВМ. Выходы блока 12 подключены к счетньзм входам триггеров регистра 6 и обеспечивают переключение их состояний. Регистр 4 информации временно хранит принятую из регистра 10 информацию перед выдачей ее в РБ 3, линейный блок 1, либо в регистр 5. Буферный регистр служит для временного хранения информации перед выдачей ее в блок 12, а также через коммутатор 7 в регистр 10. Направление обмена информацией по каждому каналу связи определяют состояния шин 14. Если состояние шины 14i О ( 1 ) / то производится прием (передача) информации по соответствующему каналу связи. РМ 5 позволяет зафиксировать окончание вывода знака из ячейки блока 8 в канал связи. Регистр 5 подключен к выходам регистра РИ 4 через кодовые шины 15. Блок 11 синхронизации формирует импульсы тактов и шагов, обеспечивающие передачу информации между регистрами. Каждому дискретному каналу связи, подключенному к устройству по входувыходу 2, в устройстве соответствует разрядный срез , содержащий по одному разряду регистров с соответствующими цепями коммутации и злементами блока 12, а также две горизонтальные ячейки блока 8. Это позволяет осуществить параллельный обмен битами данных со всеми работающими ДКС. Устройство работает следующим образом. Алгоритм работы устройства представлен на фиг. 6. Все операции над содержимым регистров логические поразрядные (номера разрядов не приведены) . Состояния входа 14, по которому ЦВМ управляет направлением об.менаI обозначены РР. Ввод и вывод данных во времени совмещаются, однако целесообразно рассмотреть эти процессы отдельно. 1. Ввод данных из ДКС в ЦВМ. В исходном состоянии для обмена с ДКС (N-i, i-l,N) назначается одна горизонтальная ячейка блока 8. Это выполняется установкой i-ro триггера регистра 6, например, в нулевое состояние. В результате i-e разряды регистров 3 и 4 подключаются к соответствующему, например (2i-1)-му разряду регистра 10. Назначенная ячейка блока 8 заполняется из ЦВМ константой, содержащей слева так на зываемую маркерную единицу и нули в остальных разрядах. Маркерная едини ца позволяет определить момент окон чания приема знака из ДКС. Исходное состояние изменяется с приходом из ДКС первого бита и сигнала сопровождения С. Начинаетс цикл ввода бита данных в ячейку 8, содержащий п + 1 шаг. В первом шаге обнуляется регистр 5, и принятый бит записывается из линейного блока 1 в i-й разряд РВ 3 затем производится чтение первого вертикального слова из блока 8 И размещение в регистре 4 разрядов считанного слова, выделенных сигналами регистра б (блоки 39 и 40 алгоритма, фиг. 6). Далее из регистра 4 в регистр 3 передаются биты только для тех ДКС, по которым в данном цикле сигнал синхронизации не посту пил, и информация из регистра 4 помещается в первую вертикальную, ячейку блока 8 {блок 41 алгоритма, фиг. б). Итак, принятый из ДКС бит уже записан в блок 8 на место маркерной единицы, сохранившейся в регистре 4. Эту единицу необходимо продвинуть во второе вертикаль ное слово блока 8. С этой целью содержимое регистра 4 передается в регистр 3 (блок 46 алгоритма,фиг.б) и организуется второй шаг, подобный первому. В течение одного цикла в горизо тальных ячейках, назначенных для работающих.на ввод ДКС, происходят следующие изменения. В крайнем слева разряде помещается принятый из ДКС бит, а остальная информация подвергается сдвигу вправо на один разряд Для тех каналов, которые в данном цикле обмен не производят, положение информации не изменяется. В последнем шаге каждого цикла формируется сигнал ответа А, который поступает в линейный блок 1 и свидетельствует о приеме устройством очередного бита (блок 48 алгоритма, фиг. б). В последнем цикле, когда в блоке 8 накоплен весь, знак, маркерная единица оказывается в крайнем справа разряде горизонтальной ячейки и в буферном регистре. Это обеспечивает переключение триггера регистра б и назначение второй горизонтальной ячейки из пары, закрепленной за дан нымДКС (блок 47 алгоритма, фиг. 6) После переключения триггера регистра б блок 13 выдает в ЦВМ номер соответствующей ячейки, и ЦВМ считает из нее накопленный знак, восстанавливая исходное состояние ячейки (блок 42 алгоритма, фиг. б). 2. Вывод данных из ЦВМ в ДКС. В исходном состоянии ЦВМ помещает в горизонтальную ячейку блока 8 знак, дополнив его слева маркерной единицей. Затем эта ячейка назначается для обмена с ДКС. Так же, как и при вводе, исходное состояние изменяется с получением из ДКС и выдачей из линейного блока и блока 11 сигнала синхронизации (запроса) С . . Начинается цикл вывода одного бита в ДКС, содержащий п + 1 шаг. Аналогично рассмотренному производится последовательное продвижение информации в горизонтальной ячейке вправо, при этом освобождак щийся слева разряд заполняется нулем. По завершении цикла вытолкнутый из горизонтальной ячейки бит оказывается в регистре 4, откуда он передается в линейный блок 1 и далее в ДКС. Одновременно блок 11 формирует сигнал сопровождения А В последнем цикле горизонтальная ячейка оказывается заполненной нулями, за исключением крайнего справа разряда, в который смещается маркерная единица. Кроме этого, маркерная единица оказывается в регистрах 4и 3. В соответствии с алгоритмом соответствующий бит регистра 5 в течение цикла сохраняет значение нуль, в результате чего происходит перек-. лючение триггера регистра б (блок 47, фит. б) и назначение второй горизонтальной ячейки для вывода данных в ДКС. Целесообразно подчеркнуть значение блока 44 алгоритма в повышении пропускной способности устройства. При отсутствии блока 7 в предпоследнем шаге последнего цикла в регистр 5заносится из регистра 4 маркерная единица (блок 45 алгоритма, фиг. б). В результате, несмотря на то, что вывод знака в ДКС завершается, в данном цикле триггер регистра б не переключается, и новая ячейка из пары, закрепленной за данным ДКС, своевременно не назначается. Для переключения триггера регистра б потребуется дополнительный цикл, что приводит к снижению пропускной способности устройства вдвое. Как и при вводе, переключение триггера регистра б обеспечивает формирование и выдачу из блока 13 в ЦВМ номера освободившейся ячейки. ЦВМ заполняет эту ячейку новым знаком.. Рассмотренные процессы иллюстрируются примером (фиг. 7), где приведена прокрутка работы устройства. Отдельные таблицы фиг. 7 отображают состояние узлов устройства (и .некоторых сигналов) В определенном шаге при выполнении последовательности блоков алгоритма. Предполагается, что , разрядность знаков . Ввод данных (символов B-J. и в)произ-. водится по ДКС № 1, вывод данных (символов Qf и Q ) - по ДКС № 2. По ДКС № 3 данные не поступают, поэтому оборудование устройства, относящееся к данному каналу, находится в состоянии ожидания. На фиг. 7 показаны только назначенные для обмена горизонтальные ячейки блока 8. По таблицам фиг. 7 можно проследить особенности работы устройства: исходное состояние узлов, перемещени информации по узлам в каждом шаге, процессы проталкивания информации в горизонтальных ячейках блока 8, переключение триггеров регистра 6. На фиг. 7 показано, что ввод и вывод знакрв в ДКС № 1 и № 2 начинается и завершается одновременно, однако в общем случае разные каналы могут начинать и завершать обмен знаками в разные моменты времени Таким образомj предлагаемое устройство при сокращенном по сравнению с известным объеме оборудования позволяет повысить пропускную способность за счет ускорения обработки ввода и вывода битов информации, а также обеспечения совмещаемого во времени ввода и вывода. Формула изобретения 1. Устройство для сопряжения циф ровой вычислительной машины с дискретными каналами связи, содержащее линейный блок, группа входов-выходо которого является группой линейных входов-выходов устройства, коммутатор, регистр коммутации, блок управ ления коммутацией, блок синхронизации, блок памяти, первые вход и выход которого являются соответственно информационными входом и выходом устройства, и блок очередности выдачи знаков, выход которого являетс управляющим выходом устройства, о т личающеесоя тем, что, с целью сокращения аппаратурных затрат, в устройство введены буферный регис регистр информации и регистр маркеров, причем информационный выход ли нейного блока подключен к первому и формационному входу буферного регистра, выходом соединенного с первым входом блока управления коммутацией и информационным входом коммутатора, а вторым информационным входом - с информационными входами регистра маркеров и линейного блока и выходом регистра информации, информационный вход которого подключен ко второму выходу блока памяти, а управляющий вход - к выходу регистра коммутации, входу блока очередности выдачи знаков и управляющему входу коммутатора, выходом соединенного с вторым входом блока памяти, выход синхронизации линейного блока соединен с входом блока синхронизации и вторым входом блока управления коммутацией, группа выходов блока синхронизации соединена с синхронизирующими входами буферного регистра, линейного блока, регистра маркеров и регистра коммутации, информационный вход которого подключен к выходу блока управления коммутацией, третьим входом соединенному с выходом регистра маркеров, а четвертым входом - с выходом управления направлением обмена устройства и управляющим входом линейного блока. 2. Устройство по п. 1, о.т л ичающееся тем, что блок управления коммутацией содержит элементы И, выходы которых являются выходом блока, и элементы ИЛИ, причем первый и второй входеа i-ro элемента И (i-l,N) подключены соответственно jK i-ым разрядным шинам первого и второго входов блока, а третий вход к выходу i-ro элемента ИЛИ, первый и второй входы которого соединены соответственно с i-ыми разрядными шинами третьего и четвертого входов блока. Источники информации, принятые во внимание при экспертизе 1.Усольцев А.Г. и Кислин Б.П. Сопряжение дискретных каналов связи с ЭВМ. М., Связь, 1973, гл. 5. 2.Авторское свидетельство СССР по заявке № 2579689/18-24, М. , кл. G 06-F 3/04, 1978 (прототип).

/ l

31

fl

&

.

r

i

20

I

, f I P

ii

t

21

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для сопряжения цвм с каналами передачи данных | 1978 |

|

SU744541A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство для обмена информацией | 1982 |

|

SU1091151A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

Фиг.З

/7

Ф.

до

Фиг. 6

Исходное состоян1 е

Начало li4(KMt

лз t5

«м

Начало вникла

to

N

1 §мт апгщ1атм0 yiaa состояние дзла jSKCf l состояние узла КС состояние дзлаМка З

Авторы

Даты

1982-02-23—Публикация

1980-05-12—Подача