Изобретение относится к вычислительной технике и может быть использовано в системах обмена информацией

Целью изобретения является сокращение оборудования и повышение производительности.

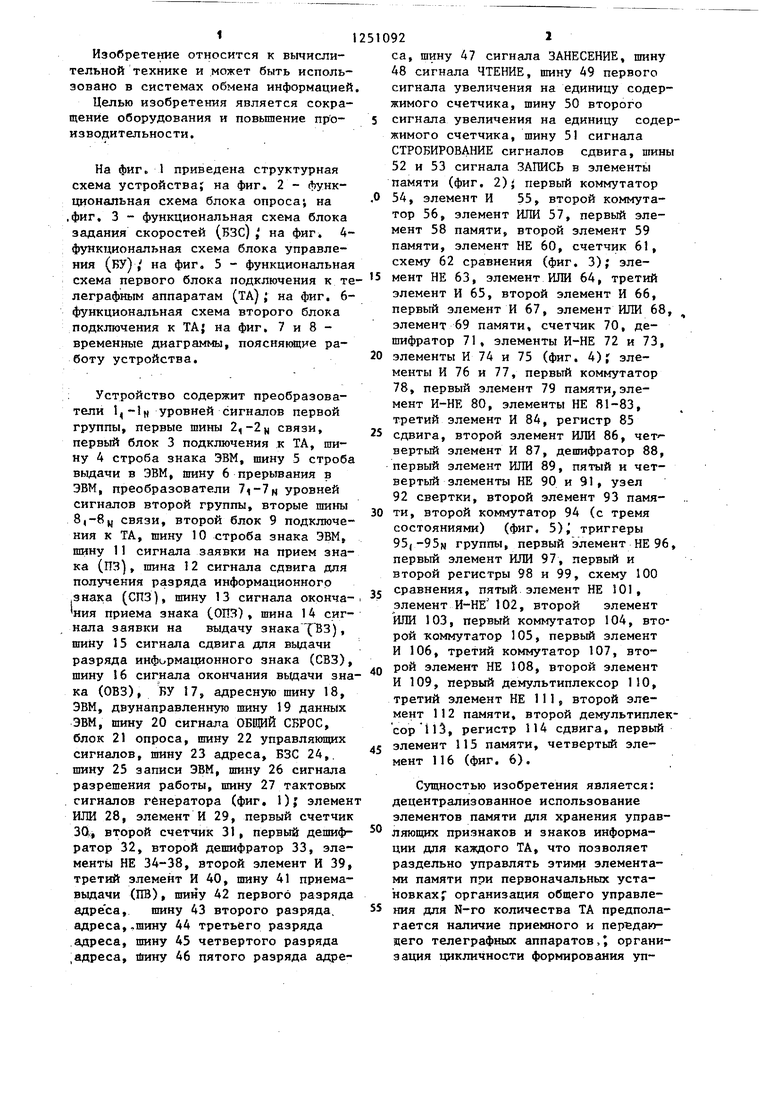

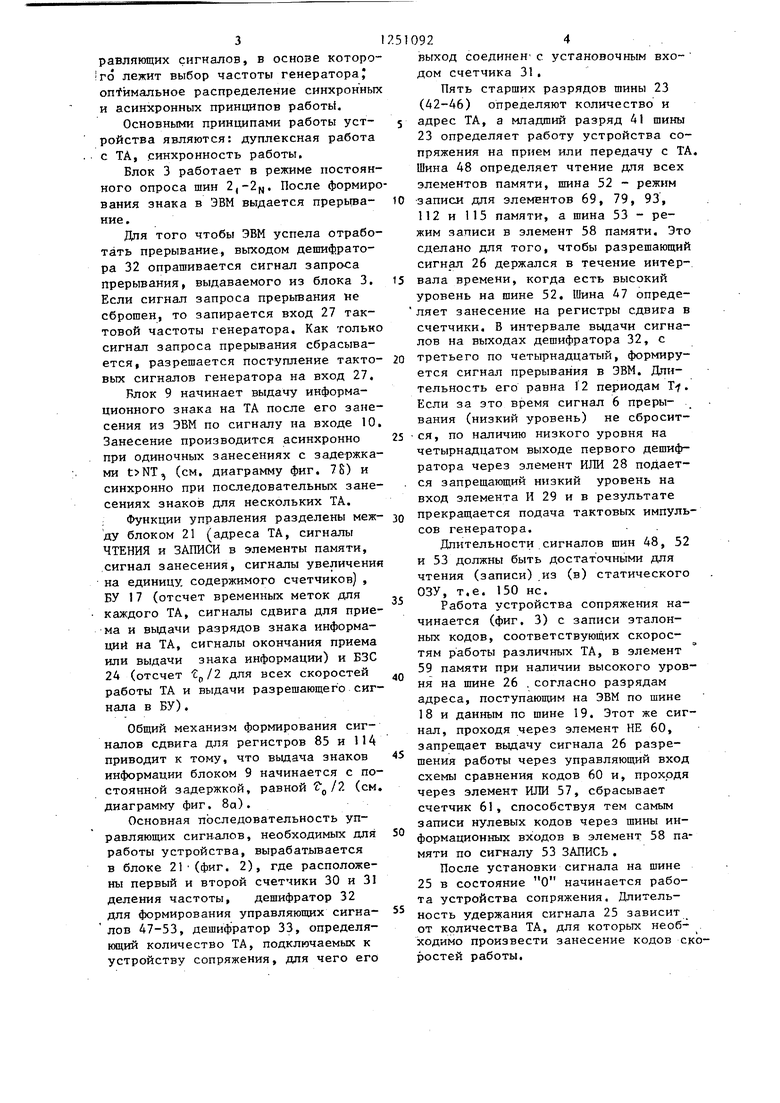

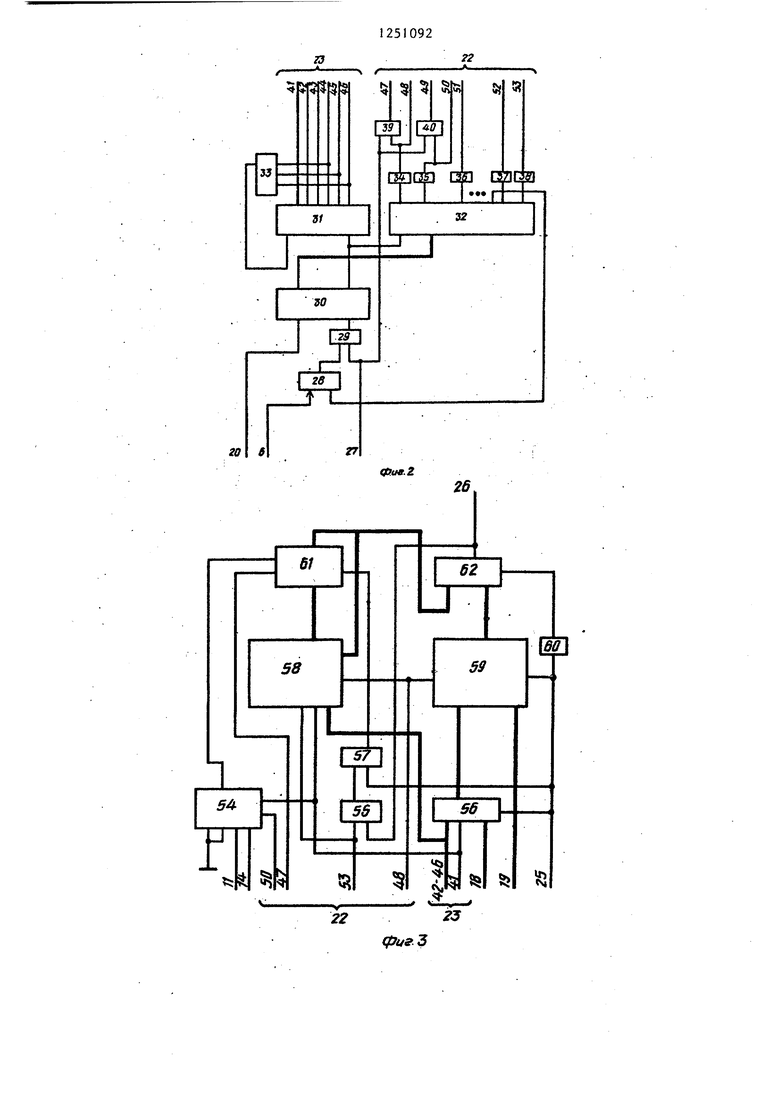

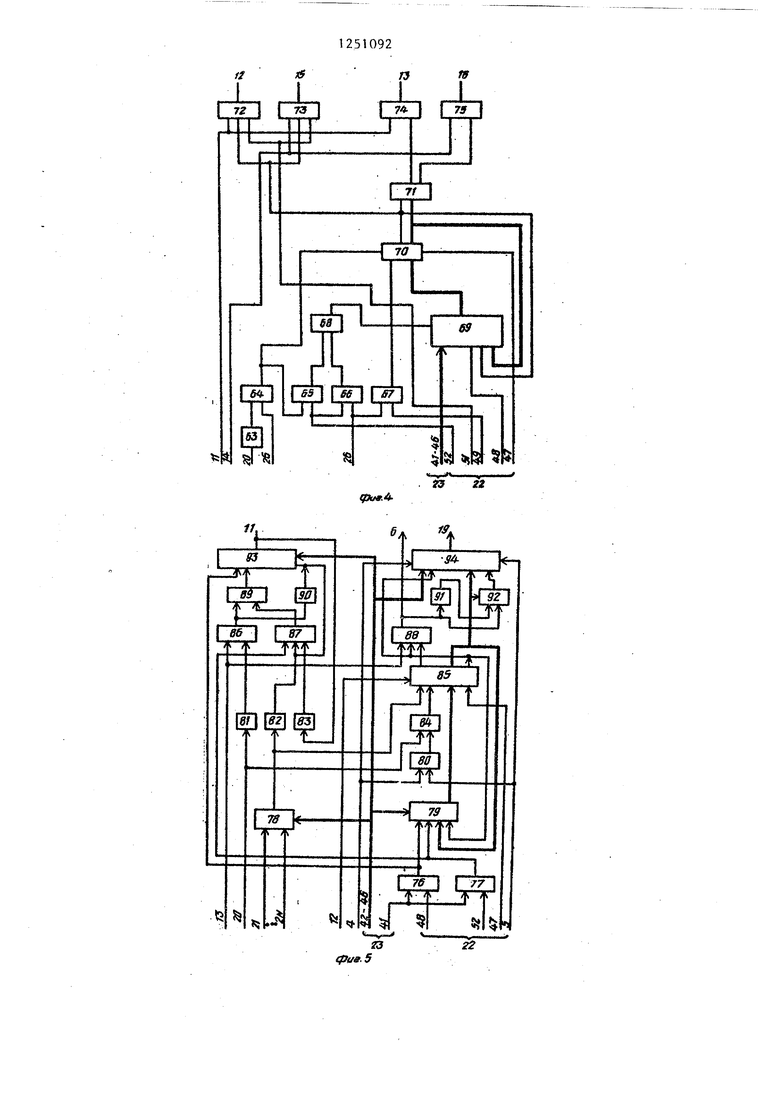

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока опросаi на ,фиг, 3 - функциональная схема блока задания скоростей (ВЗС) , на фиг. 4- функциональная схема блока управления (ВУ)/ иа фиг. 5 - функциональная схема первого блока подключения к телеграфным аппаратам (ТА); на фиг, 6- функциональная схема второго блока подключения к ТА{ на фиг, 7 и 8 - временные диаграммы, поясиякяцие работу устройства.

; Устройство содержит преобразователи 1,-1ц уровней сигналов первой группы, первые шины 2,-2« связи, первый блок 3 подключения к ТА, шину 4 строба знака ЭВМ, шину 5 строба выдачи в ЭВМ, шину 6 прерывания в ЭВМ, преобразователи 71-7ц уровней сигналов второй группы, вторые шины 8,-8к связи, второй блок 9 подключения к ТА, шину 10 строба знака ЭВМ, шину 11 сигнала заявки на прием знака (ПЗ), шина 12 сигнала сдвига для получения разряда информационного знака (СПЗ), шину 13 сигнала оконча иия приема знака (ОПЗ), шина 14 сигнала заявки на выдачу знака ( ВЗ), шину 15 сигнала сдвига для выдачи разряда информационного знака (СВЗ), шину 16 сигнала окончания вьщачи знака (ОВЗ), БУ 17, адресную шину 18, ЭВМ, двунаправленную шину 19 данных ЭВМ, шину 20 сигнала ОБЩИЙ СБРОС, блок 21 опроса, шину 22 управляющих сигналов, шину 23 адреса, БЗС 24,. шину 25 записи ЭВМ, шину 26 сигнала разрешения работы, шину 27 тактовых сигналов генератора (фиг, l)j элемен ИЛИ 28, элемент И 29, первый счетчик 3U, второй счетчик 31, первый дешифратор 32, второй дешифратор 33, элементы НЕ 34-38, второй элемент И 39, третий элемент И 40, шину 41 приема- выдачи (ПВ), шину 42 первого разряда адре са, шину 43 второго разряда, адреса,,шину 44 третьего разряда адреса, шину 45 четвертого разряда .адреса, йину 46 пятого разряда адреса, шину 47 сигнала ЗАНЕСЕНИЕ, шину 48 сигнала ЧТЕНИЕ, шину 49 первого сигнала увеличения на единицу содержимого счетчика, шину 50 второго

сигнала увеличения на единицу содержимого счетчика, шину 51 сигнала СТРОБИРОВАНИЕ сигналов сдвига, шины 52 и 53 сигнала ЗАПИСЬ в элементы памяти (фиг, 2); первый коммутатор

54, элемент И 55, второй коммутатор 56, элемент ИЛИ 57, первый элемент 58 памяти, второй элемент 59 памяти, элемент НЕ 60, счетчик 61, схему 62 сравнения (фиг, 3); элемент НЕ 63, элемент ИЛИ 64, третий элемент И 65, второй элемент И 66, первый элемент И 67, элемент ИЛИ 68, элемент 69 памяти, счетчик 70, дешифратор 71, элементы И-НЕ 72 и 73,

элементы И 74 и 75 (фиг, 4);; элементы И 76 и 77, первый коммутатор 78, первый элемент 79 памяти элемент И-НЕ 80, элемеиты НЕ 81-83, третий элемент И 84, регистр 85

сдвига, второй элемент ИЛИ 86, чет-- вертый элемент И 87, дешифратор 88, первый элемент ИЛИ 89, пятый и четвертый элементы НЕ 90 и 91, узел 92 свертки, второй элемент 93 памяти, второй коммутатор 94 (с тремя состояниями) (фиг, 5) триггеры 95,-95м группы, первый элемент НЕ 96, первый элемент ИЛИ 97, первый и второй регистры 98 и 99, схему 100

сравнения, пятый элемент НЕ 101, элемент И-НЕ 102, второй элемент ИЛИ 103, первый коммутатор 104, второй коммутатор 105, первый элемент И 106, третий коммутатор 107, второй элемент НЕ 108, второй элемент И 109, первый демультиплексор ПО, третий элемент НЕ 111, второй элемент 112 памяти, второй демультиплексор 13, регистр 114 сдвига, первьй

элемент 115 памяти, четвертый элемент 116 (фиг, 6).

Сущностью изобретения является: децентрализованное использование элементов памяти для храиения управляющих признаков и знаков информации для каждого ТА, что позволяет раздельно управлять этими элементами памяти при первоначальных установках f организация общего управления для N-ro количества ТА предполагается наличие приемного и передающего телеграфных аппаратов,J организация цикличности формирования уп3

равляющих сигналов, в основе которо 1го лежит выбор частоты генератораJ onfHManbHoe распределение синхронны и асинхронных принципов работь.

Основными принципами работы уст- ройства являются: дуплексная работа с ТА, синхронность работы.

Блок 3 работает в режиме постоянного опроса шин 2,-2f4. После формирвания знака в ЭВМ выдается прерьгаа- ние.

Для того чтобы ЭВМ успела отработать прерывание, вьпсодом дешифратора 32 опрашивается сигнал запроса прерывания, выдаваемого из блока 3. Если сигнал запроса прерьгеания не сброшен, то запирается вход 27 тактовой частоты генератора. Как только сигнал запроса прерывания сбрасывается, разрешается поступление такто- вых сигналов генератора на вход 27.

Клок 9 начинает выдачу информационного знака на ТА после его занесения из ЭВМ по сигналу на входе 10 Занесение производится асинхронно при одиночных занесениях с заде-ржка- ми , (см, диаграмму фиг, 7S) и синхронно при последовательных занесениях знаков для нескольких ТА. ; Функции управления разделены меж- ду блоком 21 (адреса ТА, сигналы ЧТЕНИЯ и ЗАПИСИ в элементы памяти, сигнал занесения, сигналы увеличения на единицу, содержимого счетчиков) , БУ 17 (отсчет временньгх меток для каждого ТА, сигналы сдвига для приема и выдачи разрядов знака информации на ТА, сигналы окончания приема или выдачи знака информации) и БЗС 24 (отсчет для всех скоростей работы ТА и выдачи разрешающего сигнала в ВУ).

Общий механизм формирования сигналов сдвига для регистров 85 и 114 приводит к тому, что выдача знаков информации блоком 9 начинается с постоянной задержкой, равной (см. диаграмму фиг, 8а),

Основная последовательность управляющих сигналов, необходимых для работы устройства, вырабатывается в блоке 21(фиг. 2), где расположены первый и второй счетчики 30 и 31 деления частоты, дешифратор 32 для формирования управляющих сигна- лов 47-53, дещифратор 33, определя- няций количество ТА, подключаемых к устройству сопряжения, для чего его

10924

выход соединен с установочным входом счетчика 31,

Пять старших разрядов шины 23 (42-46) определяют количество и адрес ТА, а младший разряд 41 шины 23 определяет работу устройства сопряжения на прием или передачу с ТА Шина 48 определяет чтение для всех элементов памяти, шина 52 - режим записи для элементов 69, 79, 93, 112 и 115 памяти, а шина 53 - режим записи в элемент 58 памяти. Это сделано для того, чтобы разрешающий сигнал 26 держался в течение интервала времени, когда есть высокий уровень на шине 52. Шина 47 опреде- ляет занесение на регистры сдвига в счетчики. В интервале выдачи сигналов на выходах дешифратора 32, с третьего по четырнадцатый, формируется сигнал прерывания в ЭВМ. Длительность его равна 12 периодам . Если за это время сигнал 6 прерывания (низкий уровень) не сбросит- ся, по наличию низкого уровня на четырнадцатом выходе первого дешифратора через элемент ИЛИ 28 подается запрещающий низкий уровень на вход элемента И 29 и в результате прекращается подача тактовых импульсов генератора.

Длительности сигналов шин 48, 52 и 53 должны быть достаточными для чтения (записи) из (в) статического ОЗУ, т.е. 150 НС.

Работа устройства сопряжения начинается (фиг. 3) с записи эталонных кодов, соответствующих скоростям работы различных ТА, в элемент 59 памяти при наличии высокого уровня на шине 26 , согласно разрядам адреса, поступающим на ЭВМ по шине 18 и данным по шине 19. Этот же сигнал, проходя через элемент НЕ 60, запрещает выдачу сигнала 26 разрешения работы через управляющий вход схемы сравнения кодов 60 и, проходя через элемент ИЛИ 57, сбрасывает счетчик 61, способствуя тем самым записи нулевых кодов через шины информационных входов в элемент 58 памяти по сигналу 53 ЗАПИСЬ .

После установки сигнала на шине 25 в состояние О начинается работа устройства сопряжения. Длительность удержания сигнала 25 зависит от количества ТА, для которых необходимо произвести занесение кодов скростей работы.

В каждом интервале Т, производится чтение из элемента 58 памяти кода i-ro ТА (первоначано равен нулю, где ), опредепякяцего интервал времени от начала вьщачи или приема разряда информации соответственно в блок 9 или 3, а также кода эталона и элемента 59 памяти по сигналу на тине 48.

При совпадении кодов на выходе схемы 62 сравнения появляется сигнал 26 высокого уровня, разрешающий прием (вьщачу) разряда информации. Этот же сигнал сбрасывает содержимое счетчика 61 с задержкой, обусловленной поступлением сигнала по шине 53 (соответствует шестнадцатому такту, фиг. , За).

Суммарная длительность шестнадцати тактов равна длительности сигнала на шине 41 (фиг, 7Ь). Работа с i-M ТА происходит с периодом 2КТз, равным 312,5 мкс. Это число кратно длительности разрядов для всех возможных скоростей работы ТА и дает возможность подсчетом этих интервало определить длительность разряда информации tp/2 в БЗС 24.

Назначением ВУ 17 является отсчет интервалов времени и 7,5 выдача сигцалов / 12 и 15 сдвига, выдача сигналов окончания работы по приему или вьщаче знака информации соответственно на шинах 13 и 16 за i-й ТА. Во времй общего сброса (наличие низкого уровня на шине 20) или при записи эталонных кодов в элемент 59 памяти (наличие высокого уровня на шине 25) происходит обну ление счетчика 70 сигналов с выхода элемента ИЛИ 64, стробированным сигналом записи по шине 52, запись обнуленного значения счетчика 70 в элемент 69 памяти по адресу, поступающему с шин 41-46.

При работе по отсчету времени выполняются следукйцие операции: чтение из элемента 69 памяти{ занесение прочитанного кода в счетчик 70 по сигналу 47{ увеличение на единицу содер- жимого счетчика 70 по сигналу с шины 49 при наличии Сигнала на шине 26, запись содержимого счетчика 70 в элемент 69 памяти.

Формирование сигналов сдвига происходит следующим образом.

Стробирующий импульс с шины 51 поступает позже сигнала с шины 49

0

5

0

5

(фиг. 7q), по которому увеличивается на единицу содержимое счетчика 70. На фиг. 8 условно показано время удержания сигнала на выходе младшего 5 разряда этого счетчика, а на фиг.8Ь, показаны соответственно прием и вьг- дача разрядов информационного знака относительно сигнала на фиг. 88. Первоначально на младшем разряде счетчика 70 (после чтения из элемента памяти) - низкий уровень. При поступлении в БУ 17 первого сигнала с шины 26 и сигнала с шины 49 на младшем разряде счетчика 70 появляется сигнал высокого уровня с задержкой срабатывания счетчика t « «50 НС. После этого на одном из выходов 12 или 15 появляется сигнал сдвига высоким уровнем по сигналу с шины 51.

При поступлении в БУ 17 следующего сигнала с шины 26 через второй интервал tp/2 (фиг. 8) по сигналу с шины 49, значение младшего разряда счетчика 70 становится равным нулю, и при появлении сигнала с шины 51 сигнал сдвига (с шины 12 или 15) не выдается. Таким образом, сигналы сдвига вьщаются через ин0

5

5

тервалы времени, равные tg (см.

фиг. 8 &, 2 ) на нечетные импульсы с шины 26.

Окончание приема (передачи) знака информации производится после того, как счетчик 70 сосчитает 15 или 16 интервалов. Тогда на одном из выходов, соответствующем приему (13) или выдаче (16) появится сигнал высокого уровня (фиг. 8&, е).

Прием знаков с ТА происходит в блоке 3 следующим образом (фиг, 5).

Код адреса ТА с шин 41-46 поступает на входы коммутатора 78, элементов 79 и 93 памяти на первые ин- 5 формационные входы коммутатора 94 с тремя состояниями и держится в течение периода изменения адреса Tj. В течение Т (фиг. 7а) происходит: чтение знаков в элементы 79 и 93 при наличии совпадения сигналов на шинах 41 и 48 на входе элемента И 764 занесение информадаи, прочи- ;танной из элемента 79 памяти, на регистр 85 сдвига по сигналу на шине 47 сдвиг регистра 85 по сигналу СПЗ на шине 12 (т.е. занесение значения нового разряда информации с выхода коммутатора 78){запись

измененного содержимого регистра 85 в элемент 79 памяти при совпадении сигналов шинах 41 и 52 на входе элемента И 77,

При поступлении сигнала СТАРТ на одну из шин 2,-2, соответствующего коду адреса ТА на шинах 42- 46, на выходе коммутатора 78 появляется сигнал низкого уровня, который инвертируется на элементе НЕ 82 и поступает на вход элемента И 87, на другие входы которого поступают сигналы записи с выхода элемента И 77 и сигнал с выхода элемента НЕ 83, указывающий на отсутствие ПЗ на ши«е 11. Совпадение эти трех сигналов дает сигнал высокого уровня, которъ1й, проходя через эле-г мент ИЛИ 89, поступает на вход ЗАПИСЬ элемента 93 памяти. На информационный вход в это время поступает сигнал высокого уровня с выхода элемента НЕ 82.

Сигнал ПЗ на щине 11 может быть сброшен или сигналом.ОПЗ (высокий уровень на шине 13), означающим окончание приема знака с ТА, или сигналом ОБОЩЙ СБРОС (низкий уровень на шине 20).

Во время приема знака значение сигнала СТОП заносится на регистр 85 сдвига два раза (седьмым и восьмым сигналами сдвига на шине 12). На дешифратор 88, служащий для определения окончания приема знака информации, подается только значение., полученное на седьмом сдвиге (нА третий вход). На второй его вход подается сигнал с выхода восьмого разряда регистра 85 сдвига низким уровнем (разряд СТАРТ), а на первый вход дешифратора 88 подается сигнал ОПЗ с шины 13. При этом на выходе появляется сигнал прерывания в ЭВМ . (шина 6) низким уровнем, который по- ступает также на вход узла 92 свертки. Инверсия этого сигнала на элементе НЕ 91 подается на вход узла 9|2 свертки. Эти два управляющих сигнала совместно с пятью разрядами ин- формации с выходов регистра 85 с второго по шестой определяют формирование контрольного разряда, который совместно с разрядами информации подается на вторые входы коммута тора 94.

До выдачи прерывания в ЭВМ на шине 4, соединенной с входом управле

25

5 0 5

2510928

НИН третьим состоянием коммутатора 94, поддерживается высокий уровень удержания его выходов в высокоомном состоянии, а на шину 5 (адресный 5 вход) подается низкий уровень. Как только обрабатывается прерывание в ЭВМ на шину 4 подается низкий уровень, на шине 5 остается низкий уровень и на выход коммутатора 94 пода10 ются разряды адреса ТА. После приема адреса ТА на шину 5 подается высокий уровень и на выход коммутатора поступают разряды знака телеграфной информации. После приема

15 знака информации на шину 4 подается высокий уровень, который в сочетании с высоким уровнем на шине 5, проходя через элемент И-НЕ 80 и элемент И 84, низким уровнем сбрасыва20 ет регистр сдвига. После этого снимается сигнал прерывания в ЭВМ с шины 6 (с выхода четвертого дешифратора) , нулевое значение регистра 85 сдвига записывается в элемент 79 памяти и цикл формирования и выдачи в ЭВМ знака информации завершается. С выходов преобразователей Ij-l за те номера ТА, которые не подклю-

чены к устройству сопряжения, должен

tit ti « .

30

5

0

выдаваться уровень I.,

Работа блока 9 (фиг. 6) происходит следующим образом.

По шинам 18 и 19 из ЭВМ поступают соответственно код адреса ТА и код передаваемого знака с восьмым стартовым, а также первым и вторым стоповыми разрядами. Разряды информационного знака записываются в разряды с третьего по седьмой причем старший разряд знака находится на седьмой позиции.

При подаче высокого уровня на шину 10 передним фронтом происходит занесение адреса ТА и знака информации соответственно на первый 98 и второй 99 регистры. Высокий уровень первого разряда регистра 98 используется как запрос на запись знака во второй 112 и запись ПВ в первый 115 элементы памяти и поступает на управляющий вход схемы 100 сравнения, выход которой поступает на входы коммутаторов 104, 105, 107 и на первый вход элемента ИЛИ 103. Коммутаторы 104, 105 и 107 переключаются и на адресные входы элементов 112 и 115 памяти подаются разряды регистра 98 с четвертого по восьмой с вы9

ходов коммутаторов 10А и 107, На информационные входы элемента 112 памяти подаются разряды регистра 99 с первого по восьмой через коммутатор 105.

Дпя формирования сигнала ЗАПИСЬ для элементов 112 и 115 памяти необходимо совпадение высокого уровня с выхода элемента РШИ 103, сигнала шины 41, инвертированного на элементе НЕ 101, и сигнала ЗАПИСЬ (шина 52) на элементе И 109, Высокий уровень с выхода элемента И 109 разрешает запись в элементы 112 и 115 памяти, В случае записи в зле- мент 112 памяти информационного знака (информационные разряды регистра 99 с первого по восьмой) и элемент 115 памяти записывается сигнал высокого уровня с выхода элемента НЕ 108, В конце цикла записи на элементе И-НЕ 102 совпадением сигналов на шине 41 ПВ, на шине 52 и выходе. схемы 100 сравнения формируется сигнал сброса регистров 98 и 99 низко- го уровня. Длительность сигнала на шине 52 равна длительности Т, (около 350 не),

После окончания записи информационного знака в элемент 112 памя- ти начинается автономная от ЭВМ поразрядная выдача его на ТА, которая состоит из следующих тактов: чтение из элементов 112 и 115 памяти соответственно знака информации и ПВ 41 по высокому уровню сигнала на выходе элемента И 106; занесение информационного знака в регистр 114 сдвига по отрицательному фронту сигнала на шине 47 занесение значения восьмого старшего разряда регистра 114 сдвига в один из триггеров 95| - 95 по переднему положительному фронту сигнала на шине 15 СВЗ, Триггер i-го ТА определяется синхросигналом с выхода первого демультиплексора, на адресные входы которого подаются шины 42-46 адреса TAf сдвиг содержимого регистра 114 задним отрицательным фронтом сигнала на ши- не 15 СВЗ«, запись содержимого регистра 114 в элемент 112 памяти (через входы коммутатора 105) при наличии высокого уровня на выходе элемента И 109.

Третье и четвертое из указанных действий выполняются в случае поступления сигнала по шине 15. Так как

9210

информационный последовательный вход соединен с землей, то на позиции сдвигаемого младшего разряда записываются нули. Если сигнала сдвига нет, то в элемент 112 памяти записывается неизменное значение содержимо- го регистра 114 сдвига.

Значение разряда информации, занесенное на один из триггеров 95, держится на шинах до следующего сдвига регистра 114, Сигнал, поступающий по шине 16 ОВЗ, держится до конца периода Тз и, проходя через .элементы ИЛИ 97 и 103, при совпадении с сигналом на шине 52 производит запись содержимого регистра 114 (высокий уровень на восьмом и низкий - на остальных разрядах) в элемент 112 памяти и сигнала низкого уровня с выхода элемента НЕ 108 в элемент 115 памяти (сигнал ПВ), Запись низкого уровня в элемент 115 памяти (адрес соответствует коду на шинах 42- . 46, поступающему через коммутатор 107) означает, что в БЗС 24 прекратится подсчет временных интервалов до следующего получения знака информации и адреса ТА от ЭВМ, Для первоначальной установки схемы используется сигнал ОБЩИЙ СБРОС на шине 20, поступающий (низким уровнем) на входы установки в единичное состояние триггеров 95(-95ц и на вход установки в нуль регистра сдвига. Этот же сигнал через элемент НЕ 96 и элемент ИЛИ 103 аналогично сигналу ОВЗ, поступающему по шине 16, производит запись в элементы 112 и 115 памяти первоначальных нулевых значений знака информации и ПВ соответственно.

Для того чтобы в блоках 3 и 9 по адресам всех ТА были записаны при первоначальном включении устройства сопряжения нулевые значения ПЗ 11 и ВЗ 14 надо, чтобы длительность сигнала на шине 20 была равна i N-312,5 МКС,

Если занесение в регистры 98 и 99 происходит редко с интервалами t T,j 2 N, то оно может производится асинхронно. В этом случае информационный знак и номер ТА запоминаются соответственно на регистрах 98 и 99, В момент совпадения адреса ТА с регистра 98 и адреса ТА, выдаваемого с блока 21, происходит занесеII

ние знака информации в элемент 112 памяти.

В случае необходимости занесения информаиионньгх знаков для нескольких ТА (выдача происходит ча- ще, чем ) необходимо синхронизировать выдачу информационных знаков на ТА с адресами, которые выдаются из блоков 21 . Затем с интервалом смены адресов блока 21, равным Т, выдаются знаки в следующие ТА, Информацию о номере ТА ЭВМ может получить с двунаправленной шины 19 (необходимо подать сигнал низкого уровня на шину А).

В случае, если программе ЭВМ необходимо знать о занесении в блок 9, а затем о выдаче на ТА знака, можно организовать прерывание 2 и прерывание 3 соответственно о положительном и отрицательном перепадах сигнала на шине 14.

Формула изобретения

Устройство для сопряжения ЭВМ с телеграфными аппаратами, содержащее блок опроса, две группы преобразователей уровней сигналов, два блока подключения к телеграфным аппаратам, блок управления, группа информационных входов первого блока подключения к телеграфным аппаратам через преобразователи уровней сигналов первой группы подключена к выходам телеграфных аппаратов, группа .информационных выходов второго блока подключения-к телеграфным аппаратам через преобразовател уровней сигналов второй группы подключе на к входам телеграфных аппаратов, выходные адресная и управляющая щи- ны блока опроса подключены соответственно к адресному и управляющему, входам первого и второго блоков подключения телеграфных аппаратов, отличающееся тем, что, с целью сокращения оборудования и повышения производительности, устройство содержит блок задания скорое- тей, состоящий из двух элементов памяти, счетчика, схемы сравнения, двух компараторов, элементов И, ИЛИ и НЕ, при этом выход первого коммутатора соединен со счетным входом счетчика, информационный вход которого соединен с выходом первого элемента памяти, а вход сброса - с вы

5 О 5

5

5

109212

ходом элемента ИЛИ, выход счетчика соединен с информационным входом первого элемента памяти и первым информационным входом схемы сравнения, ВТО,ой информационный и разре- шаюпц й входы которой соединены соответственно с выходом второго элемента памяти и выходом элемента НЕ, выход схемы сравнения соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, первый информационный вход второго коммутатора соединен с адресной птной ЭВМ, а второй информационный вход и адресный вход первого элемента памяти соединены с вьтходной адресной шиной блока опроса, выход второго коммутатора соединен с адресным входом второго элемента памяти, информационный вход которого соединен с шиной данных ЭВМ, первьй управляющий вход второго коммутатора, второй вход элемента ИЛИ, вход записи второго элемента памяти и вход элемента НЕ соединены с шиной записи ЭВМ, кроме того, блок опроса содержит два счетчика, два дешифратора,

элемент ИЛИ, три элемента И, пять элементов НЕ, при этом в блоке опроса выход элемента ИЛИ соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, группа разрядных выходов которого соединена с группой входов первого дешифратора, разрядный выход первого счетчика соединен с входом первого дешифратора и счетным входом второго счет- чик а, вход сброса которого через второй дешифратор подключен к группе выходов его старших разрядов, вход сброса первого счетчика соединен с шиной общего сброса устройства,первый и второй выходы первого дешифратора соответственно через первый и второй элементы НЕ соединены с первыми входами второго и третьего элементов И, вторые входы которых и второй вход первого элемента И подключены к тактовому выходу ЭВМ, выходы второго счетчика образуют выходную аДрГесную шину блока, выходы второго и третьего элементов И и выходы первого - пятого элементов НЕ образуют выходную управлякяцую шину бло- .ка, третий, четвертый, пятый и шестой выходы первого дешифратора соединены соответственно с входом трегьего элемента НЕ, первым входом элемента ИЛИ и входами четвертого и пятого элементов НЕ, выходы второго элемента НЕ, второго элемента И,пяг- того элемента НЕ, первого элемента НЕ череэ выходную управляющую шину соединены соответственно с первым информационным входом первого коммутатора, разрешающим входом счетчика, вторым входом элемента Ни входом записи первого элемента памяти, входами чтения nepieoro и второго элементов памяти блока задания скоростей, второй управляющий вход второго коммутатора, разрешающий вход первого элемента памяти блока задания скоростей соединены с выходом первого разряда второго счетчика блока опроса, причем блок уп

равления содержит элемент памяти.

счетчикi дешифратор, два элемента ИЛИ, пять элементов И, два элемента И-НЕ и элемент НЕ, при- этом в блоке управления адресный вход элемента памяти соединен с выходной адрес- ной шиной блока опроса, а выход соединен синформационным входом счет- чика, счетный вход и вход сброса которого соединены соответственно с выходами первого элемента И и перво- го элемента ИЛИ, первый вход которого через элемент НЕ соединен с пганой общего сброса устройства, а второй вход - с шиной записи ЭВМ, первые входы первого и второго элементов И соединены с выходом схемы сравнения блока задания скоростей, второй вход первого элемента И соединен через выходную управляющую шину с выходом третьего элемента И блока опроса, выход четвертого элемента НЕ которого соединен через выходную управлягющую шину со вторым входом второго и первым входом третьего элементов И блока управления, в ко- тором вьгход первого элемента ИЛИ содинен с вторым входом третьего элемента И, выходы второго и третьего элементов И через второй элемент ИЛИ соединены с входом записи эле- мента памяти, информационный вход которого соединен с группой разрядных выходов счетчика, соединенных также с входами дешифратора, первый я второй выходы которого соединены с первыми входами четвертого и пятого элементов И, выходы первого элемента И, первого и третьего эле

ментов НЕ блока опроса через выходную управляющую шину соединены соответственно с разрешающим входом счетчика, входом чтения элемента памяти и первыми входами первого и второго элементов блока управления, вторые входы которых соединены с выходом первого разряда счетчика кроме того, первый блок подключения к телеграфным аппаратам содержит регистр сдвига, два коммутатора, два элемента памяти, дешифратор, четыре

элемента И, два элемента ИЛИ, элемент И-НЕ, пять элементов НЕ и узел свертки, при этом информационные входы первого коммутатора образуют группу информационных входов блока, а выход соединен с последовательным информационным входом регистра сдвига, параллельный информационный вход которого соединен с выходом первого элемента памяти, информационный вход которого соединен С параллельным выходом регистра сдвига, первым входом узла свертки и первым информационг ным входом второго коммутатора, выход которого соединен с шиной данных ЭВМ, а второй информационный вход, адресный вход первого и второго элементов памяти управляющий вход первого коммутатора и первые входы второго и первого элементов И образуют адресный вход блока, установочный вход регистра сдвига соединен с выходом третьего элемента И, первый вход которого соединен с выходом элемента И-НЕ, вьгход второго элемента памяти через первый элемент НЕ соединен с первым входом четвертого элемента И, второй вход которого соединен с информационным входом второго элемента памяти и через второй элемент НЕ - с выходом первого коммутатора, а выход соединен с первым входом первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента ИЛИ и входом записи второго элемента памяти, вход чтения которого соединен с вы- ходо2 первого элемента И, соединенным также с входом чтения первого элемента памяти, вход записи которого и третий вход четвертого элемента

И соединень; с выходом второго элемен- та И, выход третьего элемента НЕ соединен с первым входом второго элемента ИЛИ, первый и второй разрядные выходы регистра сдвига соединены с первым и вторым входами дешифратора,

13

выход которого непосредственно и через четвертый элемент НЕ соединен с вторым и третьим входами узла свертки, выход которого соединен с соответствующим входом первой группы вх дов второго коммутатора, первый разрядный выход регистра сдвига соединен с соответствующим разрядом информационного входа первого элемента памяти и соответствующим вхо- дом второй группы информационных входов второго коммутатора, выход второго элемента ИЛИ через пятый элемент НЕ соединен с информационным входом второго элемента памяти, вы- ход дешифратора соединен с шиной прерывания ЭВМ и с вторым входом элемента ИЛИ блока опроса, вход третьего элемента НЕ и второй вход третьего элемента И соединены с шиной об- щето сброса устройства, второй вход второго элемента ИЛИ и третий вход дешифратора соединены с выходом четвертого элемента И блока управления, выход первого элемента И-НЕ которо- го соединен со входом сдвига регистра сдвига, первого блока подключения к телеграфным аппаратам, вход переключения в третье состояние и управляющий вход второго коммутато- ра подключены соответственно к шинам Строб выдачи и Код выдачи ЭВМ, соединенным также с первым и вторым входами элемента И-НЕ, вход разрешения параллельной записи ре- гистра сдвига и вторые входы первого и второго элементов И соединены соответственно с выходом второго элемента И,, первого и четвертого элементов НЕ блока опроса, выход вто- рого элемента памяти первого блока подключения к телеграфным аппаратам соединен с третьим входом первого элемента И-НЕ, вторым входом четвертого элемента И блока управления и вторым информационным входом первого коммутатора блока задания скоростей, кроме того, второй блок подключения к телеграфным аппаратам содержит два элемента памяти, регистр сдвига, два демультиплексора, группу триггеров, два регистра, схему сравнения, три коммутатора, два элемента ИЛИ, два элемента И, элемент И-НЕ и пять элементов НЕ, при этом выходы триггеров группы образуют группу информационных выходов блока, а их информационные и строби09216

рующие входы соединены соответственно с выходами первого и второго яе- мультиплексоров, а входы сброса подключены к шине общего сброса уст- ро йства, соединенной с входом сброса регистра сдвига и через первый элемент НЕ - с- первым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ и через второй элемент НЕ - с информационным входом первог элемента памяти, входь чтения и записи первого и второго элементов памяти ..соединены соответственно с выходами первого и второго элементов И, адресный и информационный входы второго элемента памяти соединены соответственно с выходами первого и второго коммутаторов, первые группы информационных входов которых соединены соответственно с в;ыходами первого и второго регистров, информационные и установочные входы которых соединены соответственно с шинами адреса и данных ЭВМ и с выходом элемента И-НЕ, первый вход которого, управлякщце входы первого, второго и третьего коммутаторов, второй вход второго элемента ИЛИ соединены с ходом схемы сравнения, первая и вторая группы информационных входов которой соединены соответственно с группой выходов первого регистра, соединенной с первыми информационными входами первого и третьего коммутаторов и выходной адресной шиной блока опроса, соединенной с вторыми информационными входами первого и третьего коммутаторов и адресными входами первого и второго демуль- тийлексоров, информационные входы которых соединены соответственно с выходами третьего и четвертого эле- .ментов НЕ, последовательный выход

регистра сдвига соединен с входом четвертого элемента НЕ и информа- ционньм входом второго коммутатора, вторая группа информационных входов которого соединена с параллельным выходом регистра сдвига, параллельный информационный вход которого соединен с выходом второго элемента памяти, выход первого элемента памяти соединен с вторым входом элемента И-НЕ, выход второго элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого и первый вход первого элемента И

п

соединены с выходом пятого элемента НЕ, разрядный выход первого регистра соединен с управляющим входом схемы сравнения, выход третьего коммутатора соединен с адресным входом первого элемента памяти, выход которого соединен с третьим входом второго элемента И-НЕ и вторыми входами пятого элемента И и второго элемента И-НЕ блока управления и вторым информационным входом первого коммутатора блока задания скоростей, вход сдвига регистра сдвига и вход третьего элемента НЕ второго блока подключения к телеграфным аппаратам соединены с выходом второго элемента И-НЕ блока управления, третьи вхо1251.09218

ды элемента И-НЕ и второго элемента И второго блока подключения к телеграфным аппаратам через выходную управляющую щину соединены с выходом четвертого элемента НЕ блока опроса, второй вход первого элемента И через выходную управляющую шину соединен с выходом первого элемента НЕ блока опроса, вход пятого элемента НЕ через выходную адресную щину соединен с выходом первого разряда второго счетчика блока опроса, разрещающие входы первого и второго регистров соединены с щиной Строб 15 знака ЭВМ, второй вход первого элемента ИЛИ соединен с выходом пятого элемента И блока управления.

0

il

фиг.1

го s

222S

фиг. 5

фив.2

26

tS 22

23

22

20

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для сопряжения телеграфных каналов с электронной вычислительной машиной | 1982 |

|

SU1067494A1 |

| Устройство для сопряжения между ЭВМ, оперативной памятью и внешним запоминающим устройством | 1988 |

|

SU1531103A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1256084A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

Изобретеиие относится к области вычислительной техники и может быть использовано в системах обмена информацией. Цель изобретения - сокращение оборудования и повьшение производительности. Устройство содержит блок опроса, блок управления (БУ), адресные шины ЦВМ, шины связи, блоки подключения к телеграфным аппаратам, преобразователи уровней сигналов, блок задания скоростей (БЗС), Использование устройства позволяет ,кроме сокращения оборудования, увеличить производительность работы, обеспечить высокое быстродействие и возможность подключения к ЦВМ до 280 телеграфных установок В ил.

yOOffC

1

fSOtK r

p

гощ

27 I шв « mm lшг-ггпlШ-Ш-MжlLJЦш m ц,

3 Д tf g 7 9 9 JO n 12 n 19- fS №

5г1У

ps

,9Омс

iOtfc

-fc

35 sjs SL

«/«r

.

4 2 Ъ 5 S 7 в 9 10 11 12 13 П 15 16

/2ГГ/73) IIIIIIIII

1Ъ(ОЛЗ}

1б(ОвЪ)

фиг. 8

| Устройство для сопряжения телеграфных каналов с вычислительной машиной | 1978 |

|

SU748403A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения телеграфных аппаратов с вычислительной машиной | 1975 |

|

SU608149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1984-12-24—Подача