(54) УСТЮЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

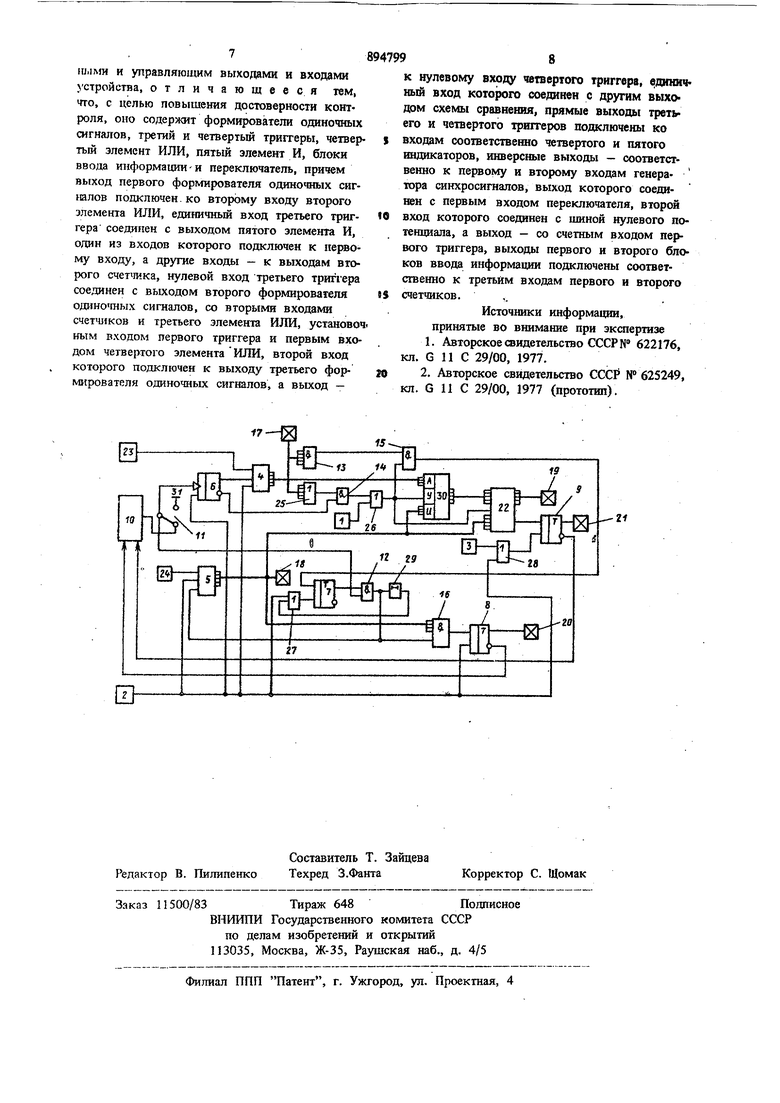

Изобретение относится к запоминающим устройствам и может быть применено для контроля типовых элементов замены (ТЭЗ) памяти. Известно устройство для контроля блоков памяти, представляющее собой стационарную установку, в которой применяется единственная программа контроля блоков памяти 1. Недостатками устройства являются его сло ность и ограниченная область применения. Наиболее близким по технической сущности к предлагаемому является устройство для контроля блоков памяти, содержащее блок ав томатического управления, блок формирования кода адреса, блок поразрядного сравнения и блок индикации, причем блок автоматического управления соединен с блоком формирования кода адреса, блоком формирования тестов и со входом управления контролируемого блока памяти. С адресным входом блока памяти соединен блок формирования кода адреса. Информационный вход контролируемого блока соединен с блоком формирования тестов и с блоком поразрядного сравнения, с которым соединен так же выход блока памяти. Управляющий вход блока поразрядного - сравнения соединен с блоком автоматического управления, а выход блока поразрядного сравнения соединен с блоком индикации 2. Недостатком известного устройства является низкая достоверность контроля, так как оно позволяет только определить неисправный блок памяти, но не обеспечивает получение информации о характере неисправностей, поскольку в нем применяется единственная неизменяемая программа контроля. Цель изобретения - повьпиение достоверности контроля блоков памяти, а также расширение области применения устройства за счет обеспечения возможности контроля отдельных ТЭЗ памяти. Ноставленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее генератор синхросигналов, триггеры, , счетчики, схему сравнения, элементы И, зле-. менты ИЛИ, индикаторы и элемент задержки, причем счетный вход первого триггера соединен с первым входом первого элемента И, второй вход которого подключен к прямому выходу второго триггера, прямой выход первого триггера соединен с первым входом первого счетчика, выходь которого подключены ко входам первого индикатора, первого элемента ИЛИ и второго элемента И, инверсиьй. выход первого триггера соединен с. первым входом третьего элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к первому входу второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И и управляющим входом схемы сравнения, второй вход четвертого элемента И подключен к выходу второго элемента И, а выход - к единичному входу второго триггера, нулевой вхо которого соединен с выходом третьего элемен та ИЛИ, первый вход которого подключен к выходу элемента задержки, вход которого соединен с выходом первого элемента И к первым входом второго счетчика, выходы которого подключень ко входам второго индикатора и одним из входов схемы сравнения, оД ни из вькодов которой соединены со входами третьего индикатора, выходы первого и второго счетчиков, выход второго элемента ИЛИ. и другие входы схемы сравнения являются соответственно адресными, информационными и управляющими выходами и входами устройства, введены формирователи одиночных сигналов, третий и четвертый триггеры чeтвep тый элемент ИЛИ, пятый элемент И, блоки ввода информации и переключатель, причем выход первого формирователя одиночных сигналов подключен ко второму входу второго элемента ИЛИ, единичный вход третьего триггера соединен с выходом пятого элемента И, один из входов которого подключен к первому входу, а дрзтие входы - к выходам второго счетчика, нулевой вход третьего триггера соединен с выходом второго формирователя одиночных сиг галов, со вторыми входами счетчиков и третьего элемента ИЛИ, установоч ным входом первого триггера и первым входом четвертого элемента ИЛИ, второй вход которого подключен к выходу третьего формирователя одиночных сигналов, а выход - к нулевому входу четвертого триггера, единич ный вход которого соединен с другим выходом схемы сравнеш1я, прямые выходы третьего и четвертого триггеров подключе1П 1 ко входам соответственно четвертого и пятого индикаторов, инверсные выходы - соответственно к первому и второму входам генератора синхросигналов, выход которого соедннен с первым входом переключателя, второй вход которого соединен с тиной нулевого потенциала, а выход - со счетным входом первого триггера, выходы первого и второго блоков ,4 ввода информации подключены соответственно к третьим входам первого и второго счетчиков, На чертеже изображена функциональная схема устройства. Устройство содержит первый }, второй 2, и третий 3 формирователи одиночных сигналов, первый 4 и второй,5 счегчики, триггеры 6-9 с первого По ча№ертый, гене1атор 10 синхросигналов, переключатель 11, эяемевты И 12-16 с первого по пятый, йнДИkaтopы 17-21 с первого по пятый, схему 22 сравнения, иервый 23 и Второй 24 блоки ввода информации, элементы ИЛИ 25-28 с первого по четвертый и элемент 29 задержки. Выход первого формирователя 1 подключен ко второму входу элемента ИЛИ 26, Единичный вход триггера 8 соединен с выходом элемента И 16, один из входов которого под ключен. к первому входу, а другие входы - к выходам счетчика 5. Нулевой вход триггера 8 соединен с выходом формирователя 2, со вторыми входами счетчиков 4 и 5 и элемента ИЛИ 27, установочным входом триггера 6 н первым входом элемента ШШ 28, Второй вход элемента ШШ 28 подключен к выходу формирователя 3, а выход - к нулевому входу триггера 9, единичный вход которого соединен с другим выходом схемы 22 сравнения. Прямые выходы триггеров 8 и 9 подключены ко входам соответ(енно индикаторов 20 и 21, а инверсные выходы - QOответственно к первому и второму входам генератора 10 синхросигналов, вь1ход которого соединен с первым входом переключателя 11, Выходы блоков 23 и 24 ввода информации подключены соответственно к третьим входам счетчиков 4 и 5, Вход, адресные, информационные и управляющий выходы устройства подключаются соответственно к выходу и соответствующим входам контролируемого блока 30 Памяти, Второй вход переключателя 11 соединен С шиной 31 нулевого потенциала, а выход - со счетным входом первого триггера 6. Устройство работает следующим образом, Оператор устанавливает устройство в исходное состояние при помощи формирователя 2, единичный сигнал с выхода которого переводит триггеры 6-9 и счетчики 4 и 5 в нулевое состояние. Устройство работает в автоматнческом и полуавтоматическом режимах. Для работы в автоматическом режиме оператор переключателем 11 подключает вь1ход генератора синхросигналов 10 к счетному входу триггера б и входу элемента И 12, Сигналы 1 с инверсных выходов триггеров 8 и 9 ртзрешают работу генератора 10. , Первый синхросигнал с выхода генератора 10 переводит триггер 6 в единичное состояаше Сигнал 1 с прямого выхода триггера 6 записьшает в счетчик 4 число, являющееся кодом адреса, причем счет адресов начинается с единицы. Второй счетчик 5 вырабатывает вектор ко&трольного теста, который поступает на информационные выходы устройства и записывается в линейку контролируемого блока 30 пакюти по адресу, сформированному счетчиком 4. Следующий сигнал синхронизации с выхода генератора 10 переводит устройство в режим считывания информации из блока 30 памяти и разрешает работу схемы 22 сравнения. В последней осуществляется поразрядное сравнение считанного из блока 30 памята вектора информащш с вектором контрольного теста, сформированного счетчиком 5. В случае несовпадения на единичный вход триггера 9 с выхода схемы 22 сравнения поступает сигнал, по которому прерывается работа генератора 10 «синхросигналов и прекращается дальнейшая проверка йяока 30 памяти. Одновременно результат сравнения поступает на инр жатор 19. 1Ъщикатор 21 сигнализирует об остановке работы устройства. По индикатору 17 оператор определяет адрес неисправной линейки блока 30 памяти. Индикатор 18 показьшает вектор контрольного теста, по которому производилас проверка. Оператор определяет неисправную ячейку блока 30 памяти путем сравнения вектора контрольного теста с вектором - резуль татом сравнения, т.е. сравнивая показания индикаторов 18 и 19. Для возобновления работы устройства оператор запускает формирователь 3. Совпадение считанной из блока 30 памяти информа1ош с контрольным тестом соответствует отсутствию неисправности. В этом случае по сигналу синхронизации устанавливается следующий адрес, по которому выполняется контроль (запись контрольного теста и считьгоание) следующей линейки блока 30 памяти на соответствие с установленным контрольным тестом. После проверки по всем адресам, формируемым счетчиком 4, подается команда, по которой устанавливается счетчиком 5 следующий вектор контрольного теста, и проверка возобновляется, начиная с адреса первой линейки блока 30 памяти. По окончании проверки по всем контроль ным тестам и всем адресам, т.е. при заполнении счетчиков 4 и 5, сигналы 1 с выходов счетчика 5 и элемента И 12 поступают на вхо ды элемента И 16, в результате чего сигнал 1 с прямого выхода триггера 8 включает индикатор 20 (Конец контроля) и блокирует генератор 10, прекращая работу устройства в автомати кском режиме. Для работы в полуавтоматическом режиме переключателем 11 счетный вход триггера 6 и вход элемента И 12- подключаются к пшне нулевого потешщала. С помощью устройств вводд информации 23 и 24 оператор устанавливает в счетчиках 4 и 5 соответственно код адреса и вектор контрольного теста, по которым необходимо провести контроль блока 30 памяти. При помощи формирователя 1 подается сигнал, разрешающий считьгоание из блока 30 памяти и сравнение считанной информащш с контрольным кодом при помощи схемы 22 сравнения, как и в автоматическом режиме. Оператор имеет возможность переключить работу устройства с одного режима .на другой на любом этапе контроля. Технике-экономическим преимуществом предлагаемого устройства является более высокая, по сравнению с известным, достоверность контроля. Формула изобретения Устройство для контроля блоков памяти, содержащее генератор синхросигналов, триггеры, счетчики, схему сравнения, элементы И, ИЛИ, индикаторы и элемент задержки, причем счетный вход первого триггера соединен с первым входом первого элемента И, второй вход которого подключен к прямому выходу второго триггера, прямой выход первою триггера соединен спервым входом первого счетчика, выходы которого подключены ко входам первого индикатора, первого элемента ИЛИ и второго элемента И, инверсный выход первого триггера соединен с первым , входом третьего элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к первому входу второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И и управляющим входом схемы сравнения, второй вход четвертого элемента И подключен к выходу второго элемента И, а выход - к единичному входу второго триггера, нулевой вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого подключен к выходу элемента задержки, вход которого соединен с выходом первого элемента И. и первым входом второго счетчика, выходы которого подключены ко входам второго индикатора и одним из входов схемы сравнения, одни из выходов которой соединены со входами третьего, индикатора, выходы первого и второго счетчиков, выход второго элемента ИЛИ и другие входы схемы сравнения являются соответственно адресными, ннформационlUiiMH и управляющим выходалщ и входами устройства, отличающееся тем, что, с целью повышения достоверности контроля, оно содержит формирователи одиночных CHFHajroB, третий и четвертый триггеры, четвертыи элемент ИЛИ, пятый элемент И, блоки ввода информации-и переключатель, причем выход первого формирователя одиночных сигшлов подключен. ко второму входу второго элемента ИЛИ, единичный вход третьего триггера соединен с выходом пятого элемента И, один из входов которого подключен к первому входу, а другие входы - к выходам второго счетда.ка, нулевой вход третьего триггера соединен с выходом второго формирователя одиношых сигналов, со вторыми входами счетчиков и третьего элемента ИЛИ, установоч ным входом первого триггера и первым входом четвертого элемента ИЛИ, второй вход которого подключен к выходу третьего формирователя одиночных сигналов, а выход - 7-

к нулевому входу четверюго триггера, едикичный вход соединен с другим выходом схемы сравнения, прямые выходы ipeTir его и четвертого триггеров подключены ко входам соответственно четвертого и пятого индикаторов, инверсные выходы - соответственно к первому и второму входам генератора синхросигналов, выход которого соединен с первым входом переключателя, второй вход которого соединен с щиной нулевого потенциала, а выход - со счетным входом первого триггера, выходы первого и второго блоков ввода информации подключены соответственно к третьим входам первого и второго счетчиков.

Источники информации, принятые во внимание при экспертизе

21

Авторы

Даты

1981-12-30—Публикация

1980-04-30—Подача