1

Изобретение относится к автоматике и вычислительной технике.и предназначено для использования в системах контроля сложными технологическими объектами.

Цель изобретения - повышение достоверности контроля.

Повышение достоверности и точности контроля функционирования объекта достигается за счет обеспечения до- пускового контроля параметров объекта в течение времени воздействия на него одного тестового сигнала, обеспечения выборочного контроля параметров объекта в зависимости от тес : тового воздействия и о беспечения

воздействия в зависимости от результатов каждого тестового воздействия и регистрации диагностической информации .

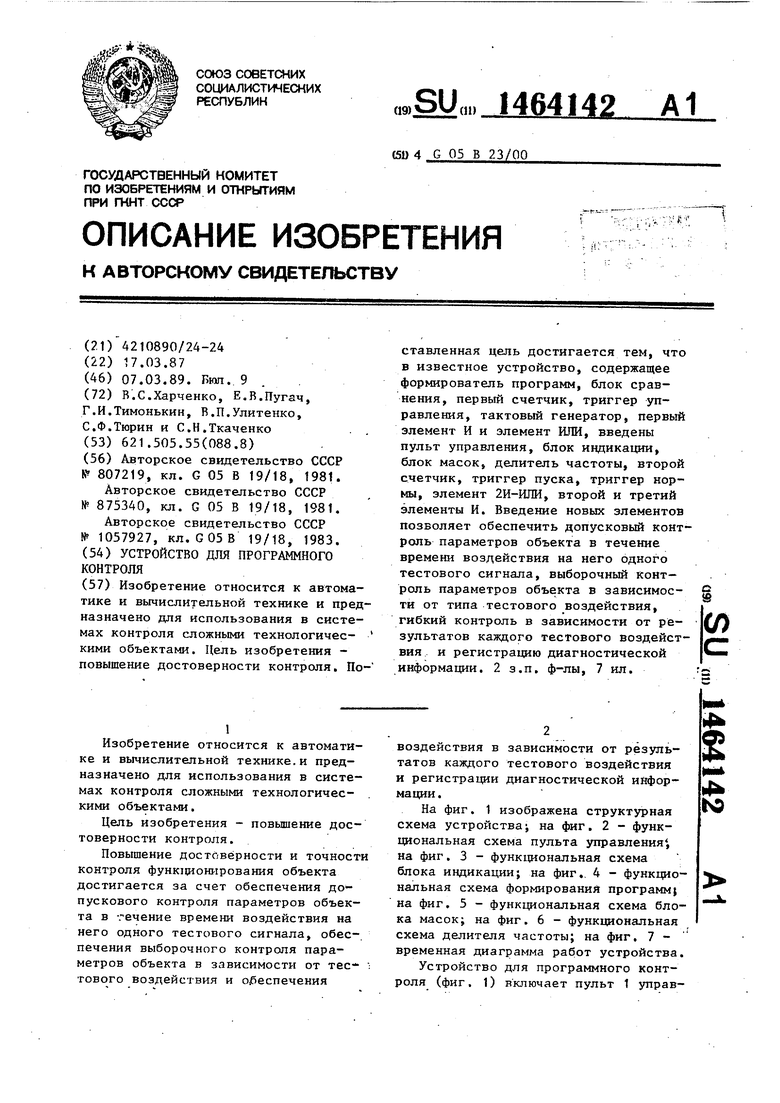

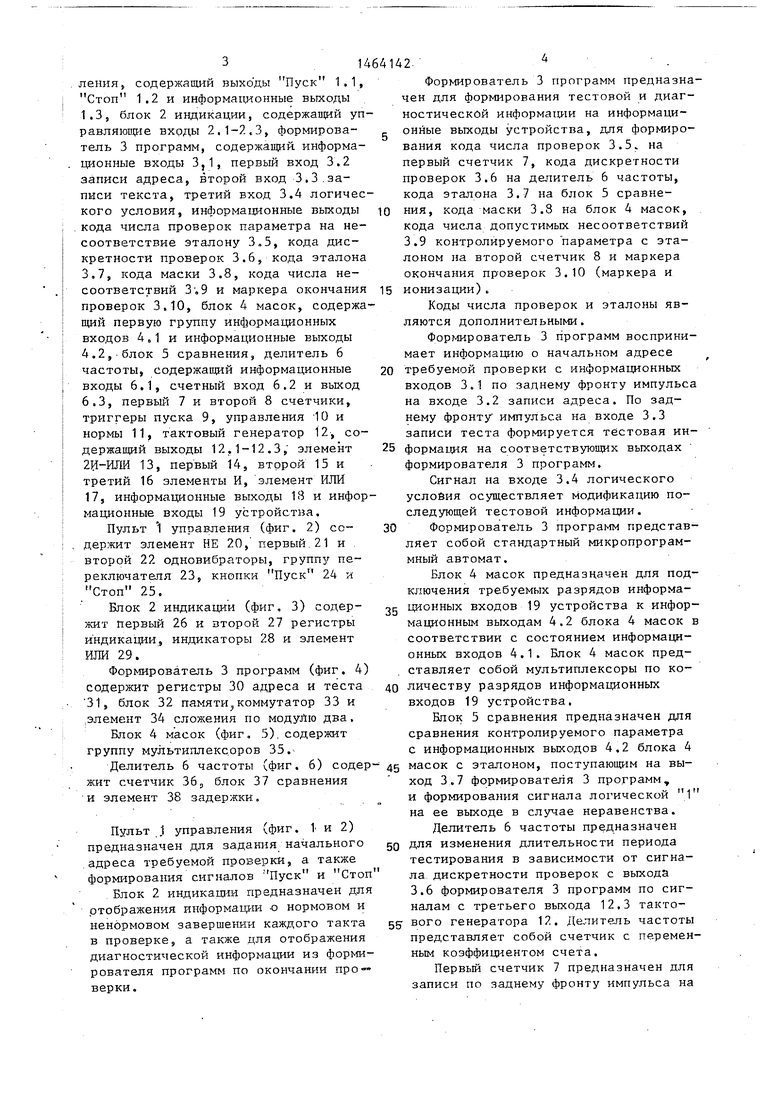

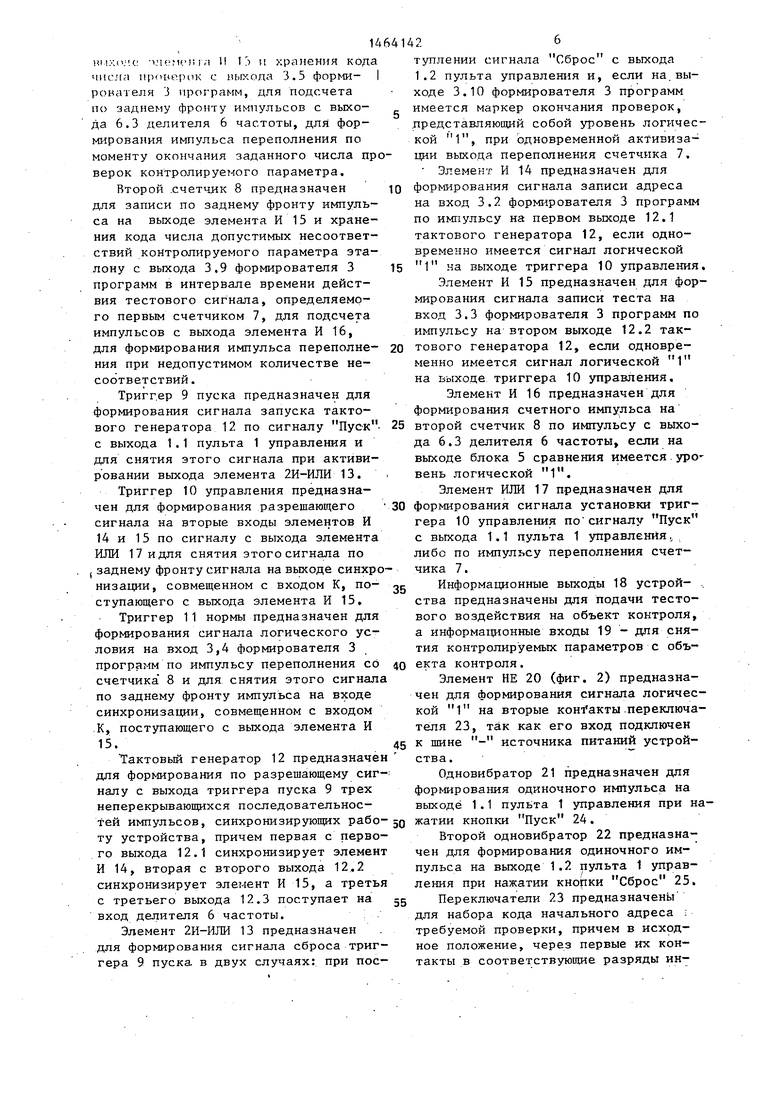

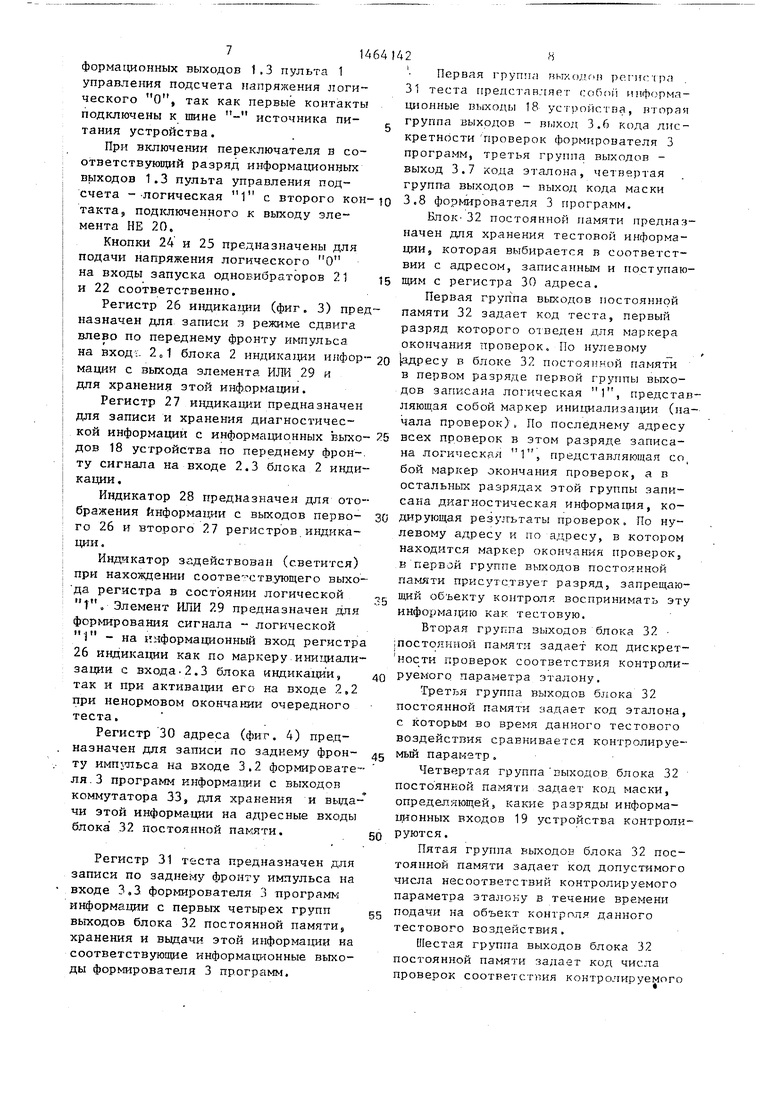

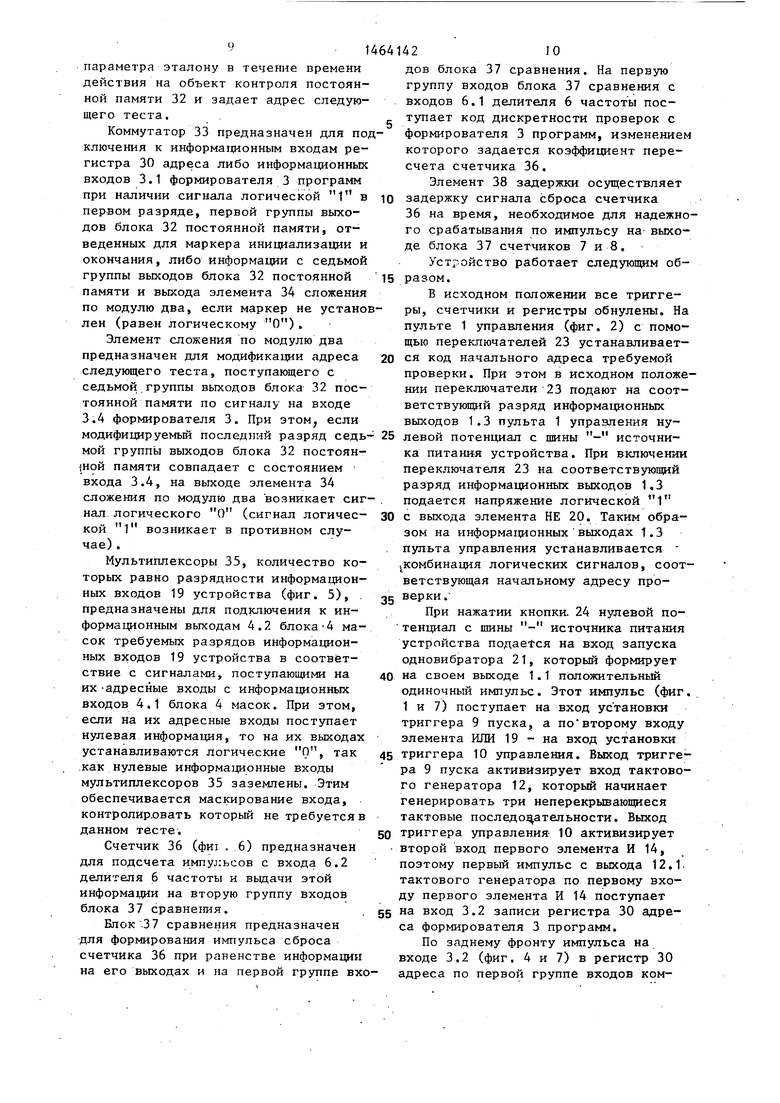

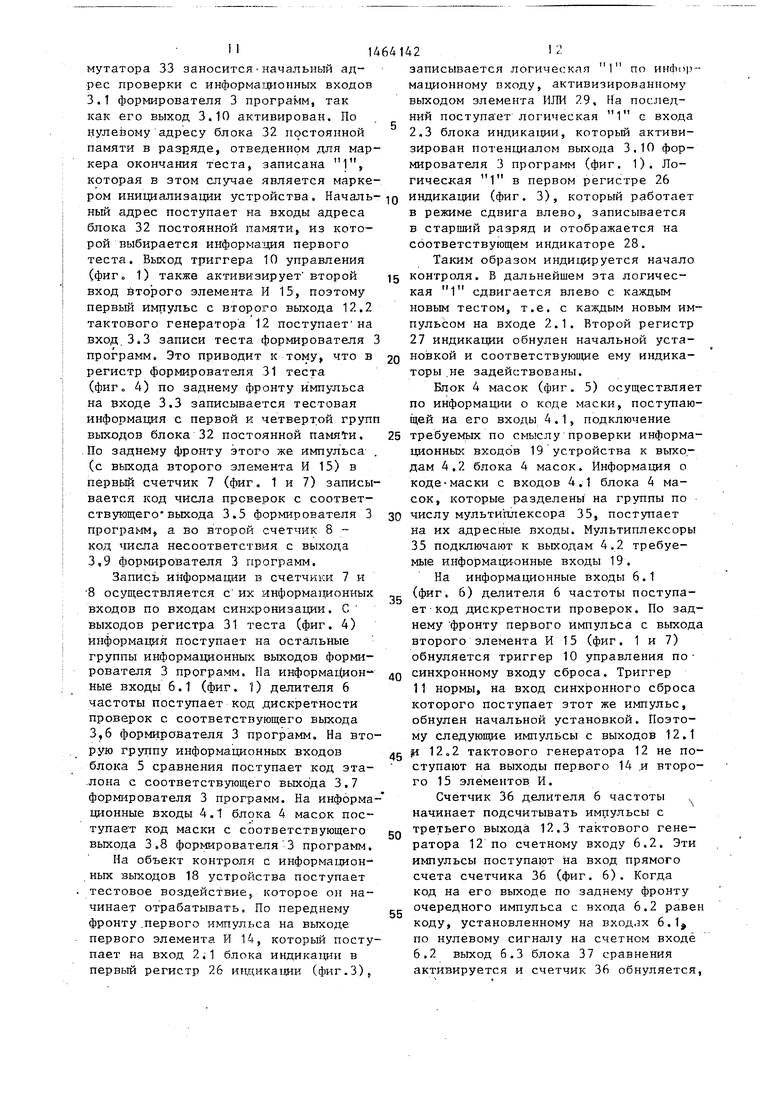

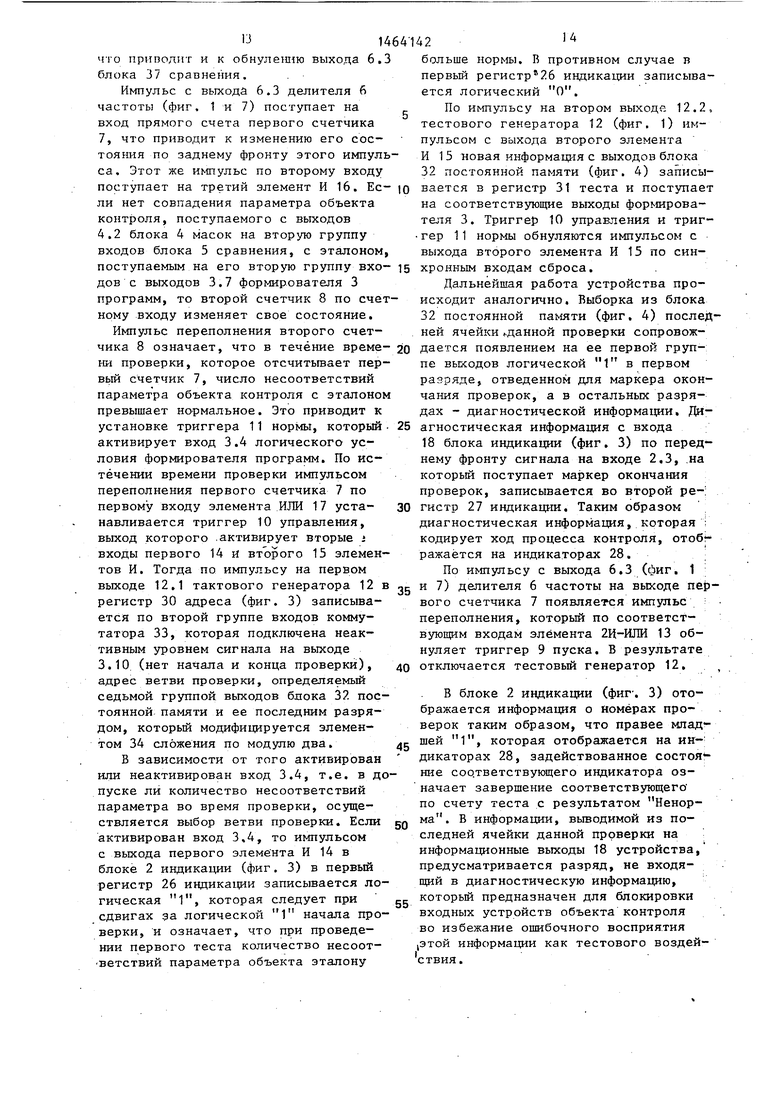

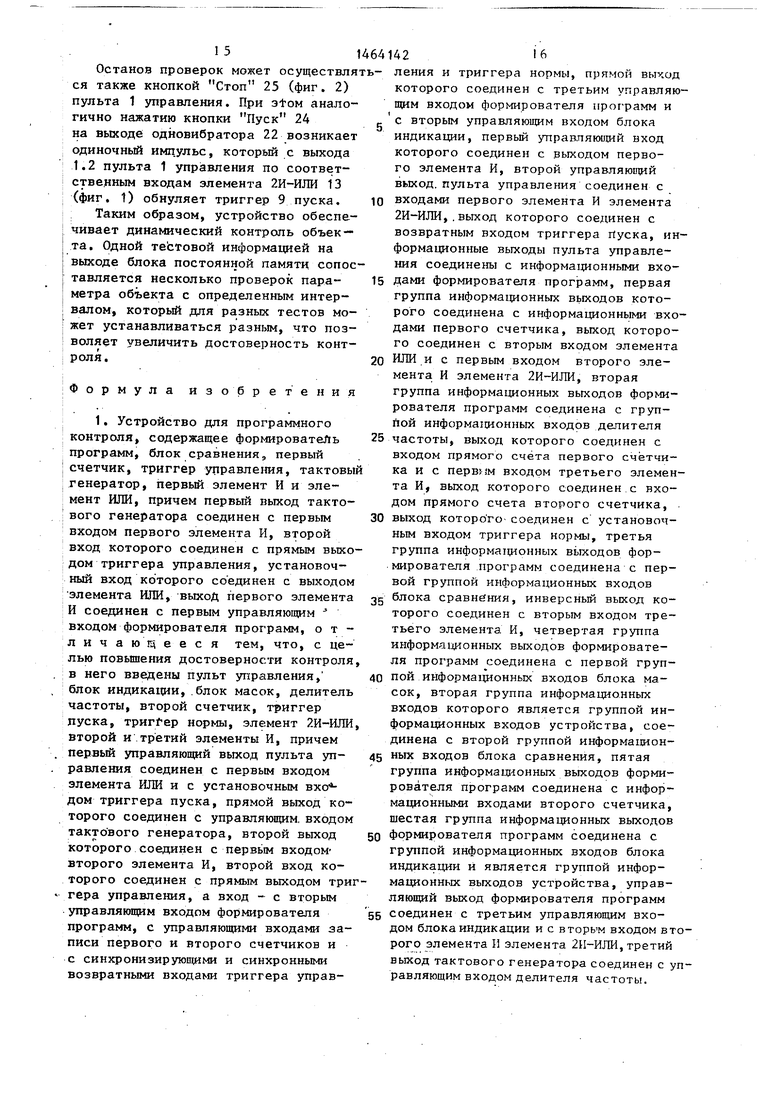

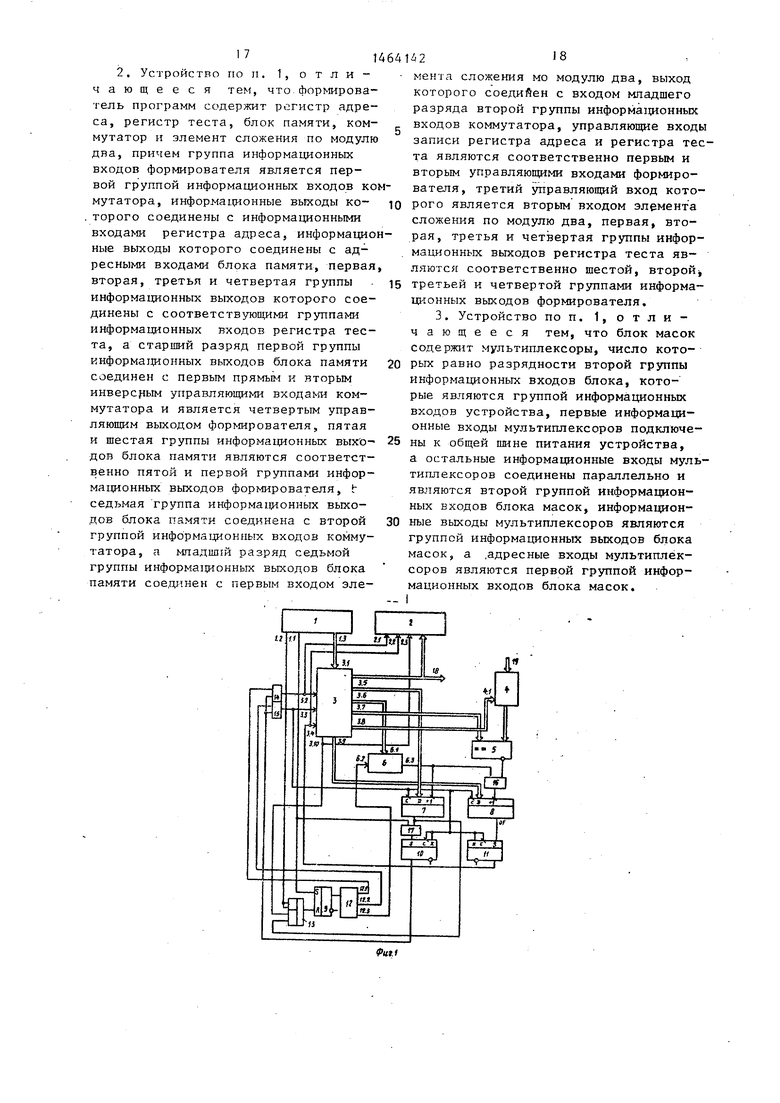

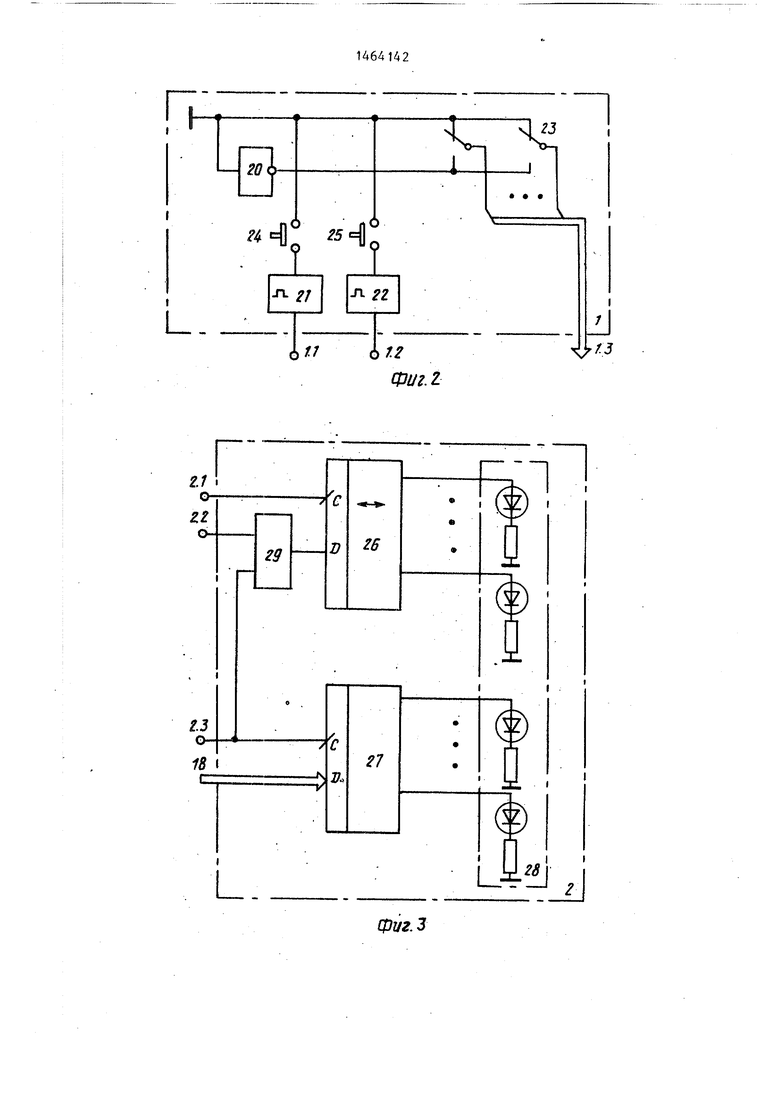

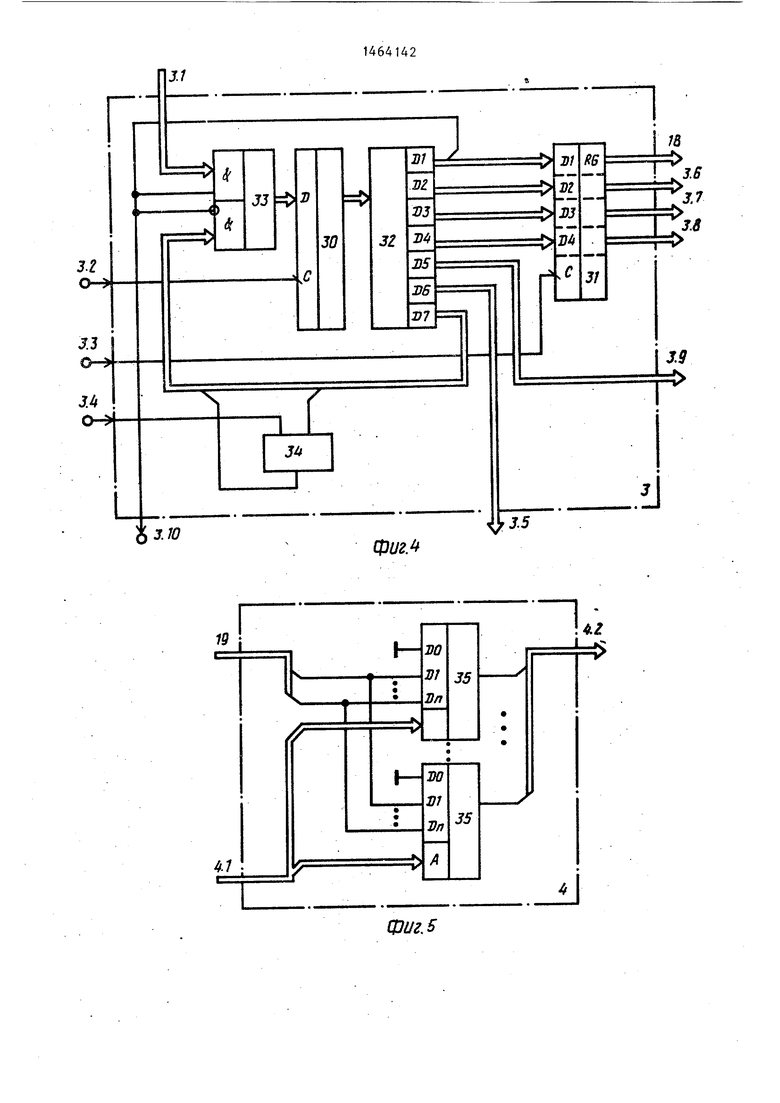

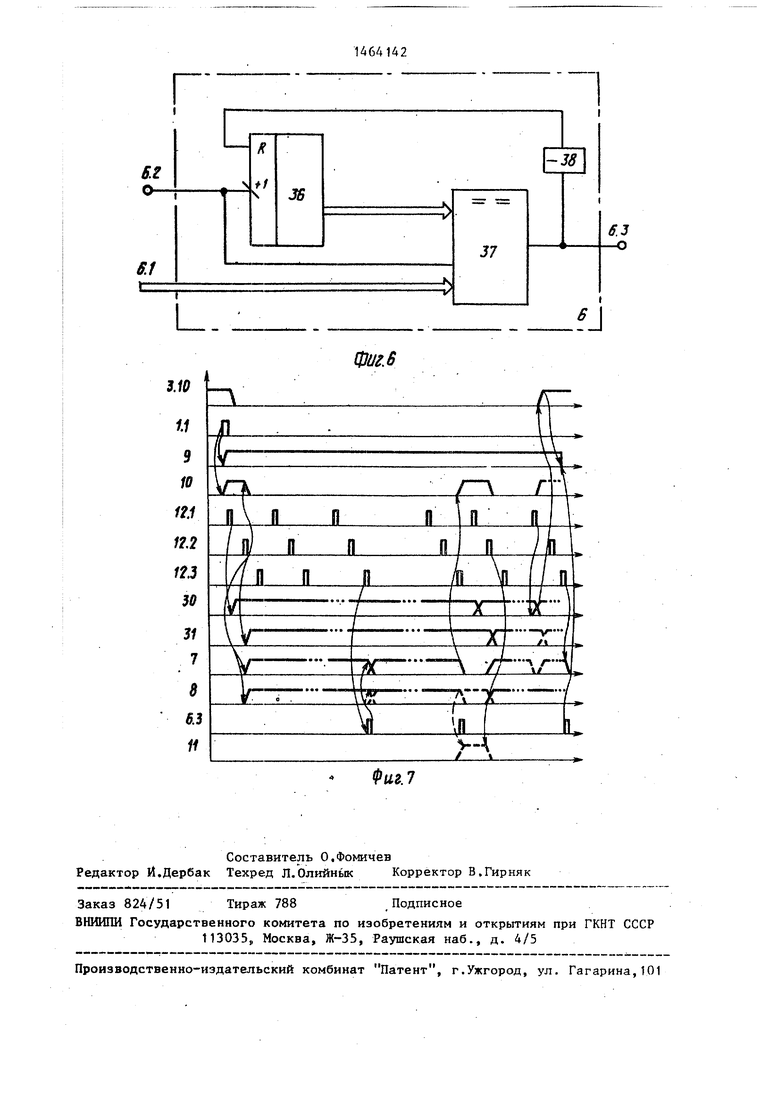

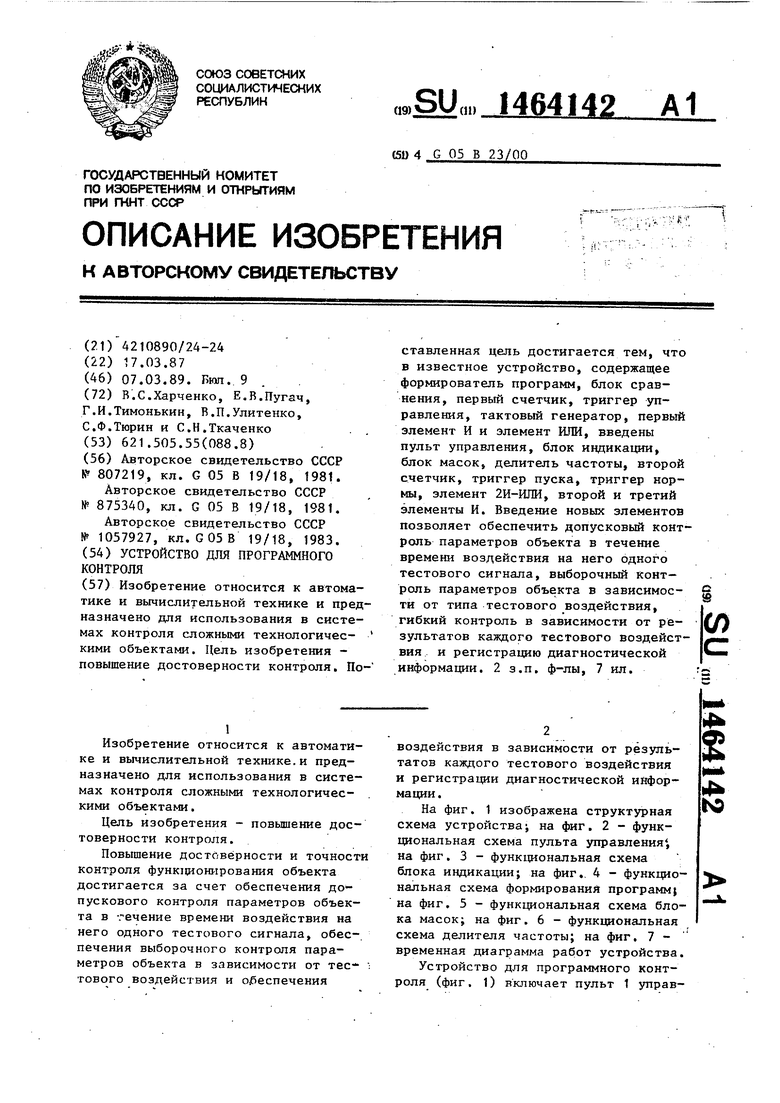

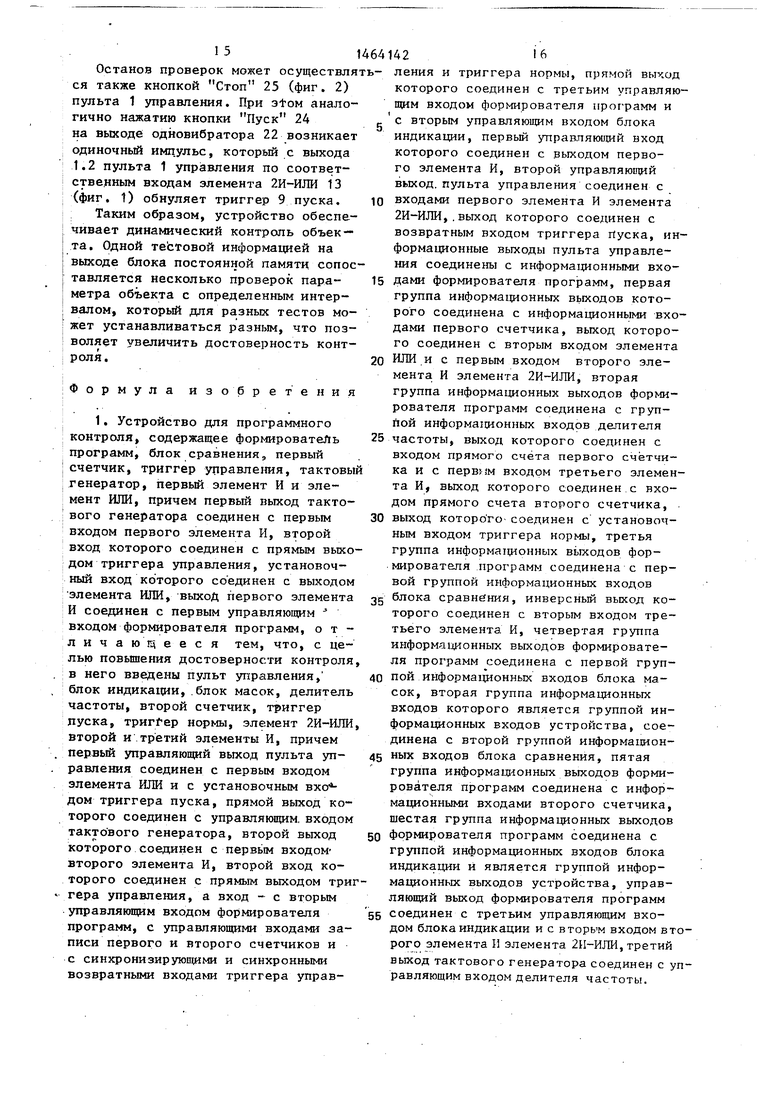

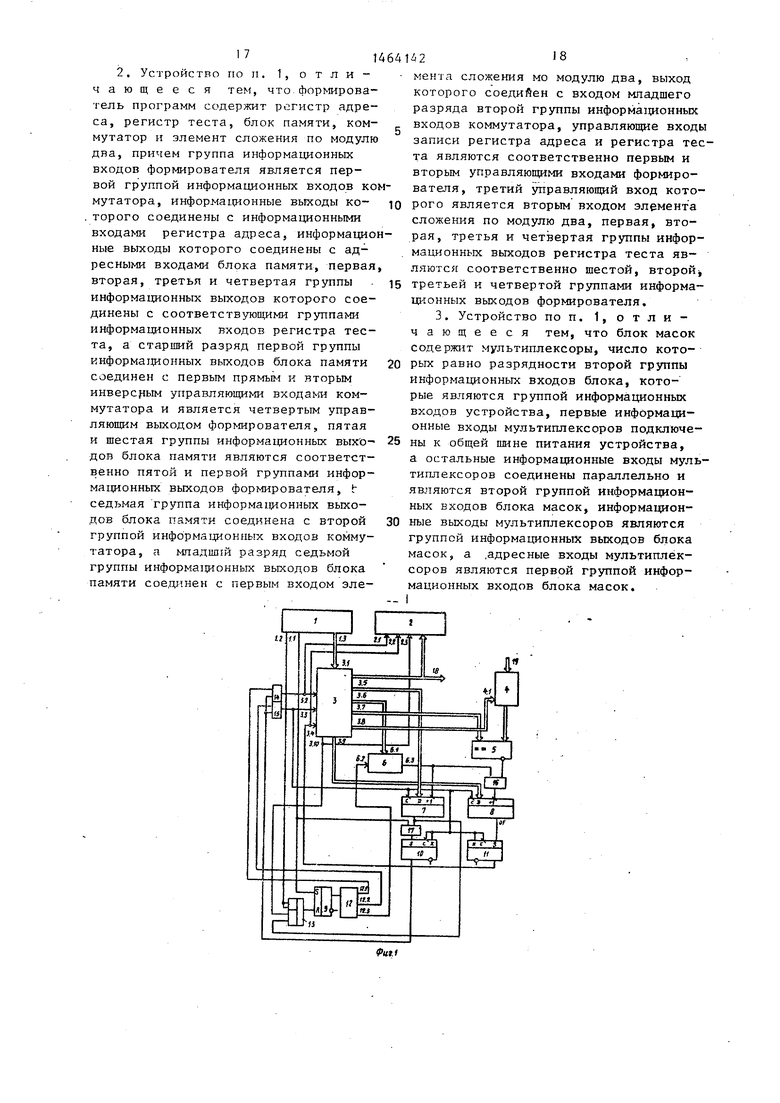

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - функциональная схема пульта управления , на фиг. 3 - функциональная схема блока индикации; на фиг., 4 - функциональная схема формирования программ; на фиг. 5 - функциональная схема блока масок; на фиг. 6 - функциональная схема делителя частоты; на фиг. 7 - временная диаграмма работ устройства.

Устройство для программного контроля (фиг. 1) включает пульт 1 управщ

й1

9

лениЯ), содержащий выходы Пуск ,, Стоп 1.2 и информационные выходы 1.3, езлок 2 индикации, содержащий управляющие входы 2,1-2.3, формирователь 3 программ, содержащий информационные входы 3,1, первый вход 3.2 записи адреса, второй вход 3.3.записи текста, третий вход 3.4 логического условия, информационные выходы .кода числа проверок параметра на несоответствие эталону 3«5, кода дискретности проверок 3.6, кода эталона 3.7, кода маски 3.8, кода числа несоответствий 3,9 и маркера окончания проверок 3,10, блок 4 масок, содержащий первую группу информационных входов 4,1 и информационные выходы 4.2,-блок 5 сравнения, делитель 6 частоты, содержащий информационные входы 6.1, счетный вход 6.2 и выход 6.3, первый 7 и второй 8 счетчики, триггеры пуска 9, управления 10 и нормы 11, тактовый генератор 12, содержащий выходы 12.1-12.3, элемент 2И-ИЛИ 13, первый 14, второй 15 и третий 16 элементы И, элемент ИЛИ 17, информационные выходы 1В и информационные входы 19 устройства.

Пульт 1 управления (фиг. 2) содержит элемент НЕ 20, первый, 21 и второй 22 одновибраторы, группу переключателя 23, кнопки Пуск 24 и Стоп 25.

Блок 2 индикации (фиг, 3) содержит первый 26 и второй 27 регистры и ндикации, индикаторы 28 и элемент ИЛИ 29.

Формирователь 3 программ (фиг. 4) содержит регистры 30 адреса и теста 31, блок 32 памяти коммутатор 33 и .элемент 34 сложения по модулю два.

Блок 4 масок (фиг, 5). содержит группу мультиплексоров 35.

Формирователь 3 программ предназначен для формирования тестовой и диагностической информатщи на информаци.. онные вьпсоды устройства, для формиро- 5

вания кода числа проверок J.b.. на

первый счетчик 7, кода дискретности проверок 3.6 на делитель 6 частоты, кода эталона 3.7 на блок 5 сравне 10 ния, кода маски 3.8 на блок 4 масок, кода числа допустимых несоответствий 3.9 контролируемого параметра с эталоном на второй счетчик 8 и маркера окончания проверок 3.10 (маркера и 15 ионизации).

Коды числа проверок и эталоны являются дополнительными.

Формирователь 3 программ воспринимает информацию о начальном адресе 20 требуемой проверки с информационных входов 3.1 по заднему фронту импульса на входе 3.2 записи адреса. По заднему фронту импульса на входе 3.3 записи теста формируется тестовая ин- 25 формация на соответствующих выходах формирователя 3 программ.

Сигнал на входе 3.4 логического услойия осуществляет модификацию последующей тестовой информации.

Формирователь 3 программ представляет собой стандартный микропрограммный автомат.

Блок 4 масок предназначен для подключения требуемых разрядов информационных входов 19 устройства к инфор- мациоиньм выходам 4.2 блока 4 масок в соответствии с состоянием информационных входов 4.1. Блок 4 масок представляет собой мультиплексоры по ко- 40 личеству разрядов информационных входов 19 устройства.

Блок 5 сравнения предназначен для сравнения контролируемого параметра с информационных выходов 4.2 блока 4

30

35

Делитель 6 частоты (фиг. 6) содер- 45 масок с эталоном, поступающим на выход 3.7 формирователя 3 программ, и формирования сигнала логической 1 на ее выходе в случае неравенства. Делитель 6 частоты предназначен

жит счетчик 36J блок 37 сравнения и элемент 38 задержки:.

Пульт ..1 управления (фиг. и 2) предназначен для задания начального .адреса требуемой проверки, а также формирования сигналов Пуск и Стоп

Блок 2 индикации предназначен для отображения информации о нормовом и ненормовом завершении каждого такта в проверке, а также для отображения диагностической информации из формирователя программ по окончании про- верки.

Формирователь 3 программ предназначен для формирования тестовой и диагностической информатщи на информационные вьпсоды устройства, для формиро-

вания кода числа проверок J.b.. на

первый счетчик 7, кода дискретности проверок 3.6 на делитель 6 частоты, кода эталона 3.7 на блок 5 сравне ния, кода маски 3.8 на блок 4 масок, кода числа допустимых несоответствий 3.9 контролируемого параметра с эталоном на второй счетчик 8 и маркера окончания проверок 3.10 (маркера и 5 ионизации).

Коды числа проверок и эталоны являются дополнительными.

Формирователь 3 программ воспринимает информацию о начальном адресе 0 требуемой проверки с информационных входов 3.1 по заднему фронту импульса на входе 3.2 записи адреса. По заднему фронту импульса на входе 3.3 записи теста формируется тестовая ин- 5 формация на соответствующих выходах формирователя 3 программ.

Сигнал на входе 3.4 логического услойия осуществляет модификацию последующей тестовой информации.

Формирователь 3 программ представляет собой стандартный микропрограммный автомат.

Блок 4 масок предназначен для подключения требуемых разрядов информационных входов 19 устройства к инфор- мациоиньм выходам 4.2 блока 4 масок в соответствии с состоянием информационных входов 4.1. Блок 4 масок представляет собой мультиплексоры по ко- 40 личеству разрядов информационных входов 19 устройства.

Блок 5 сравнения предназначен для сравнения контролируемого параметра с информационных выходов 4.2 блока 4

0

35

масок с эталоном, поступающим на выход 3.7 формирователя 3 программ, и формирования сигнала логической 1 на ее выходе в случае неравенства. Делитель 6 частоты предназначен

для изменения длительности периода тестирования в зависимости от сигнала дискретности проверок с выхода 3.6 формирователя 3 программ по сигналам с третьего выхода 12.3 тактового генератора 12. Делитель частоты представляет собой счетчик с переменным коэффициентом счета.

Первьм счетчик 7 предназначен для записи по заднему фронту импульса на

Hiixivu; -ijicrttMii; II 13 и хранения кода числа прпиерчк с нькода 3.5 форми- I ронателя 3 программ, для подсчета по заднему фронту импульсов с выхода 6.3 делителя 6 частоты, для формирования импульса переполнения по моменту окончания заданного числа прверок контролируемого параметра.

Второй счетчик 8 предназначен для записи по заднему фронту импульса на выходе элемента И 15 и хранения кода числа допустимых несоответствий контролируемого параметра эталону с выхода 3,9 формирователя 3 программ в интервале времени действия тестового сигнала, определяемого первым счетчиком 7, для подсчета импульсов с выхода элемента И 16, для формирования импульса переполнения при недопустимом количестве несоответствий.

Триггер 9 пуска предназначен для формирования сигнала запуска тактового генератора 12 по сигналу Пуск с выхода 1.1 пульта 1 управления и для снятия этого сигнала при активировании выхода элемента 2И-ИЛИ 13,

Триггер 10 управления предназначен для формирования разрешающего сигнала на вторые входы элементов И 14 и 15 по сигналу с выхода элемента ИЛИ 17 и для снятия этого сигнала по , заднему фронту сигнала на выходе синхронизации, совмещенном с входом К, по- ступающего с выхода элемента И 15,

Триггер 11 нормы предназначен для формирования сигнала логического условия на вход 3,4 формирователя 3 программ по импульсу переполнения со счетчика 8 и для снятия этого сигнал по заднему фронту импульса на входе синхронизации, совмещенном с входом ,К, поступающего с выхода элемента И 15.

Тактовый генератор 12 предназначе для формирования по разрешающему сиг налу с выхода триггера пуска 9 трех

Одновибратор 21 предназначен для формирования одиночного импульса на выходе 1.1 пульта 1 управления при на

неперекрывающихся последовательностей импульсов, синхронизирующих рабо-50 жатии кнопки Пуск 24, ту устройства, причем первая с перво- Второй одновибратор 22 предназна- го выхода 12.1 синхронизирует элемент И 14, вторая с второго выхода 12,2 синхронизирует элемент И 15, а третья с третьего выхода 12.3 поступает на jg вход делителя 6 частоты. :

Элемент 2И-ИЛИ 13 предназначен для формирования сигнала сброса триггера 9 пуска в двух случаях: при пос-

чен для формирования одиночного импульса на выходе 1.2 пульта 1 управления при нажатии кнопки Сброс 25.

Переключатели 23 предназначены для набора кода начального адреса ; требуемой проверки, причем в исходное положение, через первые их контакты в соответствующие разряды ин-

туплении сигнала Сброс с выхода 1.2 пульта управления и, если на.выходе 3,10 формирователя 3 программ имеется маркер окончания проверок, .представляющий собой уровень логической 1, при одновременной активиза5

0

g

40 45

5

ции выхода переполнения счетчика 7.

Элемент И 14 предназначен для 0 формирования сигнала записи адреса на вход 3.2 формирователя 3 программ по импульсу на первом выходе 12,1 тактового генератора 12, если одновременно имеется сигнал логической 1 на выходе триггера 10 управления.

Элемент И 15 предназначен для формирования сигнала записи теста на вход 3.3 формирователя 3 программ по импульсу на втором выходе 12,2 тактового генератора 12, если одновременно имеется сигнал логической 1 на выходе триггера 10 управления. Элемент И 16 предназначен для формирования счетного импу;льса на второй счетчик 8 по импульсу с выхода 6,3 делителя 6 частоты, если на выходе блока 5 сравнения имеется уро вень логической 1.

Элемент ИЛИ 17 предназначен для формирования сигнала установки триггера 10 управления по сигналу Пуск с выхода 1,1 пульта 1 управления,, либо по импульсу переполнения счетчика 7,

Информационные выходы 18 устрой- , ства предназначены для подачи тестового воздействия на объект контроля, а йнформахщонные входы 19 - для снятия контролируемых параметров с объекта контроля.

Элемент НЕ 20 (фиг, 2) предназначен для формирования сигнала логической 1 на вторые контакты .переключателя 23, так как его вход подключен к шине - источника питаний устройства.

Одновибратор 21 предназначен для формирования одиночного импульса на выходе 1.1 пульта 1 управления при на30

50 жатии кнопки Пуск 24, Второй одновибратор 22 предназна- jg

жатии кнопки Пуск 24, Второй одновибратор 22 предназна-

чен для формирования одиночного импульса на выходе 1.2 пульта 1 управления при нажатии кнопки Сброс 25.

Переключатели 23 предназначены для набора кода начального адреса ; требуемой проверки, причем в исходное положение, через первые их контакты в соответствующие разряды ин-

71

формавдонных выходов 1.3 пульта 1 управления подсчета напряжения логического О, так как первые контакты подключены к шине - источника питания устройства.

При включении переключателя в соответствующий разряд информаодонных выходов 1.3 пульта управления подсчета --логическая 1 с второго кон такта, под1шюченного к выходу элемента НЕ 20.

Кнопки 24 и 25 предназначены для подачи напряжения логического О на входы запуска одновибраторов 21 и 22 соответственно.

Регистр 26 ивдикащти (фиг. 3) предназначен для. записи 3 режиме сдвига влево по переднему фронту импульса на вход-;. 2.1 блока 2 индикадии инфор- мации с выхода элемента ИЛИ 29 и для хранения этой информации.

Регистр 27 индикадют предназначен для записи и хранения диагностической информации с информационных Ьыхо- дов 18 устройства по переднему фрон-. ту сигнала на входе 2.3 блока 2 индикации .

Индикатор 28 предназначен для отображения йнформа1у{и с выходов перво- го 26 и второго 27 регистров.индикаЩ-П1,

Индикатор задействован (светится) при нахождении соотве :тв.ующего выхо- да Р гистра в состоянии логической Т. Элемент ИЛИ 29 предназначен для формирования сигнала - логической

i - на информационньй вход регистра 26 индикации как по маркеру иннщгали- задии с входа.2.3 блока индикации, так и при активации его на входе 2,2 при ненормовом окончании очередного теста.

Регистр 30 адреса (фиг. 4) предназначен для записи по заднему фрон- ту имп -льса на входе 3.2 формировате- ля.З программ информации с выходов коммутатора 33, для хранения и выда- чи этой информации на адресные входы

блока 32 постоянной памяти.

Регистр 31 теста предназначен для записи по заднему фронту импульса на входе 3,3 формирователя 3 пpoгpaм J информации с первых четырех групп выходов блока 32 постоянной памяти, хранения и вццачи этой информации на соответствующие информационные выходы формирователя 3 программ.

142Н

Первая груплсч ныходон релчтспр;) 31 теста ггреястлнллет (:o6;iii ииф(,фма- ционные вькоды 18 устройства, пторап группа выходов - выход 3.6 кода лис- кретности проверок формирователя 3 программ, третья группа выходов - выход 3.7 кода эталона, четвертая групп-а выходов - выход кода маски 3.8 формирователя 3 программ.

Блок-32 постоянной памяти предназначен для хранения тестовой информации, которая выбирается в соответствии с адресом, записанным и поступающим с регистра 30 адреса.

Первая груп па выходов постоянной памяти 32 задает код теста, первый разряд которого О1веден для маркера окончания проверок. По нулевому адресу в блоке 32 постоянной памят и в первом разряде первой группы выходов записана логическая , предсталяющая собой маркер инициализа 1и (начала проверок). По последнему адресу всех проверок в этом разряде записана лох-нческая 1, представляющая со

бой маркер окончания проверок, а в остальных разрядах этой группы записана диагностическая информация, кодирующая резу. гьтаты проверок. По нулевому адресу и по адресу, в котором находится маркер окончания проверок, в первой группе выходов постоянной памяти присутствует разряд, запрещающий объекту контроля воспринимать эту информагщю как тестовую.

Вторая группа выходов блока 32 - |постояниой памяти задает код дискрет- проверок соответствия контролируемого параметра эталону.

Третья группа выходов блока 32 постоянной памяти задает код эталона, с которым во время данного тестового воздействия сравнивается контролируемый параметр.

Четвертая группа ззых од он блока 32 постоянной памяти задает код маски, определяющей, какие разряды информационных входов 19 устройства контролируются .

Пятая группа выходов блока 32 постоянной памяти задает код допустимого числа несоответствий контролируемого параметра эталону в течение времени подачи на объект контроля данного тестового воздействия.

Шестая группа выходов блока 32 постоянной памяти задает код числа проверок соответст пия контролируемого

у

параметра эталону в течение времени действия на объект контроля постоянной памяти 32 и задает адрес следующего теста.

Коммутатор 33 предназначен для поключения к информационным входам регистра 30 адреса либо информационных входов 3.1 формирователя 3 программ при наличии сигнала логической 1 в первом разряде, первой группы выходов блока 32 постоянной памяти, отведенных для маркера инициализации и окончания, либо информации с седьмой группы выходов блока 32 постоянной памяти и выхода элемента 34 сложения по модулю два, если маркер не устанолен (равен логическому О).

Элемент сложения по модулю два предназначен для модификации адреса следующего теста, поступающего с седьмой. группы вьпсодов блока 32 постоянной памяти по сигналу на входе 3.4 формирователя 3. При этом, если модифицируемый последний разряд седь мой группы выходов блока 32 постоян- |ной памяти совпадает с состоянием входа 3.4, на выходе элемента 34 сложения по модулю два возникает сигнал логического О (сигнал логичес- кой 1 возникает в противном случае) .

Мультиплексоры 35, количество которых равно разрядности информационных входов 19 устройства (фиг. 5), . предназначены для подключения к информационным выходам 4.2 блока 4 масок требуемых разрядов информационных входов 19 устройства в соответствие с сигналами, поступающими на их-адресные входы с информахщонных входов 4.1 блока 4 масок. При этом, если на их адресные входы поступает нулевая информация, то на их выходах устанавливаются логические П, так .как нулевые информационные входы мультиплексоров 35 заземлены. Этим обеспечивается маскирование входа, контролировать который не требуется в данном тесте.

Счетчик 36 (фи1.6) предназначен для подсчета импульсов с входа 6.2 делителя 6 частоты и вьщачи этой информации на вторую группу входов блока 37 сравнения.

Блок .37 сравнения предназначен для формирования импульса сброса счетчика 36 при равенстве информации на его выходах и на первой группе вхо

s

0 5 О

д 0

5

14210

дов блока 37 сравнения. На первую группу входов блока 37 сравнения с входов 6.1 делителя 6 частоты поступает код дискретности проверок с формирователя 3 программ, изменением которого задается коэффициент пересчета счетчика 36.

Элемент 38 задержки осуществляет задержку сигнала сброса счетчика 36 на время, необходимое для надежного срабатывания по импульсу на выходе блока 37 счетчиков 7 и 8.

Устройство работает следующим образом.

В исходном положении все триггеры, счетчики и регистры обнулены. На пульте 1 управления (фиг. 2) с помощью переключателей 23 устанавливается код начального адреса требуемой проверки. При этом в исходном положении переключатели 23 подают на соответствующий разряд информационных выходов 1.3 пульта 1 управления нулевой потенциал с шины - источника питания устройства. При включении переключателя 23 на соответствующий разряд информационных выходов 1.3 подается напряжение логической 1 с выхода элемента НЕ 20. Таким образом на информационных выходах 1.3 пульта управления устанавливается комбинация логических сигналов, соответствующая начальному адресу проверки .

При нажатии кнопки. 24 нулевой по- тенциал с шины - источника питания устройства пoдaetcя на вход запуска одновибратора 21, который формирует на своем выходе 1.1 положительный одиночный импульс. Этот импульс (фиг., 1 и 7) поступает на вход установки триггера 9 пуска, а по второму входу элемента ИЛИ 19 - на вход установки триггера 10 управления. Выход триггера 9 пуска активизирует вход тактового генератора 12, который начинает генерировать три неперекрывающиеся тактовые последо ательности. Выход триггера управления- 10 активизирует второй вход первого элемента И 14, поэтому первый импульс с выхода 12.1. тактового генератора по первому входу первого элемента И 14 поступает на вход 3.2 записи регистра 30 адреса формирователя 3 программ.

По заднему фронту импульса на входе 3.2 (фиг. 4 и 7) в регистр 30 адреса по первой группе входов коммутатора 33 заноситсяначальный адрес проверки с информащюнных входов 3,1 формирователя 3 программ, так как его выход 3,10 активирован. По нулевому адресу блока 32 ностоянной памяти в разряде, отведенном для маркера окончания теста, записана 1,

записывается логическая 1 по информационному входу, активизированному вькодом элемента HJIli 29, FJa последний поступает логическая 1 с входа 2.3 блока индикахщй, который активизирован потенциалом выхода 3,10 формирователя 3 программ (фиг, 1), Ло

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для программного регулирования | 1986 |

|

SU1437833A2 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для тестового диагностирования | 1984 |

|

SU1213481A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах контроля сложными технологичес- кими объектами. Цель изобретения - повышение достоверности контроля. Поставленная цель достигается тем, что в известное устройство, содержащее формирователь программ, блок сравнения, первый счетчик, триггер управления, тактовый генератор, первый элемент И и элемент ИЛИ, введены пульт управления, блок индикации, блок масок, делитель частоты, второй счетчик, триггер пуска, триггер нормы, элемент 2И-ШШ, второй и третий элементы И. Введение новых элементов позволяет обеспечить допусковый контроль параметров объекта в течение времени воздействия на него одного тестового сигнала, выборочный контроль параметров объекта в зависимости от типа тестового воздействия, гибкий контроль в зависимости от результатов каждого тестового воздействия и регистрацию диагностической информации. 2 з.п. ф-лы, 7 ил. (Л

крторая в этом случае является марке- гическая 1 в первом регистре 26 ром инициализации устройства. Началь-ig индикации (фиг, 3), который работает

ныи адрес поступает на входы адреса блока 32 постоянной памяти, из которой выбирается информа; дия первого теста. Выход триггера 10 управления (фиго 1) также активизирует второй вход второго элемента И 15, поэтому первый импульс с второго выхода 12.2 тактового генератора 12 поступает на вход. 3,3 записи теста формирователя 3 программ. Это приводит к тому, что в регистр формирователя 31 теста (фиг„ 4) по заднему фронту импульса на входе 3,3 записывается тестовая информация с первой и четверт.ой групп выходов блока 32 постоянной памя1 и, По заднему фронту этого же импульса (с выхода второго элемента И 15) в первый счетчик 7 (фиг, 1 и 7) записывается код числа проверок с соответствующего выхода 3,5 формирователя 3 программ, а во второй счетчик 8 код числа несоответствия с выхода 3,9 формирователя 3 программ.

Запись информации в счетчики 7 и 8 осуществляется с их информакщонных входов по входам синхронизации, С выходов регистра 31 теста (фиг, 4) информация поступает на остальные группы информационных выходов формирователя 3 программ. На информаи(ион- ныб входы б,1 (фиг, 1) делителя 6 частоты поступает код дискретности проверок с соответствующего выхода формирователя 3 программ. На вторую группу информационных входов блока 5 сравнения поступает код эта- .лона с соответствующего выхода 3,7 формирователя 3 программ. На информационные входы 4,1 блока 4 масок поступает код маски с соответствующего выхода 3,8 формирователя 3 программ.

На объект контроля с информагдион- ных выходов 18 устройства поступает тестовое воздействие, которое он начинает отрабатывать. По переднему фронту .первого импульса на выходе первого элемента И 14, который поступает на вход 2,1 блока индика1и и в первый регистр 26 ивдикации (фиг.З),

в режиме сдвига влево, записывается в старший разряд и отображается на соответствующем индикаторе 28,

TajCHM образом индицируется начало контроля, В дальнейшем эта логическая 1 сдвигается влево с каждым новьм тестом, т,е, с каждым новым импульсом на входе 2,1, Второй регистр 27 индикации обнулен начальной установкой и соответствуюи(ие ему индикаторы .не задействованы,

Епок 4 масок (фиг, 5) осуществляет по информации о коде маски, поступающей на его входы 4,1, подключение

требуемых по смыслу проверки информационных входов 19 устройства к выхо.- дам 4,2 блока 4 масок. Информация о коде-маски с входов 4,1 блока 4 масок, которые разделены на группы по числу мульти плексора 35, поступает на их адресные входы. Мультиплексоры 35 подключают к выходам 4,2 требуемые информаци-онные входы 19,

На информационные входы 6,1 (фиг. 6) делителя 6 частоты поступает код дискретности проверок. По заднему фронту первого импульса с выхода второго элемента И 15 (фиг, 1 и 7) обнуляется триггер 10 управления по синхронному входу сброса. Триггер 11 нормы, на вход синхронного сброса которого поступает этот же импульс, обнулен начальной установкой. Поэтому следующие импульсы с выходов 12,1

|и 12„2 тактового генератора 12 не поступают на выходы первого 14 .и второго 15 элементов И,

Счетчик 36 делителя 6 частоты начинает подсчитывать импульсы с третьего выхода 12,3 тактового генератора 12 по счетному входу 6,2, Эти импульсы поступают на вход прямого счета счетчика 36 (фиг, 6), Когда код на его выходе по заднему фронту очередного импульса с входа 6,2 равен коду, установленному на вход.зх 6,1 по нулевому сигналу на счетном входе 6,2 выход 6,3 блока 37 сравнения активируется и счетчик 36 обнуляется.

что приводит и к обнулет5ю выхода 6.3 блока 37 сравнения. .

Импульс с вькода 6.3 делителя 6 частоты (фиг, 1 и 7) поступает на вход прямого счета первого счетчика 7, что приводит к изменению его состояния по заднему фронту этого импульса. Этот же импульс по второму входу

поступает на третий элемент И 16, Ее- ю вается в регистр 31 теста и поступает

ли нет совпадения параметра объекта контроля, поступаемого с выходов 4,2 блока 4 масок на вторую группу входов блока 5 сравнения, с эталоном, поступаемым на его вторую группу вхо- 15 хронным входам сброса. дов с выходов 3,7 формирователя 3 Дальнейшая работа устройства про- программ, то второй счетчик 8 по счетному входу изменяет свое состояние.

Импульс переполнения второго счетчика 8 означает, что в течение време- 20 дается появлением на ее первой групна соответствующие выходы фор шрова- теля 3, Триггер 10 управления и триг гер 11 нормы обнуляются импульсом с выхода второго элемента И 15 по синисходит аналогично. Выборка из блока 32 постоянной памяти (фиг. 4) послей ней ячейки дaннoй проверки сопровож

Ю1 проверки, которое отсчитьшает пер- вьш счетчик 7, число несоответствий параметра объекта контроля с эталоном превышает нормальное. Это приводит к установке триггера 11 нормы, который активирует вход 3.4 логического условия формирователя программ. По истечении времени проверки импульсом переполнения первого счетчика 7 по первому входу элемента ИЛИ 17 устанавливается триггер 10 управления, выход которого .активирует вторые i входы первого 14 и второго 15 элементов И, Тогда по импульсу на первом выходе 12.1 тактового генератора 12 в регистр 30 адреса (фиг, 3) записывается по второй группе входов коммутатора 33, которая подключена неактивным уровнем сигнала на выходе 3.10 (нет начала и конца проверки), адрес ветви проверки, определяемый седьмой группой выходов блока 3. постоянной памяти и ее последним разрядом, который модифицируется элементом 34 сложения по модулю два.

Б зависимости от того активирован или неактивирован вход 3.4, т.е. в допуске ли количество несоответствий параметра во время проверки, осуществляется выбор ветви проверки. Если активирован вход 3,4, то импульсом с выхода первого элеме нта И 14 в блоке 2 индикации (фиг, 3) в первый регистр 26 индикации записывается , которая следует при

начала проверки, и означает, что при проведении первого теста количество несоответствий параметра объекта эталону

гическая

сдвигах за логической 1

больше нормы, В противном случае в первый регистр 26 индикации записывается логический О,

По импульсу на втором выходе 12,2, тестового генератора 12 (фиг, 1) импульсом с выхода второго элемента И 15 новая информация с выходов блока 32 постоянной памяти (фиг, 4) записыхронным входам сброса. Дальнейшая работа устройства про-

на соответствующие выходы фор шрова- теля 3, Триггер 10 управления и триггер 11 нормы обнуляются импульсом с выхода второго элемента И 15 по синхронным входам сброса. Дальнейшая работа устройства про-

дается появлением на ее первой груписходит аналогично. Выборка из блока 32 постоянной памяти (фиг. 4) послей ней ячейки дaннoй проверки сопровож

пе вькодов логической 1 в первом разряде, отведенном для маркера окончания проверок, а в остальных разрядах - диагностической информации, Дяагностическая информация с входа ; 18 блока индикации (фиг, 3) по переднему фронту сигнала на входе 2.3, .на который поступает маркер окончания проверок, записывается во второй ре-:

гистр 27 индикации. Таким образок диагностическая информация, которая ; кодирует ход процесса контроля, отобг ражаётся на индикаторах 28.

По импульсу с выхода 6.3 (фиг. 1 и 7) делителя 6 частоты на выходе первого счетчика 7 появляется импульс : переполнения, который по соответствующим входам элемента 2И-ИЛИ 13 обнуляет триггер 9 пуска. В результате отключается тестовый генератор 12.

В блоке 2 индикащи (фиг . 3) отображается информация о номерах проверок таким образом, что правее мпад- шей 1, которая отображается на ин- дикаторах 28, задействованное состояние соо.тветствующего индикатора означает завершение соответствующего по счету теста с результатом Ненорма, В информации, выводимой из последней ячейки данной проверки на информационные выходы 18 устройства, предусматривается разряд, не входящий в диагностическую информацию, который предназначен для блокировки входных устройств объекта контроля во избежание ошибочного восприятия

|Этой информации как тестового воздей ствия.

5 5

Останов проверок может осуществляся также кнопкой Стоп 25 (фиг. 2) пульта 1 управления. При эфом аналогично нажатию кнопки Пуск 24 на выходе одновибратора 22 возникает одиночный импульс, который с выхода 1.2 пульта 1 управления по соответственным входам элемента 2И-ИЛИ 13 (фиг. 1) обнуляет триггер 9 пуска.

Таким образом, устройство обеспечивает динамический контроль объекта. Одной тестовой информацией на выходе блока постоянной памяти сопос I тавляется несколько проверок пара- I метра объекта с определенным интер- ; валом, который для разных тестов мо- I жет устанавливаться разным, что поз- воляет увеличить достоверность контроля.

:Формула изобретения

счетчик, триггер управления, тактовы генератор, первый элемент И и элемент ИЛИ, причем первый выход такто: вого генератора соединен с первым

входом первого элемента И, второй вход которого соединен с прямым выходом триггера управления, установочный вход которого соединен с выходом элемента ИЛИ, выход первого элемента И соединен с первым управляющим входом формирователя программ, отличающееся тем, что, с целью повьшения достоверности контроля в него введены пульт управления,

блок индикации,.блок масок, делитель частоты, второй счетчик, триггер пуска, триггер нормы, элемент 2И-ШШ второй и.третий элементы И, причем первый управляющий выход пульта уп- равления соединен с первым входом элемента ИЛИ и с установочным дом триггера пуска, прямой выход которого соединен с управляннцим, входом тактового генератора, второй выход которого соединен с первьм входом- второго элемента И, второй вход которого соединен с прямым выходом триггера управления, а вход - с вторым управляющим входом формирователя

программ, с управляющими входами записи первого и второго счетчиков и с синхронизируюпщми и синхронными возвратными входами триггера управ14216

ления и триггера нормы, прямой выход которого соединен с третьим управляющим входом формирователя программ и с вторым управляюишм входом блока индикации, первый управляюиий вход которого соединен с выходом первого элемента И, второй управляюп1Ий выход, пульта управления соединен с входами первого элемента И элемента 2И-ИЛИ,.выход которого соединен с возвратным входом триггера Пуска, информационные выходы пульта управления соединены с информат ионными входами формирователя программ, первая группа информационных вькодов которого соединена с информационными входами первого счетчика, выход которого соединен с вторым входом элемента ИЛИ и с первым входом второго элемента. И элемента 2И-ИЛИ, вторая группа информационных выходов формирователя программ соединена с группой информационных входов делителя частоты, выход которого соединен с входом прямого счёта первого счетчика и с nepBJSM входом третьего элемента И, выход которого соединен с входом прямого счета второго счетчика, выход которого соединен с установочным входом триггера нормы, третья группа информатщонных вькодов формирователя программ соединена с первой группой информационных входов блока сравнения, инверсный выход которого соединен с вторым входом третьего элемента И, четвертая группа информационных выходов формирователя программ соединена с первой группой информахщонных входов блока масок, вторая группа информационных входов которого является группой информационных входов устройства, соединена с второй группой информационных входов блока сравнения, пятая группа информационных выходов формирователя программ соединена с информационными входами второго счетчика, шестая группа информационных выходов формирователя программ соединена с группой информационных входов блока индикации и является группой информационных выходов устройства, управляющий выход формирователя программ соединен с третьим управляющим входом блок а индикации и с вторым входом втрого элемента И элемента 2И-ИЛИ, третий выход тактового генератора соединен с уравляющим входом делителя частоты.

Фиг, 3

фиг.5

Г

П

фиг. 6

| Устройство для программногоупРАВлЕНия Об'ЕКТАМи | 1978 |

|

SU807219A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для програмного управления | 1979 |

|

SU875340A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-03-07—Публикация

1987-03-17—Подача