(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1552174A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

. 1

Изобретение относится к вычислительной технике и предназнано для деления многоразрядных чисел в р-кодах Фибоначчи.

Известно устройство для деления, содержащее регистр делимого, регистр делителя, схему сравнения, генератор тактовых импульсов,, сумматор, и осуществляющее деление многоразрядных двоичных чисел 1 .

Известно также устройство для деления двоичных чисел, содержащее регистр делимого, регистр делителя, регистр частного и параллельный сумматор 2 ..

Недостатком таких устройств для деления является невозможность деления чисел представленных в р-кодах Фибоначчи.

Наиболее близким к предлагаемому является устройство для деления, содержащее регистр делителя, преобразователь прямого кода в обратный, регистр делимого и регистр частного, сумматор, первый выход которого соединен со входом блока управления, первый вход сумматора соединен с выходом регистра делимого, управляющие входы регистра делителя, преобразователя прямого кода в обратный,

регистра делимого, регистра частного .

и сумматора соединены с oooTBeTCTByra щими выходами блока управления,вы-

ход регистра частного является выS ходом устройства, первый вход регист. ра делимого является первым входом устройства, вход регистра делителя является вторым входом устройства, выход регистра делителя соединен со 0 входом преобразователя прямого кода в обратный 3.

Недостатком этого устройства для деления является невозможность деления чисел, представленных в р-кодах 15 Фибоначчи, .

Дель изобретения - расширения ,функциональных возможностей устройства.

Данная цель достигается тем, что 20 устройство йля деления дополнительно содержит генератор последовательности обобщенных чисел Фибоначчи и регистр Остатка, выход которого соединен со вторым входом регистра делимого, а вход соединен со вторым выходом сумматора, второй вход сумматора соединен о выходом генератора последовательности обобщенных чисел Фибоначчи, вход которого соеди30 ней с выходом преобразователя прямо744564

го кода в обратный, управляющие входы генератора последовательности обобщенных чисел Фибоначчи и регистра остатка соединены с соответствующими выходами блока управления.

При делении чисел в р-кодах Фибоначчи образуют последовательность обобщенных чисел Фибоначчи. Начальное число последовательности с номером нуль соответствует нулевому разряду р-кода Фибоначчи частного и является делителем, а i-e число последовательности, соответствующее i-му разряду р-кода Фибоначчи частного, образуется путем сложения в р-коде Фибоначчи (i-l)-ro и (i-p-l)-ro чисел последовательности обобщенных чисел Фибоначчи. Числа последовательно сравнивают вр-к6дах Фибоначчи

с делимым до тех пор, пока не опредепится -ое число, которое является . первым .числом в полученной последовательности б|Ольшим делимого. После этого в- (Е-1)-й разряд р-кода Фибоначчи частного записывают единицу, а (В-1)-ое число последовательности обобщенных чисел Фибоначчи вычитают в р-коде Фибоначчи из делимого. Полученный остаток сравнивают в р-коде Фибоначчи с числами полученной пЬследовательности и выделяют т-ое число последовательности, которое являет.ся наименьшим числом последовательности, большим чем остаток. После чего в (т-1)-й разряд р-кода фибона чи частного записывают единицу, а (m-i)-oe число образованной последовательности вычитают в р-коде Фибоначчи из предыдущего остатка, получая при этом очередной остаток. Пррцесс сравнения чисел последовательности с остатком й вычйТанйёповТо- 1

. .гтУ-г- --. - . --

ряют до тех пор,.пока остаток не станет меньше делителя. При этом контролируют, чтобы в р-коде Фибоначчи частного в каждой группе из (р+1) подряд идущих разрядов кода встречалось не более одной единицы. Нарушение этого условия является признаком неправильного выполнения операции деления.

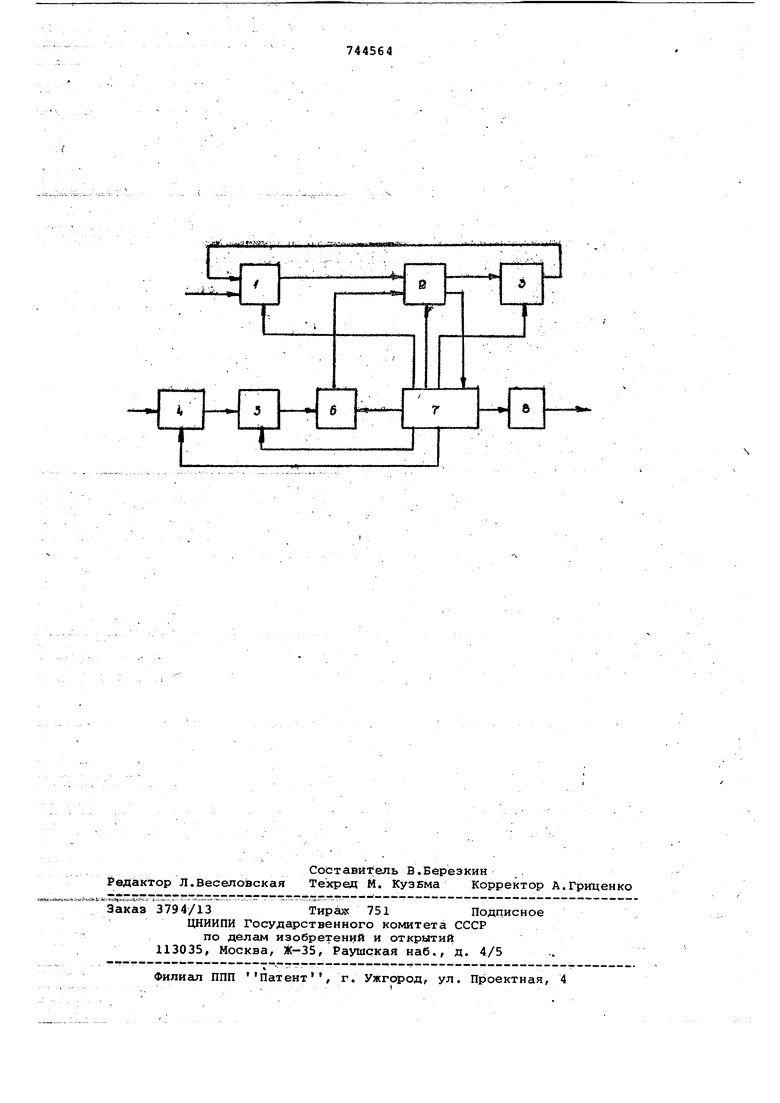

На чертеже изображена влок-схема устройства для деления.

Устройство ддя деления содержит регистр 1 делимого, предназначенный для хранения р-кода Фибоначчи дели Мого; сумматор 2, осуществляющий сложение р-кодрв Фибоначчи поступающих на его входы; регистр 3 остатка, в котором хранится р-код Фибоначчи разности делимого (остатка) и числа из последовательности обобщенных чисел Фибоначчи; регистр 4 делителя, предназначенный для хранения р-кода Фи боначШ дели т ел я; пр ёобраэ 6в ат ель 5 прямого кода в обратный, осуществляющий лреобразобание прямого p-Kojnta Фибоначчи делителя в обратный р-код Фибоначчи, который является исходным

кодом последовательности кодов формируемой генератором 6 последовательности обобщенных чисел Фибоначчи, блок 7 управления; регистр 8 частного, в котором формируется результат деления в р-коде Фибоначчи. Первый выход сумматора 2, являющийся выходом переноса старшего разряда, соединен со входом блока 7 управления. Первый вход регистра 1 делимого является первым входом сумматора, а вход регистра 4 делителя является вторым входом устройства, выход регистра 8 частного является выходом устройства..

Устройство для деления работает следующим образом.

Если делимое равно 102, делитель 5, то в исходном состоянии в регистре 1 делимого записывается р-код Фибоначчи числа 102, в регистре 4 делителя - р-код Фибоначчи числа 5; содержимое регистра остатка 3 и регистра частного 8 равно нулю. Нулевое число последовательности обобщенных чисел Фибоначчи, формируемое генератором 6, равно обратному р-коду |Фибоначчи делителя.

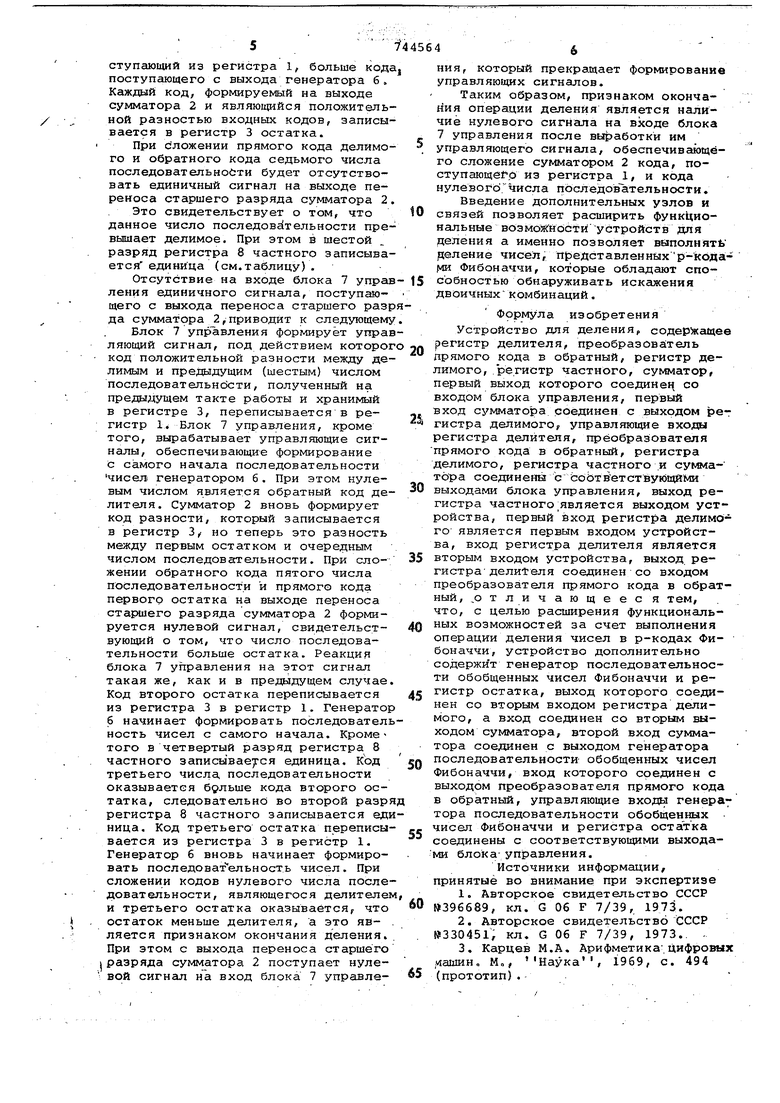

Под действием управляющих сигналов, поступающих из блока 7 управления, генератор 6 начинает формировать обратные р-коды Фибоначчи чисел последовательности, приведенной в таблице.

Код с выхода генератора 6 поступает на второй вход сумматора 2, который осуществляет сложение этого кода с KoijoM делимого. При этом на вход переноса младшего разряда сумматора 2 постоянно подается единица, т.е. сложение выполняется как бы с дополнительным кодом. Если на выходе переноса сдаршего разряда сумматора 2 отсутствует сигнал переноса, то это означает, что код, поступающий из регистра 1, меньше кода, поступеиощего с выхода генерат.ора 6. Если же на выходе переноса старшего разряда сумматора 2 формируется единичный сигнал, то это значит, что код, поступающий из регистра 1, больше кода, поступающего с выхода генератора 6. Каждый код, формируемый на выходе сумматора 2 и являющийся положительной разностью входных кодов, записывается в регистр 3 остатка.

При сложении прямого кода делимого и обратного кода седьмого числа последовательности будет отсутствовать единичный сигнал на выходе переноса старшего разряда сумматора 2.

Это свидетельствует о том, что данное число последовательности превышает делимое. При этом в шестой разряд регистра 8 частного записывается единица (см.таблицу) .

Отсутствие на входе блока 7 управления единичного сигнала, поступающего с выхода переноса старшего разряда сумматора 2, приводит к следующему.

Блок 7 управления формирует управляющий сигнал, под действием которого код положительной разности между делимым и предыдущим (шестым) числом последовательнс)сти, полученный на предыдущем такте работы и хранимый в регистре 3, переписывается в регистр 1j Блок 7 управления, кроме того, вырабатывает управляющие сигналы, обеспечивающие формирование с самого начала последовательности чисел генератором б. При этом нулевым числом является обратный код делителя. Сумматор 2 вновь формирует код разности, который записывается в регистр 3 но теперь это разность между первым остатком и очередным числом последовательности. При сложении обратного кода пятого числа последовательности и прямого кода первого остатка на выходе переноса старшего разряда сумматора 2 формируется нулевой сигнал, свидетельствующий о том, что число последовательности больше остатка. Реакция блока 7 управления на этот сигнал такая же, как и в предыдущем случае. Код второго остатка переписывается из регистра 3 в регистр 1. Генератор 6 начинает формировать последовательность чисел с самого начала. Крометого в четвертый разряд регистра 8 частного записывае гся единица. Код третьего числа, последовательности оказывается больше кода второго остатка, следовательно во второй разряд регистра 8 частного записывается единица. Код третьего остатка переписывается из регистра 3 в регистр 1. Генератор 6 вновь начинает формировать последоват ельность чисел. При сложении кодов нулевого числа последовательности, являющегося делителем, и третьего остатка оказывается, что остаток меньше делителя, а это яв- . ляется признаком окончания деления. . При этом с выхода переноса старшего 1 разряда сумматора 2 поступает нулевой сигнал на вход блока 7 управления, который прекращает формирование управляющих сигналов.

Таким образом, признаком окончания операции деления является наличие нулевого сигнала На входе блока 7 управления после выработки им управляющего сигнала, обеспечивающего сложение сумматором 2 кода, поступающего из регистра 1, и кода нулевого. числа поеледовательности,

Введение дополнительных узлов и

0 связей позволяет расширить функциональные возмоя нсэсти устройств для деления а именно позволяет выполнять деление чисел, представленныхр-кодаfJSK Фибоначчи, которые обладают спо5собностью обнаруживать искажения двоичныхкомбинаций.

Формула изобретения Устройство для деления, содержащее регистр делителя, преобр аз он артель

0 прямого кода в обратный, регистр делимого, регистр частного, сумматор, первый выход которого соединец со входом блока управления, первый вход сумматора соединен с выходом ре5, гистра делимого, управляющие входы регистра делителя, преобразователя прямого кода в обратный, регистра делимого, регистра частного и сумматора соединены с соЬтветствующйми

D выходами блока управления, выход регистра частного,является выходом устройства, первый вход регистра делимого является первым входом устройства, вход регистра делителя является

5 вторым входом устройства, выход регистра делителя соединен со входом преобразователя прямого кода в обратный, ,отличающеес я тем, что, с целью расширения функциональных возможностей за счет выполнения

0 операции деления чисел в р-кодах Фибоначчи, устройство дополнительно содержит генератор последовательности обобщенных чисел Фибоначчи и регистр остатка, выход которого соеди5нен со вторым входом регистра делимого, а вход соединен со вторым выходом сумматора, второй вход сумматора соединен с выходом генератора последовательности обобщенных чисел

O Фибоначчи, вход которого соединен с выходом преобразователя прямого кода в обратный, управляющие входы генера тора последовательности обобщенных чисел Фибоначчи и регистра остатка

5 соединены с соответствующими выходами блока-управления.

Источники информации, принятые во внимание при экспертизе

0 №396689, кл. G 06 F 7/39, 1973.

5 (прототип).

-

Авторы

Даты

1980-06-30—Публикация

1978-03-17—Подача