о а

СП

9д

СА

Изобретение относится к вычислительной технике и. может быть применено при разработке быстродействующих устройств деления, удобных для изготовления в составе больших интегральных схем.

Целью изобретения является расширение области применения устройства за счет обеспечения возможности обработки чисел, представленных дополнительным кодом.

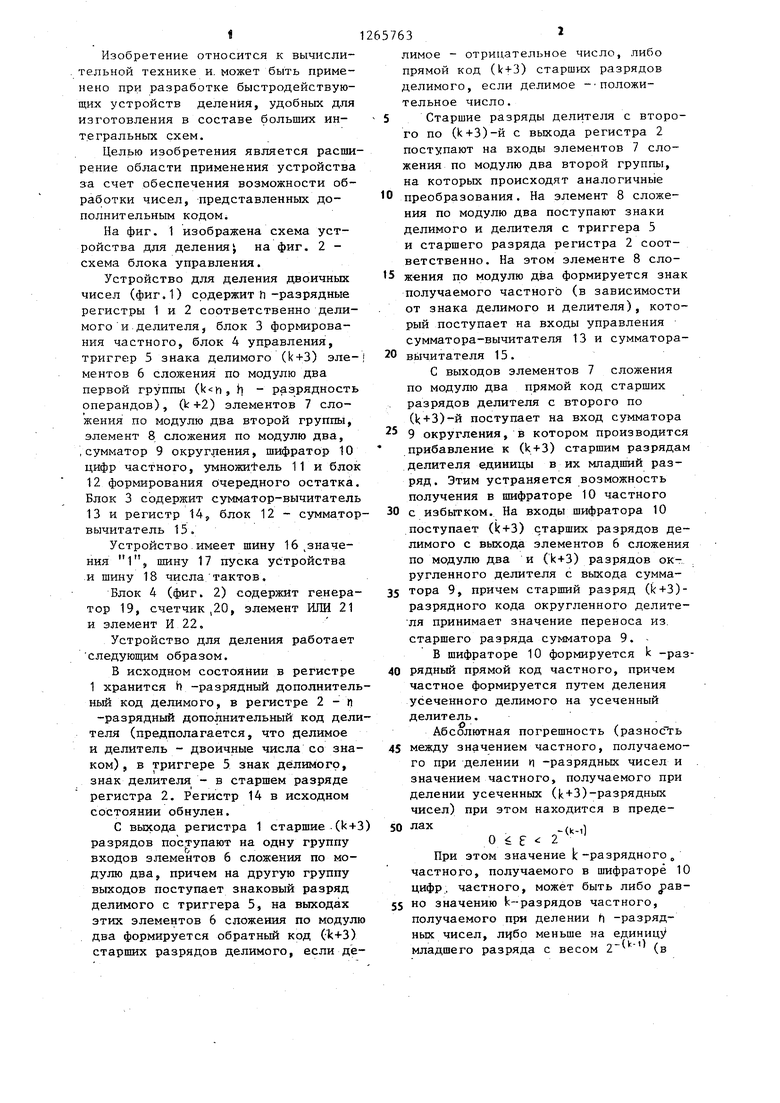

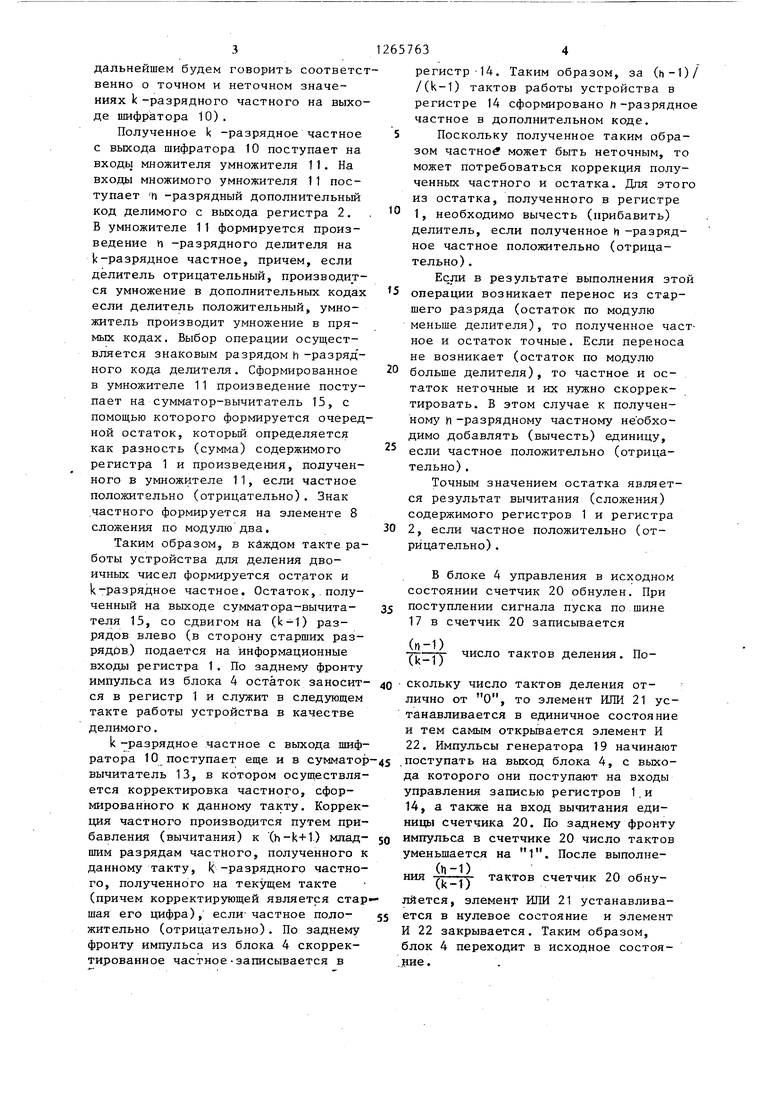

На фиг. 1 изображена схема устройства для деления, на фиг. 2 схема блока управления.

Устройство для деления двоичных чисел (фигИ) содержит П-разрядные регистры 1 и 2 соответственно делимого и делителя, блок 3 формирования частного, блок 4 управления, триггер 5 знака делимого (k+3) элементов 6 сложения по модулю два первой группы (, h - разрядность операндов), () элементов 7 сложения по модулю два второй группы, элемент 8 сложения по модулю два, .сумматор 9 округления, шифратор 10 цифр частного, умножиФель 11 и блок

12формирования очередного остатка. Блок 3 содержит сумматор-вычитатель

13и регистр 14, блок 12 - сумматорвычитатель 15.

Устройство.имеет шину 16 ,значения I, шину 17 пуска устройства и шину 18 числатактов.

Блок 4 (фиг. 2) содержит генератор 19, счетчик ,20, элемент ИЛИ 21 и элемент И 22.

Устройство для деления работает следующим образом.

В исходном состоянии в регистре 1 хранится h -разрядный дополнительный код делимого, в регистре 2 - п

-разрядный дополнительный код делителя (предполагается, что делимое и делитель - двоичные числа со знаком) , в триггере 5 знак делимого, знак делителя - в старшем разряде регистра 2. Регистр 14 в исходном состоянии обнулен.

С выхода регистра 1 старшие .(k+3 разрядов поступают на одну группу входов элементов 6 сложения по модулю два, причем на другую группу выходов поступает знаковый разряд делимого с триггера 5, на выходах этих элементов 6 сложения по модулю два формируется обратный код Ck+S) старших разрядов делимого, если делимое - отрицательное число, либо прямой код (k+3) старших разрядов делимого, если делимое -положительное число.

5 Старшие разряды делителя с второго по (k+3)-и с выхода регистра 2 поступают на входы элементов 7 сложения по модулю два второй группы, на которых происходят аналогичные 0 преобразования. На элемент 8 сложения по модулю два поступают знаки делимого и делителя с триггера 5 и старшего разряда регистра 2 соответственно. На этом элементе 8 сло5 жения по модулю два формируется знак получаемого частного (в зависимости от знака делимого и делителя), который поступает на входы управления сумматора-вычитателя 13 и сумматора20 вЫчитателя 15.

С выходов элементов 7 сложения по модулю два прямой код старших разрядов делителя с второго по (k+3)-и поступает на вход сумматора 25 9 округления, в котором производится прибавление к (k+3) старшим разрядам делителя единицы в их младший разряд. Этим устраняется возможность получения в шифраторе 10 частного 30 с избытком. На входы шифратора 10 поступает (k+3) старших разрядов делимого с выхода элементов 6 сложения по модулю два и (k+3) разрядов округленного делителя с выхода сумма35 тора 9, причем старший разряд (k+3)разрядного кода округленного делителя принимает значение переноса из. старшего разряда сумматора 9. В шифраторе 10 формируется k -раз40 рядный прямой код частного, причем частное формируется путем деления усеченного делимого на усеченный

делитель.

Абсолютная погрешность (разность

между значением частного, получаемого при делении ii -разрядных чисел и значением частного, получаемого при делении усеченных (|с+3)-разрядных чисел) при этом находится в преде50 лах ,

О f : 2

При этом значение 1с-разрядного „ частного, получаемого в шифраторе 10 цифр, частного, может быть либо рав55 но значению k-разрядов частного, получаемого при делении h -разрядных чисел, лчбо меньше на единицу младшего разряда с весом 2 (в дальнейшем будем говорить соответст венно о точном и неточном значениях k-разрядного частного на выходе шифратора 10). Полученное k -разрядное частное с выхода шифратора 10 поступает на входь множителя умножителя 11. На входы множимого умножителя 11 поступает И -разрядный дополнительный код делимого с выхода регистра 2. В умножителе 11 формируется произведение п -разрядного делителя на k-разрядное частное, причем, если делитель отрицательный, производится умножение в дополнительных кодах если делитель положительный, умножитель производит умножение в прямых кодах. Выбор операции осуществляется знаковым разрядом h -разрядного кода делителя. Сформированное в умножителе 11 произведение поступает на сумматор-вычитатель 15, с помощью которого формируется очеред ной остаток, который определяется как разность (сумма) содержимого регистра 1 и произведения, полученного в умножителе 11, если частное положительно (отрицательно). Знак .частного формируется на элементе 8 сложения по модулю два, Таким образом, в кйждом такте работы устройства для деления двоичных чисел формируется остаток и k-разрядное частное. Остаток,.полученный на выходе сумматора-вычитателя 15, со сдвигом на (k-1) разрядов влево (в сторону старших разрядов) подается на информационные входы регистра 1. По заднему фронту импульса из блока 4 остаток заносит ся в регистр 1 и служит в следующем такте работы устройства в качестве делимого. k-разрядное частное с выхода шиф ратора 10 поступает еще и в суммато вычитатель 13, в котором осуществля ется корректировка частного, сформированного к данному такту. Коррек ция частного производится путем при бавления (вычитания) к (h-k+1) млад шим разрядам частного, полученного данному такту, 1 -разрядного частно го, полученного на текущем такте (причем корректирующей является ста шая его цифра), если частное положительно (отрицательно). По заднему фронту импульса из блока 4 скорректированное частное-записывается в 634 регистр-14. Таким образом, за (h-1)/ /(k-1) тактов работы устройства в регистре 14 сформировано rt-разрядное частное в дополнительном коде. Поскольку полученное таким образом частной может быть неточным, то может потребоваться коррекция полученных частного и остатка. Для этого из остатка, полученного в регистре 1, необходимо вычесть (прибавить) делитель, если полученное h -разрядное частное положительно (отрицательно) . Если в результате выполнения зтой операции возникает перенос из старшего разряда (остаток по модулю меньше делителя), то полученное частное и остаток точные. Если переноса не возникает (остаток по модулю больше делителя), то частное и остаток неточные и их нужно скорректировать. В этом случае к полученному h-разрядному частному необходимо добавлять (вычесть) единицу, если частное положительно (отрицательно) . Точным значением остатка является результат вычитания (сложения) содержимого регистров 1 и регистра 2, если частное положительно (отрицательно) . В блоке 4 управления в исходном состоянии счетчик 20 обнулен. При поступлении сигнала пуска по шине 17 в счетчик 20 записывается у .4 число тактов деления. Поскольку число тактов деления отлично от О, то элемент ИЛИ 21 устанавливается в единичное состояние и тем самым открьшается элемент И 22. Импульсы генератора 19 начинают поступать на выход блока 4, с выхода которого они поступают на входы управления записью регистров 1,и 14, а также на вход вычитания единицы счетчика 20. По заднему фронту мпульса в счетчике 20 число тактов уменьшается на 1. После выполнетактов счетчик 20 обнуйется, элемент ИПИ 21 устанавливается в нулевое состояние и элемент 22 закрывается. Таким образом, лок 4 переходит в исходное состояие. Формула изобретения Устройство для.деления, содержащее регистры делимого и делителя, блок управления, сумматор округления, шифратор -цифр частного, блок формирования частного, умножитель, блок формирования очередного остатка j первая группа информационных входов которого соединена с выходами регистра делимого, а вторая.группа информационных входов - с выходами умножителя, информационные входы которого соединены с выходами шифратора цифр частного и регистра делителя, первая группа входов шифратора цифр частного соединена с выходами сумматора округления, вход переноса которого соединен с шиной значения 1 устройства, выходы шифратора циф частного соединены с информационными входами блока формирования частного вход управления сдвигом которого со динен с выходом блока управления и входом управления записью регистра делимого, информационные входы кото рого соединены со сдвигом на k раз. рядов влево ( П - разрядность операндов) с выходами блока формиро вания очередного остатка, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности обрабо ки чисел, представленных дополнительным кодомJ в него йведены две . группы элементов сложения по модулю два, элемент сложения по модулю два и триггер знака делимого, блок формирования частного содержит суммато вычитатель и регистр, а блок форми7636рования очередного остатка - сумматор-вычитатель, информагщонные входы и выходы которого являются информационными входами и выходами блока формирования очередного остатка, а управляющий вход соединен с управляющим входом сумматора-вычитателя блока формирования частного и с выходом элемента сложения по модулю два, первый вход которого соединен с первыми входами элементов сложения по модулю два первой группы и выходом триггера знака делимого, а второй вход - с первыми входами элементов сложения по модулю два второй группы и выходом первого разряда регистра делителя, вторые входы элементов сложения по модулю два первой группы соединены с выходами с первого по (К+3)-й регистра делимого, а выходы - с второй группой входов шифра тора цифр частного,.вторые входы элементов содожения по модулю два второй группы соединены с выходами разрядов с второго по (k+2)-й регистра делителя, а выходы -.с входами разрядов сумматора округления, в блоке формирования частного выходы регистра соединены с информационными входами старших разрядов сумматора -вычитате ля , выходы которого соединены с информационными входами регистра, вход управления записью которого соединен с входом управления сдвигом блока формирования частного информационные входы которого соединены с входами младших разрядов сумматора-вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Изобретение относится к области вычислительной техники. Цель изобретения - расширение области применения за счет обеспечения возможности обработки чисел, представленных дополнительным кодом. Устройство содержит регистры делимого и делителя, сумматор округления, умножитель. шифратор цифр частного, блок формирования частного, содержащий сумматор-вычитатель и регистр, блок управления , триггер знака делимого, две группы элементов сложения по модулю два, элемент сложения по модулю два и блок формирования очередного остатка, содержащий сумматор вычитатель. Сущность изобретения заключается в том, что для обработки операндов в дополнительном коде старшие (k ьЗ) разрядов делимого и делителя инвертируются в случае отрицательных операндов и используются для формирования К .разрядов частi ного, а схемы устройства настраи(Л ваются на определенный режим работы в .зависимости от знаков делимого и делителя. 2 ил.

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1985-06-07—Подача