(54) УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ

ЧИСЛА ИМПУЛЬСОВ В ЦИФРОВОЙ код Изобретение относится к цифровой вычислительной технике и может быть использовано в число-импульсных вычислительных блоках, специализированных цифровых вычислительных машинах и в аналого-цифровых преобразователях. Известно устройство для функционального преобразования, содержащее счетчик текущего значения функции, дешифратор пороговых значений функции, счетчик номера порога, дешифратор номера порога, группу в ентилей блок памяти коэффициентов деления, управляемый делитель частоты, допол нительную группу вентилей и линии задержки 1. Недостатком известного устройств является низкая точность преобразов ния и iero сложность. Наиболее близким техническим реш нием к данному изобретению является устройство для функционального преобразования числа импульсов, содержащее делитель частоты, две группы элементов И, счетчик текущего значе ния функции, выходы которого .соединены со входами дешифратора пороговых значений функции, выход которого соединен со входом-счетчика номера порога, выходы которого соединены со входами дешифратора номера nopiora, первый и второй выходы которого соединены соответственно со входами первого и второго блоков памяти коэффициентов деления 2. Однако такое устройство обладает недостаточной точностью преобразования и аппаратурной сложностью. Целью изобретения является упрощение устройсва и повышение точности работы преобразователя. Это достигается тем, что предлагаемое устройство дополнительно содержит два элемента ИЛИ и блок алгебраического суммирования, первый вход которого является входом устройства, а выход соединен со входом делителя частоты, разрядные выходы которого соединены с сигнальными входами элементов И первой и второй групп, выходы которых через первый и второй элементы ИЛИ соответственно соединены со вторым входом блока алгебраического сложения и входом счетчика текущего значения функции, управляющий и сигнальный входы первого и второго элементов ИЛИ соединены соответственно с управляющими выходами первого и второго блоков памяти коэффициентов деления и первым и вторым сигнальными выходами делителя частоты, разрядные выходы первого и второго блоков памяти коэффициентов деления соединены соответственно со вторыми входами элементов ИЛИ первой и второй групп.

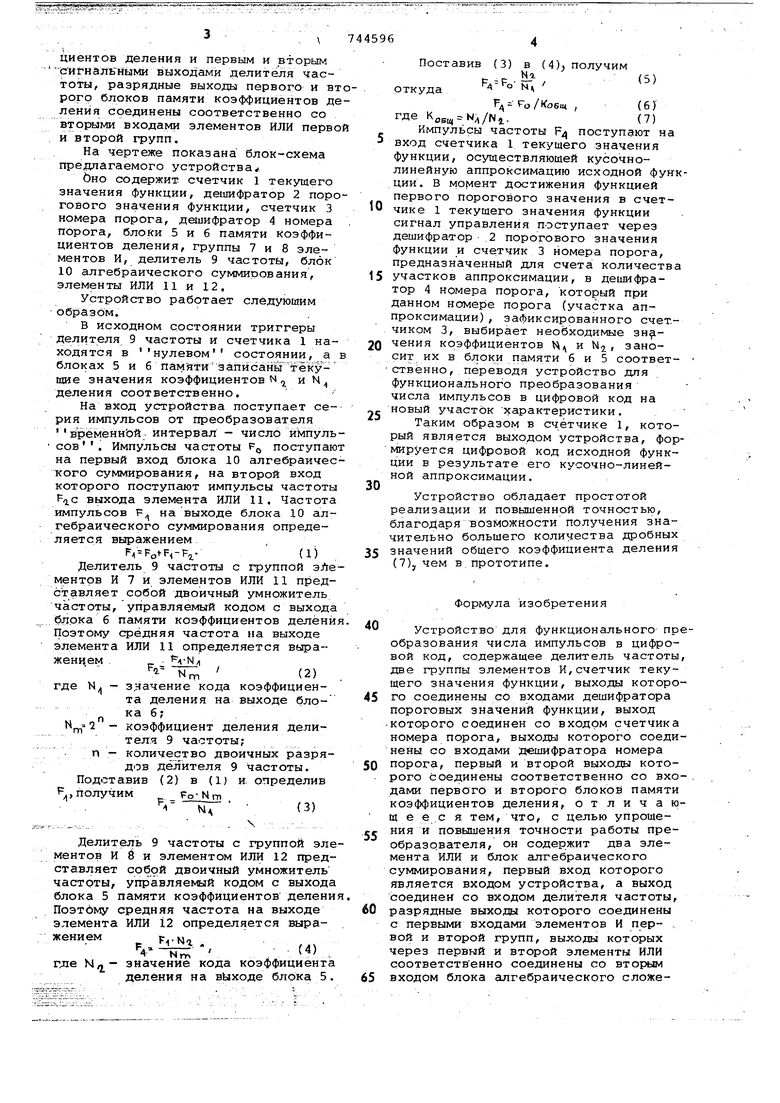

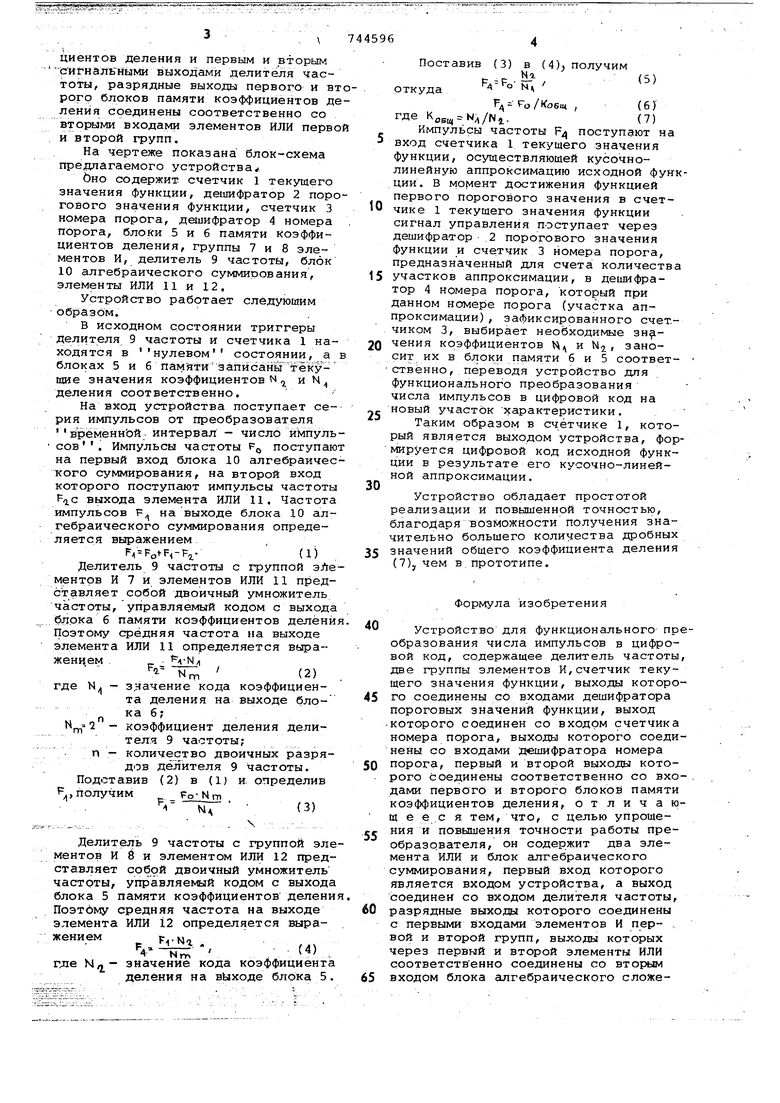

На чертеже показана блок-схема предлагаемого устройства

Ьно содержит счетчик 1 текущего значения функции, дешифратор 2 порогового значения функции, счетчик 3 номера порога, дешифратор 4 номера . порога, блоки 5 и 6 памяти коэффициентов деления, группы 7 и 8 элементов И, делитель 9 частоты, блок 10 алгебраического суммирования, элементы ИЛИ 11 и 12.

Устройство работает следующим образом.

В исходном состоянии триггеры делителя 9 частоты и счетчика 1 находятся в нулевом состоянии, а в блоках 5 и 6 памятизаписанЙтёку- щие значения коэффициентов N и N деления соответственно.

На вход устройства поступает серия импульсов от преобразователя врёменной. интервал - число йМпульсов . Импульсы частоты FJJ поступают на первый вход блока 10 алгебраического суммирования, на второй вход которого поступают импульсы частоты Fac выхода элемента ИЛИ 11. Частота импульсов F на выходе блока 10 алгебраического суммирования определяется выражением

P Fo -FrFi-(1)

Делитель 9 частоты с группой эЛементрв И 7 и элементов ИЛИ 11 предтавляет собой двоичный умножитель частоты, управляемый кодом с выхода блока б памяти коэффициентов деления. Поэтому средняя частота на выходе элемента ИЛИ 11 определяется выра-енцем . л-М/)

Nrn (2) .

где N з.начение кода коэффициента деления на выходе бло ка 6;

N 2 - коэффициент деления делителя 9 частоты;

п - количество двоичных разрядов делителя 9 частоты. Подставив (2) в (1) и определив

1-, получим

(3)

Делитель 9 частоты с группой элементов И 8 и элементом ИЛИ 12 представляет собой двоичный умножитель частоты, управляемый кодом с выхода блока 5 памяти коэффициентов деления Поэтбму средняя частота на выходе элемента ИЛИ 12 определяется выра- . жением Р.-Ыа ....

V-NT;; . , . гле значение кода коэффициента

деления на вЬаходе блока 5.

Поставив (3) в (4), получим откуда PA POFT,

. , (6)

где Ko5.N;,/Ni.(7)

Импульсы частоты F поступают на -вход счетчика 1 текущего значения функции, осуществляющей кусочнолинейную аппроксимацию исходной функции. В момент достижения функцией первого порогового значения в счет« чике 1 текущего значения функции сигнал управления поступает через дешифратор 2 порогового значения функции и счетчик 3 номера порога, предназначенный для счета количества

5 участков аппроксимации, в дешифратор 4 номера порога, который при данном номере порога (участка аппроксимации) , зафиксированного счет.чиком 3, выбирает необходимые чения коэффициентов Нд и Nj, заносит их в блоки памяти 6 и 5 соответственно, переводя устройство для функционального преобразования числа импульсов в цифровой код на новый участок характеристики.

Таким образом в счётчике 1, который является выходом устройства, формируется цифровой код исходной функции в результате его кусочно-линейной аппроксимации.

Устройство обладает простотой

реализации и повышенной точностью, благодаря ВОЗМОЖНОСТИ получения значительно большего количества дробных 5 значений общего коэффициента деления (7)у чем в прототипе.

Формула изобретения

Устройство для функционального преобразования числа импульсов в цифровой код, содержащее делитель частоты, две группы элементов И,счетчик текущего значения функции, выходы которо5 го соединены со входами дешифратора пороговых значений функции, выход которого соединен со входом счетчика номера порога, выходы которого соединены со входами дешифратора номера

0 порога, первый и второй выходы которого соединены соответственно со входами первого и второго блоков памяти коэффициентов деления, отличающееся тем, что, с целью упрощения и повышения точности работы преобразователя, он содержит два элемента ИЛИ и блок алгебраического суммирования, первый вход которого является входом устройства, а выход соединен со входом делителя частоты,

разрядные выходы которого соединены с первыми входами элементов И пер- . вой и второй групп, выходы которых через первый и второй элементы ИЛИ соответственно соединены со вторым

входом блока алгебраического сложения и входом счетчика текушего значения функции, управляющий и сигнальный входы первого и второго элементов ИЛИ соединены соответственно с управляюшими выходами первого и второго блоков памяти коэффициентов деления и первым и вторым сигнешьными выходами делителя частоты, разрядные выходы первого и второго блоков памяти коэффициентов деления соединены соответственно со вторыми входами элементов ИЛИ первой и второй групп.

Источники информации, принятые во внимание при эксперт.изе

1.Авторское св1Швтельство СССР 247642, кл. 42 м 3/00, 1968.

2.Авторское свидетельство СССР 248349, кл. 42 м 3/00, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU398985A1 |

| Аналого-цифровой функциональный преобразователь | 1975 |

|

SU542210A1 |

| АНАЛОГО-ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1969 |

|

SU248349A1 |

| ЦИФРОВОЙ КУСОЧНО-ЛИНЕЙНЫЙ АППРОКСИМАТОР | 1969 |

|

SU247642A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Телеметрическая система со сжатием информации | 1989 |

|

SU1672502A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

Ж

Авторы

Даты

1980-06-30—Публикация

1977-07-03—Подача