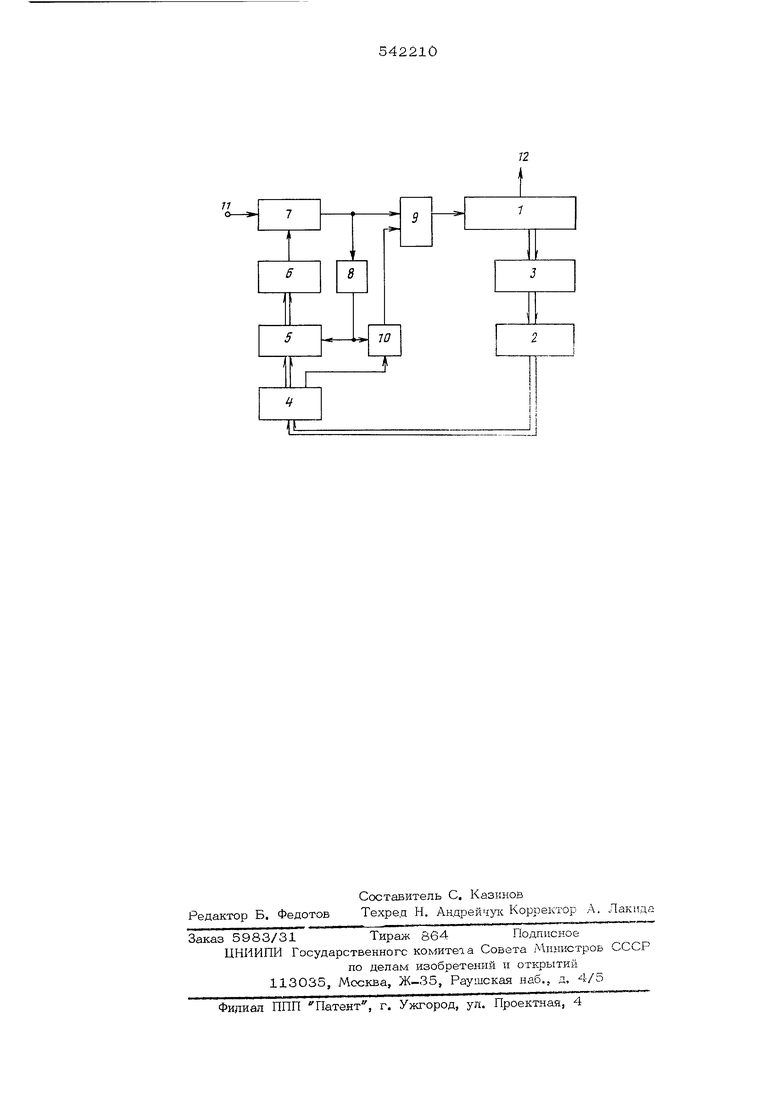

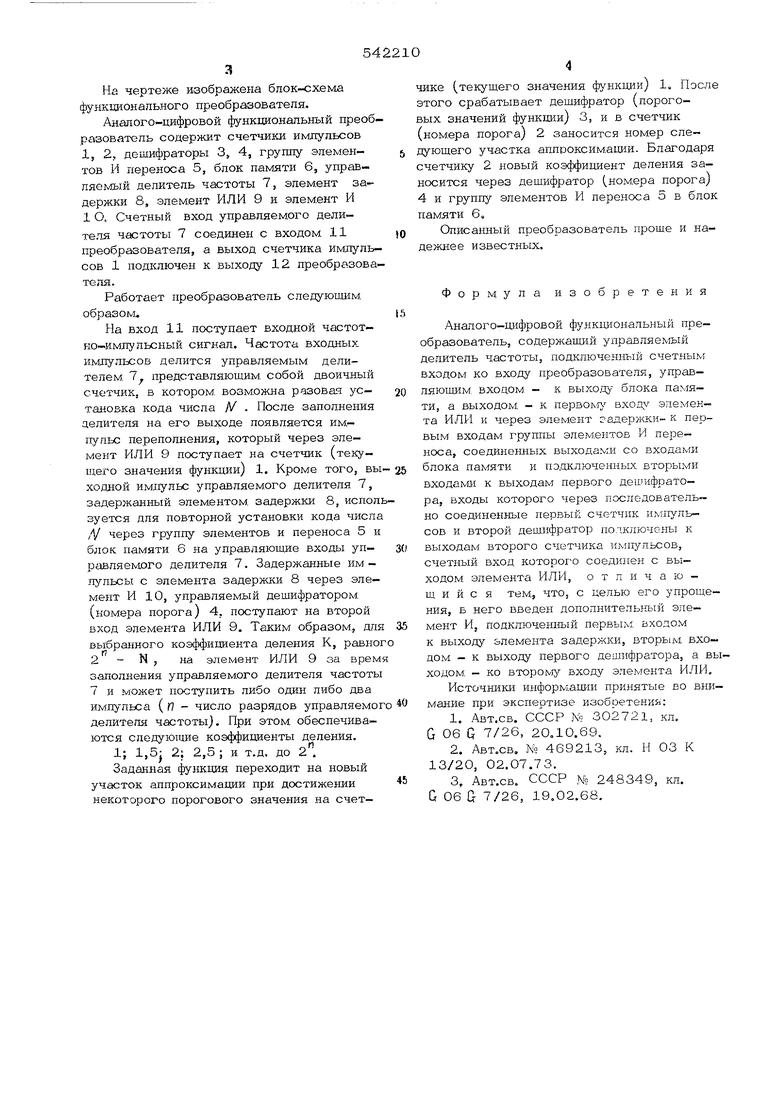

На чертеже изображена блок-схема функ1хионапьного преобразователя.

Аналого-цифровой функциональный преобразователь содержит счетчики имлупьсов 1, 2, дешифраторы 3, 4, группу элем.ентов И переноса 5, блок памяти 6, управляемый делитель частоты 7, элемент задержки 8, элемент ИЛИ 9 и элемент И 1 О, Счетный вход управляемого делителя частоты 7 соединен с входом. 11 преобразователя, а выход счетчика импудь сов 1 подключен к выходу 12 преобразователя.

Работает преобразователь следующим образом

На вход 11 поступает входной частотко-имлульсный сигнал. Частота входных импульсов делится управляемым делителем, 7., представляющим собой двоичный счетчик, в котором, возможна разовая усTaiiOBKa кода числа /V . Пссле заполнения целителя на его выходе появляется имггупьс переполнения, который через элемент ИЛИ 9 поступает на счетчик (текущего значения функции) 1. Кроме того, вы ходлой имлульс управляем.ого делителя 7, задержанный элементом, задержки 8, исползуется для повторной установки кода числа ,У через группу элементов и переноса 5 и блок памяти 6 на управляющие входы уп- равляемого делителя 7. Задержанные импульсы с элемента задержки 8 через элемент И 10, управляемый дешифратором (номера порога) 4. поступают на второй вход элемента ИЛИ 9. Таким образом., для выбранного коэффициента деления К, равног 2 - N , на элемент ИЛИ 9 за врем заполнения управляемого делителя частоты 7 и может поступить либо один либо два импульса ( /9 - число разрядов управляемог делителя частоты). При этом обеспечиваются следующие коэффициенты деления. 1; 1,5- 2; 2,5 ; и т.д. до 2 Заданная функция переходит на новый участок аппроксимации при достижении

некоторого порогового значения на счетчике (текущего значения функции) 1. После этого срабатывает дешифратор (пороговых значений функции) 3, и в счетчик (номера порога) 2 заносится номер следующего участка аппроксимации. Благодаря счетчику 2 новый коэффициент деления заносится через дешифратор (.номера порога) 4 и группу элементов И переноса 5 в блок памяти 6.

Описанный преобразователь проще и надежнее известных.

Формула изобретения

Аналого-цифровой функциональный преобразователь, содержащий управляемый делитель частоты, подключенный счетным входом ко входу преобразователя, управляющим, входом - к выходу блока памяти, а выходом - к перво Г} элемента ИЛИ и через элемент задержки- к первым входам группы элементов И переноса, соединенных выходами со входами блока памяти и пэдключенных вторыми входами к выходам первого дешифратора, входы которого через последовательно соединенные первый счетчик им.пульсов и второй дешифратор подключены к выходам второго счетчика имщ дьсов, счетный вход которого соединен с выходом элемента ИЛИ, отличающийся тем, что, с целью его упрощения, в него введен дополнительный элемент И, подключенный первым, входом к выходу элемента задержки, вторь1м вхо дом - к выходу первого дешифратора, а входом. - ко BTOpOMj входу элемента ИЛИ.

Источники информ.ации принятые во внимание при экспертизе изобретений:

1.Авт.св. СССР № 302721, кл, G 06 Q 7/26, 20,10.69.

2.Авт.св. № 469213, кл. Н 03 К 13/20, 02.О7.73.

3.Авт.св. СССР № 248349, кл. G 06 G- 7/26, 19,02.68.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Устройство для функционального преобразования числа импульсов в цифровой код | 1977 |

|

SU744596A1 |

| ЦИФРОВОЙ КУСОЧНО-ЛИНЕЙНЫЙ АППРОКСИМАТОР | 1969 |

|

SU247642A1 |

| Устройство для функционального преобразования цифровых сигналов | 1979 |

|

SU864293A1 |

| АНАЛОГО-ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU398985A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

Авторы

Даты

1977-01-05—Публикация

1975-10-20—Подача