I .

Изобретение относится к вычислительной технике, предназначено для вычисления оценок корреляционных фуйкций и может быть использовано в системах обработки информации корреляционного приема сигналов и статистических анализаторах и др.

Известны цифровые устройства выполняющие вычисление оцено к корреляционных функций на основе прямых методов. Они имеют низкую производительность при большом числе значений аргумента задержки, так как количество умножений, которые необходимЬ выполнить, растет пропорционально квадрату количества значений аргумента.

Известно цифровое устройство, выполняющее вычисление, оценок корреляционных функций, обладающее при большом числе значений аргумента задержки высокой производительностью И .

Однако это устройство содержит аналого-цифровые преобразователи (АЦП), блок умнох ения, сумматор,вычитатель, триггеры, реверсивный счет чик, регистры, устройства, использующие преобразование Фурье, и не обеспечивает высокой точности корреляционного анализа, так как имеется

с алгоритмическая ошибка, вызванная конечностью числа базисных функций, и вносятся инструментальные погрешности, связанные с сяяибками округления и приближенным представлением

10 коэффициентов Фурье. Кроме того,они требуют сложного оборудования для выполнения операций с комплексными числами.

Устройства, использующие преобtf разование Уолша, для обеспечения такой же величины общей ошибки требуют существенно болыиего числа базяскак функций, что оказывает отрицательное влияниена производительность таких устройств.

20

Наиболее близким к изобретению является устройство, в состав которого входят два входных АЦП,входы которых являются соответственно первым и вторым входами процессора,

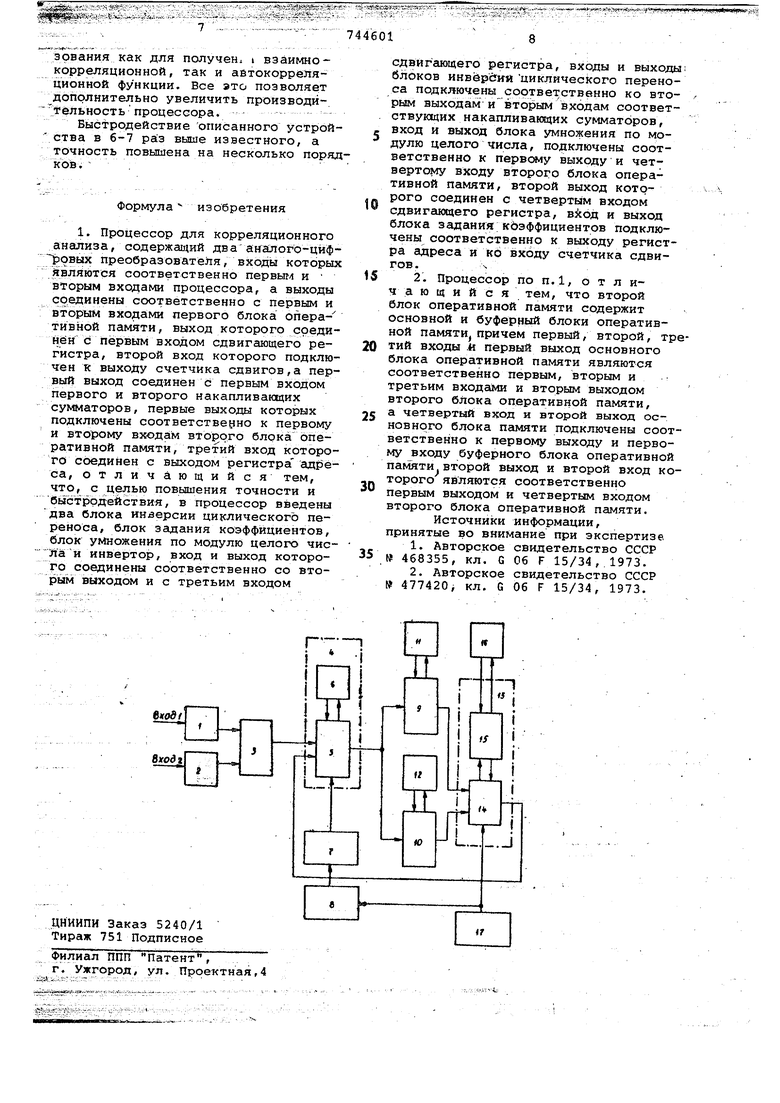

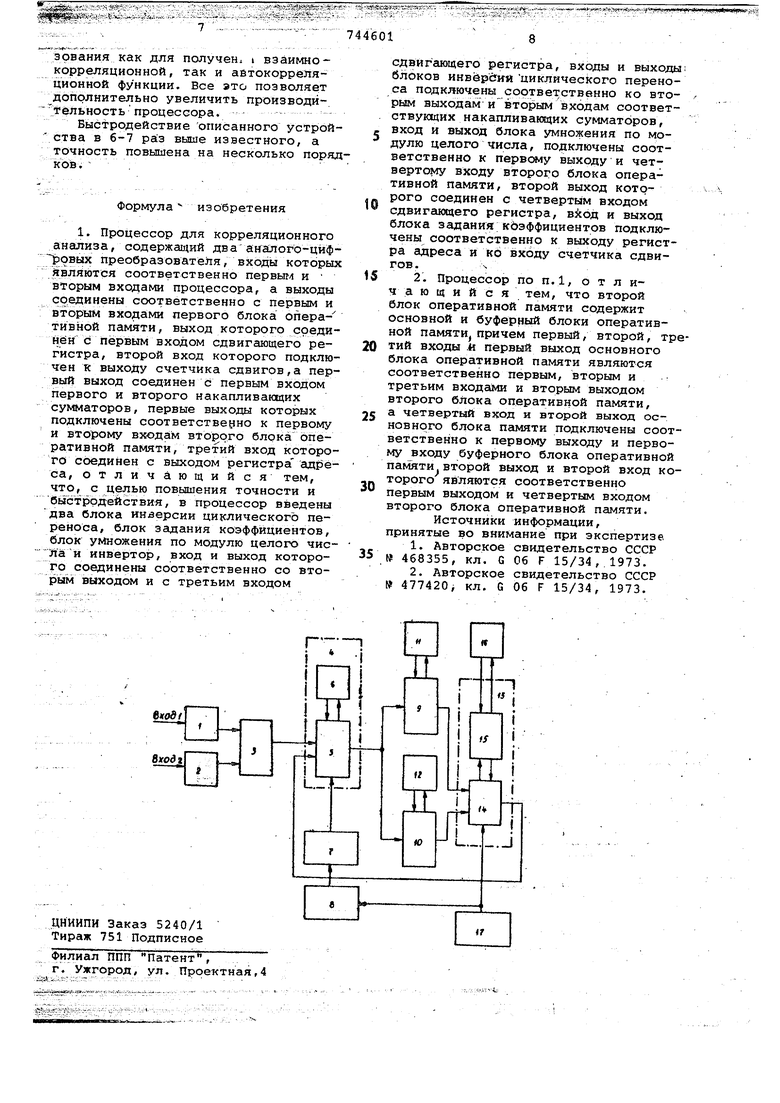

25 а выходы соединены соответственно с первым и вторым входами первого блока оперативной памяти, выход которого соединен с первым входом сдви,л гающего регистра, второй вход которого подключен к выходу счетчика сдвигов, а первый выхэд соединен с первым входом первого и второго на капливакндих сумматоров, первые в::олы которых подключены соответственно к первому и второму входам второго бло ка оперативной памяти,, третий вход которого соединен с выходом регистра адреса 2 ., , Вычисление корреляционных функций в устройстве осуществляется на основе быстрого преобразования Уолша,для выполнения которого в сумматорах производится сложение или вычитание чисел,поступающих из циклических сдв говых регистров. Недостатком указанного устройства является большая алгоритмическая оши ка вычислений, вызванная тем, что функции Уолша, по которым производился р1а ложение входных процессов, дают большую ошибку представления этих процессов при ограниченном числа членов ряда.Снижение алгоритми ческой ошибки в устройстве достигает использованием большого числа базисных функций УОЛША, но при этом устройство характеризуется большим количеством элементарных операций (умножение на 1 1 и сложение), выполняемых сумматорами, и, следовательно, низким быстродействием. Устройство характеризуется также бол шой инструментальной ошибкой, вызванной необходимостью округления результатов при масштабировании во избежание переполнения разрядной сетки из-за конечной разрядности сумматоров и ОЗУ. Цель изобретения - повышение точности корреляционного анализа и быстрЬдействия устройства. Поставленная цель достигается тем что в процессоре используется тесзретико-числовое преобразование Рейдер при котором все вычисления выполняю ся в кольце Целых чисел с помощью Простых операций сдвига и сложения, для чего в устройство введены два блока инверсии циклического перенос блок задания коэффициентов, блок ум но;хения по модулю целого числа и ин вертор, вход и выход которого соединены соответственно со вторым выходом и третьим вх дом сдвигающего регистра, входы и выходы блоков инверсии циклического переноса подключены соответ ственно ко вторым выходам и,вторым входам соответствующих накапливающи сумматоров, вход и выход блока умно жения по модулю целого, числа подключены соответственно к первому выходу-и четвертому входу второго блока оперативной памяти, второй вы ХОД которого соединен с четвертым входом сдвигающего регистра, вход и выход блока задания коэффициентов подключены соответственно к выходу регистра адреса и ко входу счетчика сдвигов. Кроме того второй блок оперативной памяти содержит основной и буферный блоки оперативной памяти, причем первый, второй, третий входы и первый выход основного блока оперативной памяти являются соответственно первым, вторым и третьим входами и вторым выходом второго блока оперативной памяти/а четвертый вход и второй выход основного блока памяти подключены соответственно к первому выходу и первому входу буфернЬго блока оперативной памяти, второй выход и второй вход которого являются соответственно первым выходом и четвёртым входом второго блока оперативной памяти. На чертеже изображена структурная схема предлагаемого устройства (пример конкретного выполнения). На каждом из двух входов устройство содержит АЦП 1 и 2, соединенные выходами с первым блоком 3 оперативной памяти (БОП), который подключен к первому информационному входу циклического сдвигового регистра 4, состоящего из сдвигового регистра 5 и инвертора б, включенного в цепь обратной связи, идущей с выхода старшего разряда сдвигового регистра 5 на вход его младшего разряда.Управляющий вход регистра 4 соединен с выходом счетчика 7 сдвигов, а вход последнего - с выходом блока 8 задания коэффициентов. Выход регистра 4 соединен со входами накапливаюгдих сумматоров 9 и 10, выходы переноса которых соединены со входами соответствующих блоков 11 и 12 инверсии циклического переноса. Выходы блоков 11 и 12 соединены соответственно с входами младших разрядов сумматоров 9 и 10. Второй БОП 13 состоит из соединенных между собой двухсторонней связью основного БОП 14 и буферного БОП 15, дополнительные выход и вход которого соединены с входом и выходом блока16 умножения по модулю целого числа. Выходы сумматоров 9 и 10 соединены с информа ционными входами БОП 14, выход которого в свою очередь подключен ко второму входу регистра 4. Выход регистра 17 адреса соединен с адресным входом блока 13 и входом блока 8. Устройство вычисляет оценки корреляционной Функции с помощью прямых и обратных числовых преобразователей. Вычисление корреляционных функций с Использованием ортогональных преобразователей производится по формуле .у .j где г - вектор-столбец, состоящий из результатов вычисления оценки корреляционной функции; N - длина преобразуемой после довательности; Т - матрица обратного преобразования;Т - матрица прямого преобразо вания; X - вектор-столбец N чисел, поступающих по первому ухо ду , ® - операция поэлементного пер множения векторов; Y - вектор-столбец из М чисел, поступивших по второму каналу , дополненных N-M нулями. Для числового преобразования Рей дера матрица преобразований имеет вид о ;;; Матрица Т имеет ту же структуру только показатели основания 2 отрицательные. Все вычисления ведутся в кольце целых чисел по модулю числ Ферма F 2 + 1 (t - целое). Структура матриц Т и Т такова,что преобразование может производиться по быстрому алгоритму с использованием методов, применяемых для быстрого преобразования Фурье, например прореживания по времени. При этом преобразование последовательности и N чисел проводится за Еод N ите раций , а в каждой итерации вычисNляется у величин вида А + 2 (mod Ft ) , А + 2. (mod F ) .. Поэлементное перемножение резуль татов прямых преобразований и обратное преобразование производятся также по модулю числа F . Выбор величины F определяет длину преобразуемой последовательности N и разрядность операционного устройств применяемого для преобразования. Устройство работает следующим образом, АЦП 1,2 преобразуют входные аналоговые сигналы в последовательност чисел, которые запоминаются в БОИ 3 Из БОП 3 числа попарно передаютс через циклический сдвиговый регистр 4 и в накапливакядие сумматоры 9 и 1 Причем,первое из чисел А передается без сдвига, второе число в регист ре 4 сдвигается на к разрядов в сто рону старших разрядов, что эквивалентно умножению на 2, а затем поступает в накапливающие сумматоры. /x-/vСумматор 9 осуществляет сложение, а сумматор 10 вычитание. Таким образом, над числами А и В производятся операции (2). Результаты записываются в БОП 13. Благодаря наличию блоков 11 и 12 и инвертора б, вычисления ; производятся по модулю числа F .Разрядность регистра и сумматоров равна t. В состав блоков инверсии циклического переноса входят схемы, предотвращающие возникновение режима генерации при наличии единиц во всех разрядах. Блок 8 задания коэффициентов обеспечивает последовательное коэффициентов к, необходимых для вычисления преобразования .по быстрому aлгopит y, и представляет собой цифровой автомат. Управление сдвигами в регистре 4 осуществляется счетчиком 7, в который предварительно записывается нужное число сдвигов из блока 8. В БОП 14 записываются и -считываются результаты промежуточных вычислений. Промежуточные результаты, записанные в него, снова подаются в циклический сдвиговый регистр 4. Операция (2) повторяется многократно до полного завершения преобразования. Окончательный результат преобразования поступает в БОП 15. В течение времени пока БОП 14 участвует в следующем преобразовании, БОП 15 осуществляет обмен 6 блоком умножения 16, в котором происходит поэлементное перемножение результатов прямых преобразований в соответствии с выражением (1). Над полученным произведением, переписанным в БОП 14, выполняется обратное преобразование таким же образом, как и прямое, за исключением того,что коэффициенты меняют знак показателя на обратный и становятся 2. N-М вычисленных значений, соответствующие апериодической части результата обратного преобразования, являются точными Значениями оценки корреляционной функции исходных входных процессов. В блоках оперативной памяти хранятся результаты прямьрс преобразований, полученных в предыдущих циклах вычислений. Под циклом вычислений понимается выполнение необходимых преобразований, завершающееся обратным преобразованием. Наличие БОП 15 позволяет использовать одно и то же прямое преобразование в нескольких циклах вычислений для тех случаев, когда требуется реализовать максимальный диапазон аргумента задержки, имекхций величину, большую длительности отрезка входной реализации, участвующего в одном преобразовании. Кроме того, наличие ОЗУ Дает возможность использовать один и тот же результат прямого преобра

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления свертки | 1985 |

|

SU1297073A1 |

| Адаптивный цифровой измеритель параметров сигнала | 1981 |

|

SU1013867A1 |

| Цифровой анализатор энергетического спектра | 1978 |

|

SU769443A1 |

| Устройство для спектрального анализа | 1978 |

|

SU767774A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Авторы

Даты

1980-06-30—Публикация

1978-01-25—Подача