1

Изобретение относится к запоминающим устройствам.

Известны устройства для контроля оперативной памяти{1 и 2.

Одно из известных устройств для контроля памяти содержит формирователь тестовой программы контроля, Ьлок выбора адресов памяти и блок сравнения считываемой информации с эталонной 1 . I

Недостатком этого устройства является невысокое быстродействие.

Из известйых устройств наиболее близким техническим решением к изобретению является устройство для контроля оперативной памяти содержащее регистры числа, выходы которых подключены ко входам блока сравнения, адресов, подключенный к пульту управления и блоку управления, соединенному с блоком формирования тестовых сигналов, первый выход которого подключен ко входу одного из регистров числа 2 .

К недостаткам этого устройства относится отсутствие возможности cjaтистического анализа в процессе контроля. амплитудных и временных паргшетров считанных сигналов. Такой анализ

позволил бы минимизировать уровень помех на выходе оперативной памяти, . выбрать оптимальное по помехоустойчивости сочетание параметров блока воспроизведения информации; порога срабатывания амплитудного дискриминатора, длительности и местоположения строб-импульса на временной оси. Отсутствие такого анализа снижает наtoдежность устройства.

Цель настоящего изобретения - повыиение нгщежности устройства.

Поставленная цель достигается тем,

15 что устройство содержит амплитудный дискриминатор, элемент задержки и блоки анализа параметров сигналов 1 и О, причем выходы блоков анализа параметров сигналов 1 и О подключены к выходам устройства, а входы - соответственно к выходам амплитудного дискриминатора, элемента задержки и блока управления, второму выходу блока формирования тестовых

25 сигнсшов и к одним из входов устройства. .Входы элемента задержки соеди;неыы с одними из выходов блока управления и пульта управления, входы амплитудного дискриминатора подключены к другому выходу пульта управления, третьему выходу блока формирования тестовых сигналов и другому входу устройства.

При этом целесообразно блок анализа параметров сигналов 1 выполнить таким образом чтобы он содержал элементы И, выход первого из которых подключен к одним из входов второго и третьего элементов И, другие входы которых, а также входы первого элемента и соединены со входами блока анализа параметров сигналов 1, выходы которого подключены к выходам элементов И.

БЛОК анализа параметров сигналов О целесообразно выполнить в виде узла, содержащего дополнительные элементы И триггеры, входы которых, а такжеодни из входов дополнительных элементов И соединены со входами блока анализа параметров сигналов О, выходы которого подключены к выходам дополнительных элементов И, выходы триггеров соединены с другими входами первого и второго дополнительных элементов И, выходы которых подключены к другим входам третьего и четвертого дополнительных элементов И.

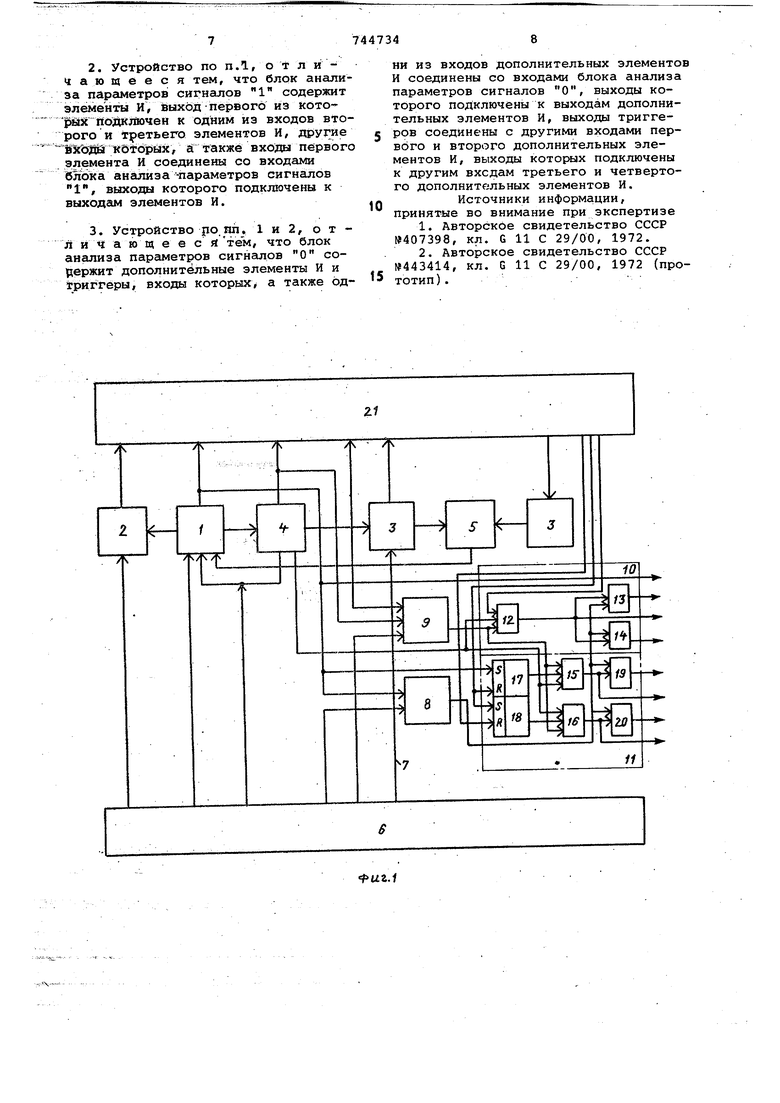

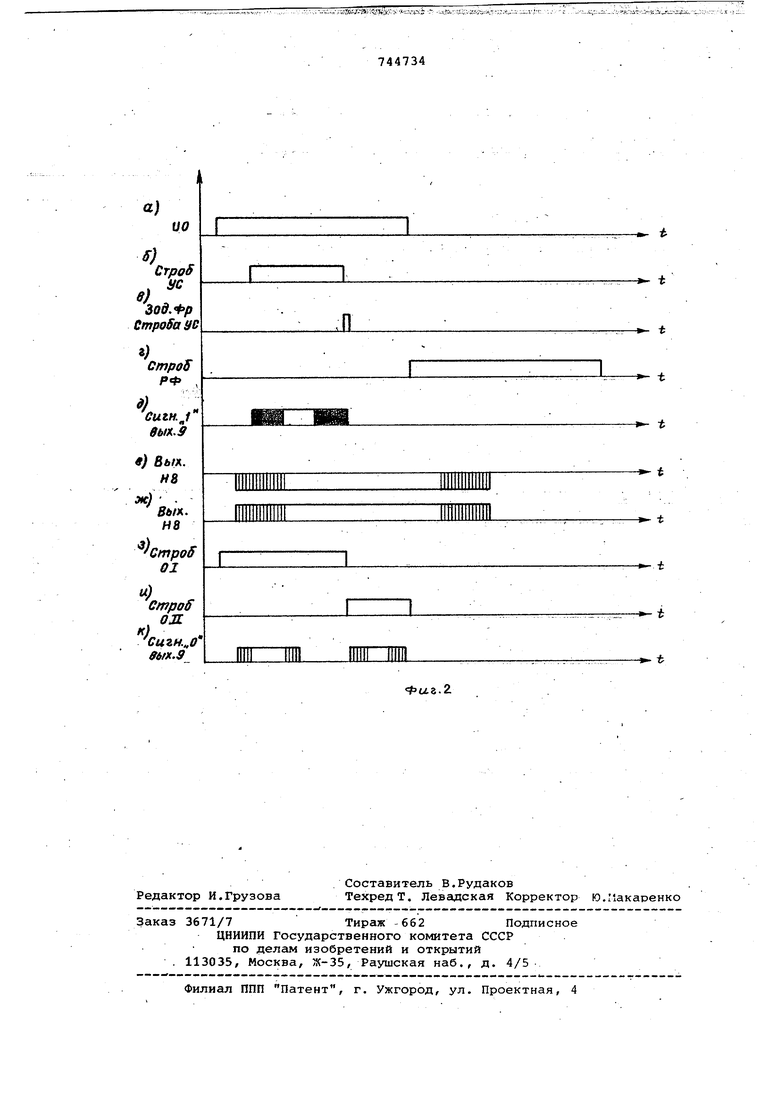

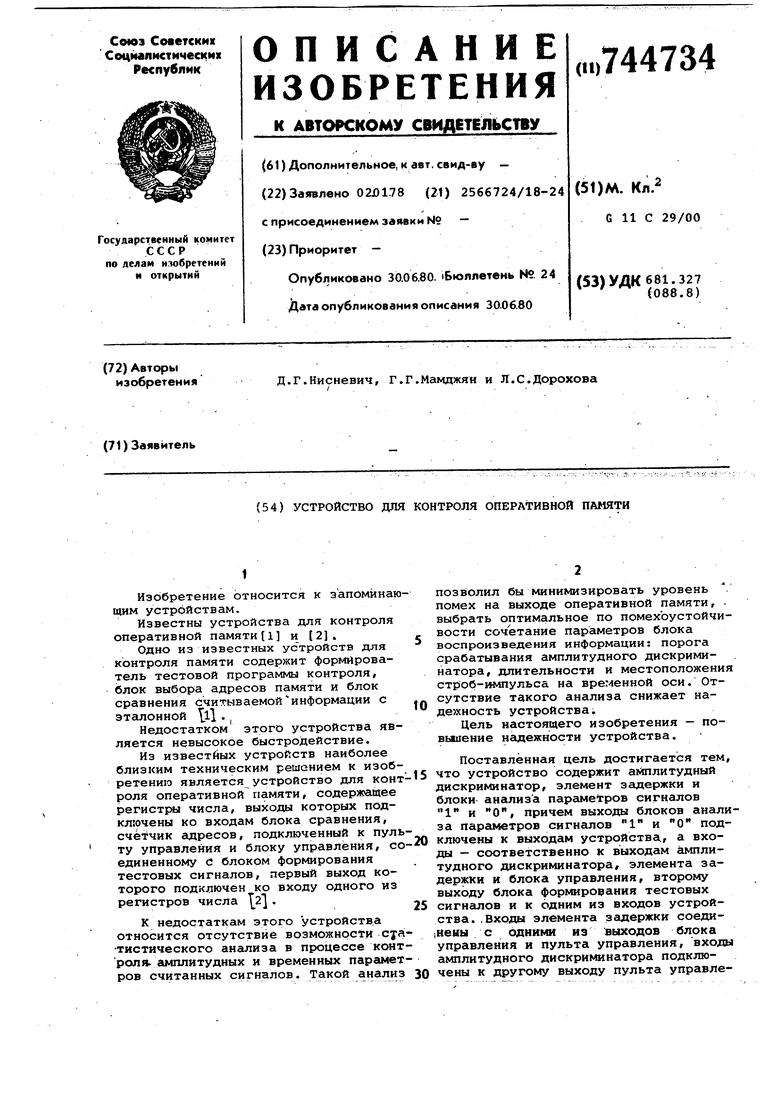

На фиг. 1 изображена блок-схема предложенного устройства на фиг. 2, а-к показаны временные диаграммы, поясняющие работу устройства.

Устройство для контроля оперативной памяти (см.фиг.1) содержит блок Г управления, счетчик 2 адресов, регистры 3 числа, блок 4 формирования тестовых сигналов, блок 5 сравнения, пульт 6 управления, выход 7 котордго подключен к одному из входов регистра 3, элемент 8 задержки; ё1мплитудный дискриминатор 9, блок 10 анализа параметров сигналов 1 и блок 11 анализа параметров сигналов О. Первый выход блока 4 подключен ко входу одного из регистров 3. Выходы блоков 10 и 11 соединены с выходами устройства, к которым подклюЧаКЬТся тэчётчйки йг-шуяьеьв или частотомеры (на фиг. 1 не показаны). Входы блоков 10 и 11 подключены сббтв тственно к .выходам дискриминатора 9, элемента 8 задержки и блока 1, второму выход блока 4 и к одним из входо устройства. Входы элемента 8 задерж Соединены с одним из выходов блоwa. 1 и пульта б управления. Входы Дискриминатора 9 подклю ны к другого выходу пульта б управления, третьему выходу блока 4 и другому входу устройства. /

Блок 10 содержит первый 12-, второ 13 и третий 14 элементы И. Выход элемента И 12. подключен к одним; йз вхоДрв элементов И 13 и 14, другие вход кбторых7 а также входы элемента И 12 соединены со входами блока 10, вы744734

ходы которого пдключены к выходам элементов И 12-14.

Блок 11 содержит первый 15 и второй 16 дополнительные элементы И, триггеры 17 и 18 и третий 19 и четветый 20 дополнительные элементыИ. |Входы триггеров 17 и 18, а также одни из входов элементов И 15, 16, 19 20 соедине1ны со входами блока 11, выходы которого подключены к выходам элементов И 15, 16, 19, 20. .

,Выходы триггеров 17 и 18 соединены с другими входами элементов И 15 и 16, выходы которых подключены к другим входам элементов и 19 и 20.

Входы и выходы устройства подключаются к контролируемому блоку 21 оперативной памяти.

Устройство для контроля .оперативной памяти работает следующим образом. .

На пульте б,задаётся требуемый ,режим работы. Для определения статйсти еских характеристик считанных сигналов используется режим, аналогичный режиму получения вероятностной работы области работоспособности оперативной памяти устройствапрототипа 2, при котором останов тестовой программы производится полным циклом теста, а для- каждого очередного запуска цикла используется кнопка Пуск на пульте управления. При каждом прого.не тестовой программы для заданных порога дискриминации и задержки момента стробирования относительно импульса обращения счетчики, подключенные к выходам блоков 10 и 11, подсчитывают количества импульсЬтв, характеризующие требуегше амплитудные и временные распрделения. Такиг ш распределениями, например, для магнитных оперативных блоков памяти на ферритовых серДечниках и пластинах являются слёдующие распределения амплитуд на выходе линейного усилителя блока памяти: импульса 1 - F(E), импульса помехи, предшествующего полезному сигналу (первый импульс О) F°(E); импульса помехи, следующего за пролезным сигналом (второйимпульс О) F°(E), и/ следующие временные распределения фронтов импульсов на выходе амплитудного дискриминатора: передних и задних фронтов импульсов 1, соответственно Fn(t) и F(t), заднего фронта первого импульса О - Fg( t) и переднего фронта второго импульса О - F(t).

Рассмотрим более, подробно получение указаннь1Х распределений.

, Амплитудные распределения 1 формируются при помощи элементс1 И 12 в котором производится стробирова ние сигнала 1 на выходе амплнтудно го дискриминатора 9 (см.фиг.2 д) предвари тел bHfcjM стробом усйлитсгля считывания блока 21.. В результате стробирования считанного сигнала на выходе амплитудного дискримйнато ра 9 и на выходе элемента И 12 выделяется импульс 1. Подсчитывая количество импульсов 1 - N/ за вр мя полного периода теста Ny находим вероятность превышения считанным сигналом 1 установленного на пуль те управления порога дискриминации .Е Изменяя уровни порогов Е-, и полу чая соответствующие значения Р) при очередных прогонах устройства, опре деляем статистическую функцию распределения амплитуд сигнала 1. Для получения распределений ампли туд первого и второго импульсов О необходимо произвести разделение этих импульсов с помощью соответствующих стробов, получаемый на выходах триггеров 17 и 18 в блоке 11 формирования распределений О. Пода вая стробы ОТ и 01 получим на выходах элементов И 15-16 функции распре деления амплитуд первого импульса О - F°(E) 1-1V{E) и второго импульса О - F(E) I-P°V(E). Для получения временных распределейий задержек проховдения фронтов импульсов используется регулируемый элемент 8 задержки в требуемой полярности , он подключается к одним входам элементов И 19 и 20, на вторые входы которых поступают сигналы .с выходов элементов И 15 и 16. На фиг. 2,е и 2,ж показаны прямой и инверсный задерхсанные сигналы стробирования на выходе элемента 8 задер ки. Когда время задержки равно нулю то в элементе И 13 совпадения не произойдет (см.фиг.2,д и 2,е) и за время полного, периода теста на вьгход элемента И 13 не пройдет ни одного импульса. При увеличении времени задержки командой с пульта управления до значения, превышающего некоторую величинуГмин(На выходе элемента И 13 появится некоторое число импульсов ). Это произойдет толь ко В.ТОМ случае, если передний фронт импульса 1 пройдетраньше фронта строба 1, т.е. когда задержка переднего фронта импульса 1 будет меньше, чем , . Тогда вероятность того, что задерхска переднего фронта импульса 1 меньше, чемт:зад.,/ равна р l-iSj. Меняя с пульта управлени времена задержек и производя прогоны тестовой программы для каждого значе с фиксацией количества импульсов на выходе элемента И 13 посредством счетчика (или частотомера) , определяют функцию распределения задержек передних фронтов импульса 1, F(t) P;(t Гзо,д) Аналогичным образом находятся временные распределения: заднего фронта импульса 1 - РЗ (t) 1-РЗ (t Гзо,д ); заднего фронта первого импульса О - p3(t), переднего фронта второго импульса О. Триггеры 17 и 18 необходимы для формирования стробов ОГ и 01, определяющих априорно ожи- , даемую зону появления соответственно заднего фронта первого импульса О и переднего фронта второго импульса О. Таким образом, с помощью незначительных аппаратурных затрат (порядка десяти корпусов интегральных схем малой интеграции) в описанном устройстве обеспечивается не только контроль работоспособности по критерию сбой, нет сбоя, но и возможность получения статистических распределений считанных сигналов на входе блока воспроизведения информации, т.е. полная физическая картина процесса считывания информации на выходе разрядно-считывающей линии блока памяти. Это позволяет выбрать оптимальные методы стробирования, уровень порога, длительность стробирующего импульса, его место на временной оси и др. Формула изобретения 1. Устройство для контроля оперативной памяти, содержащее регистры чисЛа, выходы которых подключены ко входам блока сравнения, счетчик адресов, подключенный к пульту управления и блоку управления, соединенному с блоком формирования тестовых сигна- лов, первый выход которого подключен ко нходу одного из регистров числа, отличающееся тем, что, с целью повышения надежности устройства, оно содержит амплитудный дискриминатор, элемент задержки и бЛоки анализа параметров сигналов 1 и О, причем выходы блоков анализа параметров сигналов 1 и О подключены к выходам устройства, а входы - соответственно к выходам амплитудного дискриминатора, элемента задержки и блока управления, второму выходу блока формирования тестовых сигналов и одним из входов устройства, входы элемента задержки соединены с одними из выходов блока.управления и пульта правления, входы амплитудного дискриминатора подключены к другому выходу пульта управления, третьему выходу блока формирования тестовых сигналов и другому входу устройства.

2.Устройство по п.1, о т л и чающееся тем, что блок анализа парс1метров сигналов 1 содержит элементы И, выход первого из кото ры5С поЗШлючен к одним из входов второго и третьего элементов И, другие

аХЬШ KetopEjx, а также входы первого элемента И соединены со входами блока анализа -параметров сигналов 1, выходы которого подключены к выходам элементов И.

3.Устройство jio.Hn, 1 и 2, о т л и ч: а ю щ ее с итем, что блок анализа параметров сигналов О содержит дополнительные элементы И и триггеры, входы которых/ а также одни из входов дополнительных элементов И соединены со входами блока анализа параметров сигналов О, выходы которого подключены к выходам дополнительных элементов И, выходы триггеров соединены с другими входами первого и второго дополнительных элементов И, выходы которых подключены к другим входам третьего и четвертого дополнительных элементов И. Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР №407398, кл. G 11 С 29/00, 1972.

2.Авторское свидетельство СССР №443414, кл. G 11 С 29/00, 1972 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения информаций из оперативной памяти | 1975 |

|

SU547833A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| Устройство для ввода учебной информации | 1990 |

|

SU1732369A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для измерения частоты | 1979 |

|

SU813291A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Устройство для контроля качества магнитного носителя | 1984 |

|

SU1182576A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

ри.ъ.2.

Авторы

Даты

1980-06-30—Публикация

1978-01-02—Подача