I

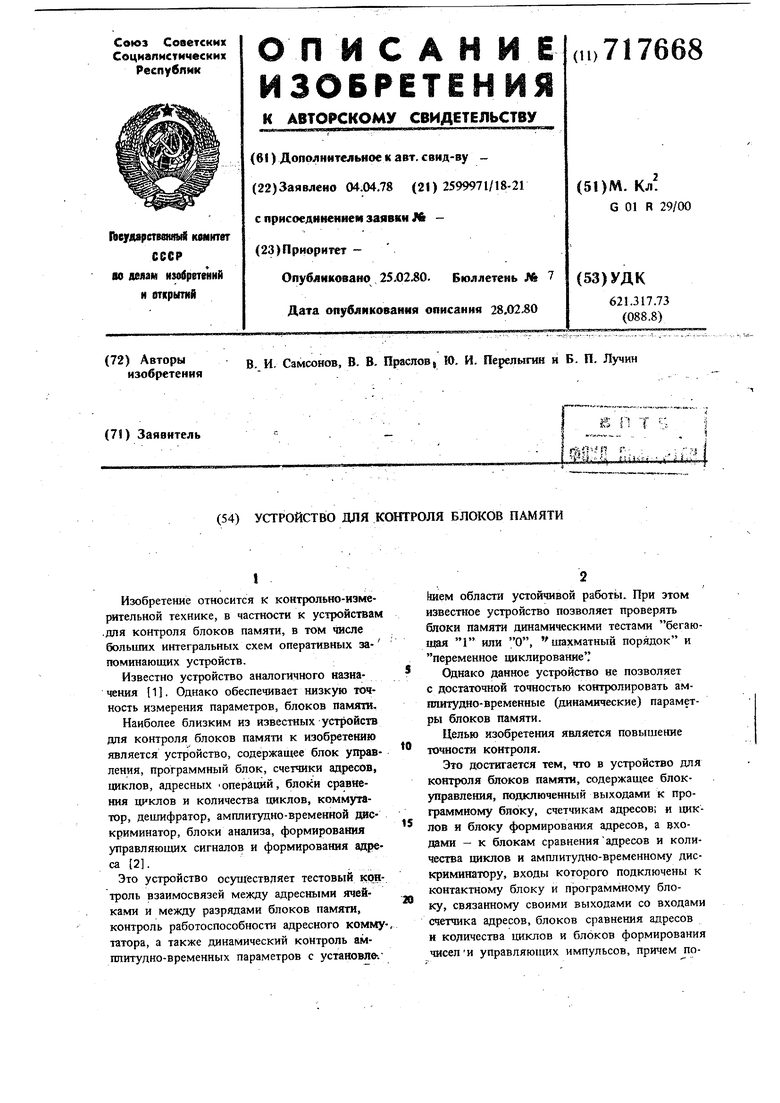

Изобретение относится к контрольно-измерительной технике, в частности к устройствам .для контроля блоков памяти, в том числе больших интегральных схем оперативных запоминающих устройств.

Известно устройство аналогичного назначения (11. Однако обеспечивает низкую точность измерения параметров, блоков памяш.

Наиболее близким из известных устройств для контроля блоков памяти к изобретению является устройство, содержащее блок управления, программный блок, счетчики адресов, циклов, адресных операций, блоки сравнения циклов и количества циклов, коммутатор, дешифратор, амплитудно-временной дискриминатор, блоки анализа, формирования управляющих сигналов и формирования адреса 2.

Это устройство осуихествляет тестовый контроль взаимосвязей между адресными ячейками и между разрядами блоков памяти, контроль работоспособности адресного комму татора, а также динамический контроль амплитудно-временных параметров с установле-.Ьием области устойчивой работьк При этом известное устройство позволяет проверять блоки памяти динамическими тестами бегающая 1 или О, игахматньш порядок и переменное даклирование

Однако данное устройство не позволяет с достаточной точностью контролировать амшштудно-временные (динамические) параметры блоков памяти.

Целью изобретения является повышение точности контроля.

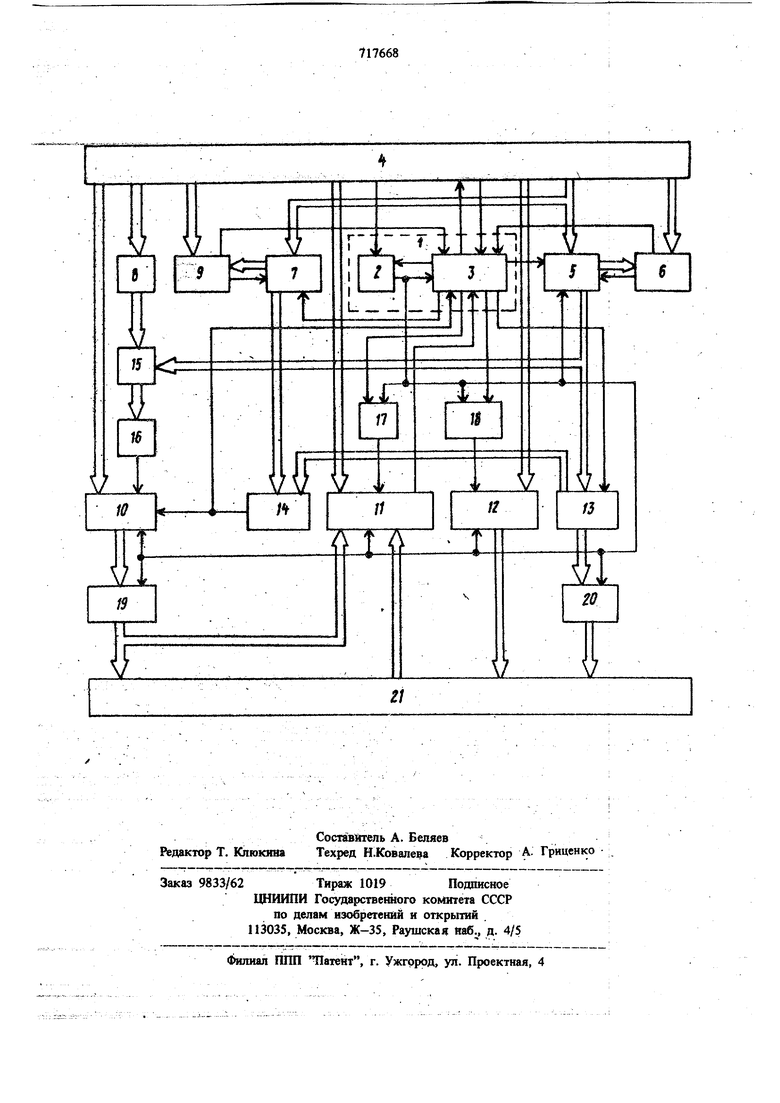

Это достигается тем, что в устройство для контроля блоков памяти, содержащее блокуправления, подключенный выходами к программному блоку, счетчикам адресов; и циклов и блоку формирования адресов, а входами - к блокам сравненияадресов и количества циклов и амплитудно-временному дискриминатору, входы которого подключены к контактному блоку и программному блоку, связанному своими выходами со входами счетчика адресов, блоков сравнения адресов и количества циклов и блоков формирования чиселИ управляющих импульсов, причем по37спедний своими выходами связан с контактным блоком, дешифратор, коммутатор, блок сравнения циклов, выход которого подклю н к блоку формирования чисел, а входы . связаны со счетчиком циклов, имеющим двустороннюю связь с блоком сравнения количества циклов, а через блок формирования адресов - со счетчиком адресов, имеющим двусторо1шюю связь с блоком сравнения адресов, введены блоки регистров адреса и чисел, многовходовой элемент ИЛИ и два регистра, первые входы которых и блоков регистров адреса и адсел объединены и подклюэдны к блоку управления, вторые входы регистров раздельно подключены к блоку управ ления, выход первого регистра подключен ко входу амплитудно-временного дискриминатора, выход второго регистра - .ко входу блока формирования улрав;)яющнх импульсов, вторы входы блока регистров адреса подключены к , блоку формироваю1Я адреса, а выходы контактному блоку, выходы блока регистров чисел подключены к контактному блоку и амплитудно-временному дискриминатору, а его вторые входы - к блоку формирования чисел вход которого подключен к вь1зсоду многовхрдового элемента ИЛИ, связанного своими входами с коммутатором, первые входы кото рого подключены k выходам счетчика адресов, связанным со входами блока формирования адресов, а вторые входы через дешифратор подключены к программному блоку. Структурная схема устройства дйя контроля блоков памяти приведена на чертеже. Устройство содержит блок 1 управления, включающий программирующий генератор 2 тактовых импульсов и блок 3 синхронизации связанные между собой двусторонней связью и подключенные своими первыми объеданенны ivffl входами к программному блоку 4, вход которого соединен с выходом блока 3 син хронизации блока 1 управления, а выходы подключены к счетчику 5 адресов, блоку 6 сравнения адресов, счетчику 7 циклов, деишфратору. 8, блоку 9 сравнения количества циклов, блоку 0 формирования чисел, амплитудно-временному дискриминатору 11 и блоку 12 формирования управляющих импуль сов. Счетчик 5 адресов своими выходами подключён ко входам блока 13. формирования адресов, а счетчик 7 циклов - ко входам блока 14 сравнения циклов. Устройство содержит также коммутатор 15, входы которого подключены к |,ешифратору 8 и выходам счетчика S .адерсов, связанным со входами блока 13 формирования адресов, & выходы коммутатора 15 соединены со входами многовходового элемента ИЛИ 16, выход которого подключен ко входу блока 10 формирования чисел, регистры 17 и 18, блок 19 регистров чисел, блок 20 регистров адреса и контактный блок 21 для включения объекта Проверки, который подключен ко входам амплитудно-временного дискриминатора II, выходам блока 12 формирования управляющих импульсов и выходам: блбков 19 и 20 регистров чисел и адреса соответственно. Управляющие (первые) входы регистров, 17 и 18 и блоков 19 и 20 регистров объединены и. подключены к выходу генератора 2 тактовых импульсов блока 1 Управления, вторые входы регистров 1.7 и 18 раздельно подключены к выходам блока 3 синхронизации блока 1 управления. Выход регистра 17 подключен ко входу амплитудно-временного даскримииатора 11, а выход регистра 18 - к блоку 12 формирования управляющих импульсов. Входы блоков 19 и 20 подключены соответственно к выходам блоков 10 и 13, причем вход блока 10 формирования чисел пОдключей к выходу блока 14 сравнения циклов, вход которого соединен с выходом блока 13 формирования адресов. Блок 1 управления служит для координадни работы узлов и блоков устройства при реализации стандартных программ проверки ЗУ (обегающая 1 или О, шахматнцй порядок, и т.д.). В частности, входящий в его состав программируемый генератор 2 тактовых импульсов Предназначен для задания Периода следования указанных импульсов а блок 3 синхронизации синхронизирует работу сче1чиков 5 и 7 адресов и соответственно, регистров 17 и 18 и Яблока 13 формирования адресов. Программный блок 4 представляет собой набор N-разрядных регистров памяти и предназначен для хранения информации, необходимой для выполнения програ мы контроля параметров ЗУ. данные о реализуемом ал/ор«тме контроля, о размере контролируемого ЗУ, т.е. количестве разрядов адре|са, об области контроля ЗУ, границами которого является начальный и конечный адрес, о длительности периода следования импульров синхронизации, о величинах граничных значений считываемого сигнала О и 1 для амплитудновременного дискриминатора,о длительности управляющих импульсов и их задержке относительно импульсов синхронизации ;б длительности контролируемого параметра, например времени выборки, о порядке прохождения информации на входы контролируемого ЗУ прямой или инверсной. Ин4)О{1мащ1Я в программный блок 4 может быть занесена из ЭВМ или с пульта управления (на чертеже не показаны). 5 Счетчики 5 и 7 адресов и циклов соответ ственно представляют собой N-разрядные лвойные счетчики. Счетчик 5 предназначен для выбора ячейки и формирования кода адреса выбираемой ячейки контроля, а счет-чик 7 - для подсчета количества циклов при реализации алгоритмов контроля бегающая или О и марширующая или О. Блоки 6, 14 и 9 сравнения адресов, ujttcлов и количества циклов соответственно пре ставляют собой цифровые компараторы пора рядного сравнения двоичных чисел, причем блок 6 сравнения адресов предназначен для сравнения двоичного кода счетчика 5 адресов с кодам, задаваемым программным блоком 4, блок 14 сравнения циклов предназначен для сравнения кода счетчика 5 адресов (связь осуществляется через блок 13 формирования адресов) с кодом счетчика 7 циклов и формирования команды длА блока 10 формирования чисел на изменение, числовой информации (прямой на инверснуто или наоборот) и блока 1 управления - на изменение режима записи на считывание или наоборот, при реализации алгоритмов контроля бегающая 1 или О и марширующая Г или О. Блок 9 сравнения количества циклов пред назначен для определения момента достижения счетчиком 7 циклов адреса конечной ячейки и формирования сигнала окончание контроля в блок 3 синхронизации блока 1 упра11ления. Дещифратор 8 предназначен для управлени коммутатором 15, который осуществляет подключение выходов разрядов счетчика 5 адресов к соответствующим входам схемы ИЛИ 16 и тем самым обеспечивает прохожд iffle сигнала с выбранного разряда счетчика. 5 адресов на вход блока 10 формирования чисел, выполненного на элементе ИЛИ и двух двоичных счетчиках.... Амплитудно-временной дискриминатор 11 представляет собой два аналоговых компаратора с четырехвходовыми схемами И на выходе. Один из компараторов предназначен для сравнения амплитуды выходного уровня с заданным опорным уровнем 1, а второй - с уровнем О. Посредством схем И фиксируется момент сравнения. Блок 12 формирования управляющих импульсов выполнен на регистре, двух цифроьых компараторах и двух двоично-десятичных счетчиках. Блок 12 предназначен для формирования импульсов с заданной задерж кой относительно импульса пуска и с задан ной длительностью. Блок 13 формирования адресов представляет собой дещифратор, два инвертора и коммутатор и предназначен для выработки адреса соответствующей ячейки контроля в соответствии с заданным алгоритмом. Регистры 17 и 8 выполнены на Д-триггерах и предназначены для управления работой амплитудно-временного дискриминатора Ни блока 2 формирования управляющих импульсов соответственно. Блоки 19 и 20 регистров чисел и адреса соответственно также выполнены на Д-триггерах и служат для последовательного приёма информации контроля и последующей одновременной передачи ее на контролируемый объект, помещенный в контактный блок 21. Устройство работает следующим образом. Контроль параметров складывается из двух этапов, первый из которых является подготовительным, когда в узлы и блоки устройства заносится необходимая информация в соответствии с требуемым алгоритмом контроля. На втором этапе происходит перезапибь этой информации в Д-триггеры регистров 7 и 18 и блоков 19 и 20 регистров, передача ее на входы контролируемого объекта и собственно измерение соответствующего параметра. По сигналу разрещения от программного блока 4 на реал 1зацию требуемого алгоритма проверки на выходах блока 3 блока 1 управления устанавливаются следующие сигналы: шгнал разрешения на работу счетчика 5 адресов; запрещение работы счетчика 7 циклов; разрешение формирования сигналов записи информации посредством блока 12 формирования управляющих импульсов (сигнал из блока 3 синхронизации на вход блока 2 поступает через регистр 18), запрещение работы амплитудно-временного дискриминатора 11 (через регистр 17), разрешение на формирование адреса ячейки контроля в соответ- . ствии с реализуемым алгоритмом. По получении сигнала с блока 3 синхронизации счетчики 5 и 7 адресов и циклов устанавливаются в состояния, соответствующие коду, адреса начальной ячейки контроля. Код адреса начальной ячейки контроля с выходов разрядов счетчика 5 адресов поступает на входы блока 13 формирования адресов, который по сигналу, поступившему из блока 3 синхронизации, формирует на своих выходах адрес начальной ячейки контроля. По сигналу с программного блока 4 блок 10 формирования чисел, в соответствии с реализуемым алгоритмом проверки, формирует на выходах необходимую числовую информацию.

Таким образом .на первом подготовительIHOM, этапе ссзтцествляется формирование ин(|х)рмации контроля для записи ее в начальную ячейку памяти объекта проверки. Эта информация устанавливается на входах блоков 19 и 20 регистров чисел и адреса. Перезапись этой информации в регистры блоков 19 и 20 и вьщача ее в ячейку памяти осуществляется следующим образом.

Сигналом начало контроля от программного блока 4 осуществляется запуск програмируембго генератора 2 тактовых импульсов блока 1 управления. Генератор 2 формирует тактовы импульсы, период следования которых равен длительности адреса выбранной ячейки контроляЛер вым тактовым импульсом осуществляется перезапись информации контроля начальной ячейки в регистры блоков 19 и 20 чисел и адреса из блоков 10 и. 13 фop fйpoвaния чисел и адреса соответственно. Эта информация поступает на входы контролируемой начальной ячейки памяти объекта проверки по сигналам, вырабатываемым блоком 12 управляющих импульсов, управляемым программным блоком 4 и блоком 1 управления че рез регистр 18. Одновременно первый тактовый импульс (юступает на вход блока 3 синхронизации и тем самым создает условия для формирования информации контроля следующей ячейки памяти. При этом первый рюдготовительный, этап контроля последующей ячейки совпадает со вторым этапом контроля предыдущей.

Процесс записи информации во все ячейки памяти проверки происходит вышеописанным образом до тех пор, пока счетчик 5 адресов не установится и состояние, соответствующее коду адреса конечной ячейки памяти объекта проверки. При этом блок 6 сравнения адресов вырабатывает (Сигнал, согласно которому блок 3 синхронизащш переводит блоки устройства из режима записи в режим считьгаання информации, а счетчик 5 адресов устанавливается в состояние, соответствующее коду адреса начальной ячейки контроля.

В режиме считывания информащш блок3 синхронизации посылает через регистр 17 сигнал, разрещающий работу амплитудновременного дискриминатора 11, а через реГистр 18 - сигнал, устанавливающий блок 12 формирования управляющих импульсов в режим считывания, при котором на выходах блока 12 устанавливаются соответствующие сигналы. Амплитудно-временной дискриминатор 11 производит в кажйом цикле считывания оценку амшппудно-временных параметров объекта проверки в заданный

програм ым блоком 4 момент времени, определяемый стробимпульсом. Оценка амплитудь выходного уровня О или 1 осуществляется путем сравнения в аналоговых компараторах амплитудно-временного дискриминатора 11 с заданными программным блоком 4 опорными уровнями. При этом выходные сигналы блока 19 регистров чисел управляют работой компараторов таким образом, чтб при счить1вании амплитуд уровней О или 1 работает соответствующий компаратор. Результат контроля поступает в блок 1 управления и оттуда, при необходимости на информационную обработку.

Таким образом осуществляется запись и считывание информации из ячеек памяти проверки. При этом устройство реализует следущие алгоритмы контроля: щахматный порядок, кодовая последовательность, бегущая 1 или О, марширующая 1 или О

При реализации алгоритма контроля щахматный порядок, в блоке 10 формирования чисел включается в работу двоичный счетчик, входящий в его состав. Управление этим счетчиком осуществляется программируемым генератором 2 тактовых импульсов блока 1 управления. При этом на выходе разряда счетчика формируется код чисел О и 1. Дещифратор S, управляемый программным блоком 4, разрещает прохождение через коммутатор 15 сигналов с выхода младшего разряда строки счетчика 5 адресов. Эти сигналы через многовходовый элемент ИЛИ 6 поступают на блок 10 формирования чисел, по которым последний изменяет чередование уровней О и 1 при переходе с одиой строки на другуто в объекте проверки.

При реализации алгоритма контроля кощзъля последовательность дещифратор 8 аналогичным образом разрещает прохождение кодов адресов со счетчика 5 на блока 10 формирования чисел.

При реализации алгоритмов бегущая 1 или О, марщирующая 1 или О производится запись 1 или О соответственно во все ячейки памяти объекта проверки вышописанным образом. По окончании записи блок 14 сравнения циклов формирует сигнал равенства кодов, установленных на выходах разрядов счетчиков 5 и 7 адресов и циклов соответственно, по получении которого блок 10 формирования чисел вырабатывает инверсную информацию, а блок 3 синхронизации блока 1 управления формирует сигнал на разрешение записи этой информации в начальную ячейку памяти, после чего устройство переходит в режим считывания информации из ячеек памяти. Этот процесс происходит до тех пор, пока блок 14 сравнения циклов не зафиксирует момент равенства кодов на выходах счетчиков 5 и 7 адресов и циклов соответственно. В момент равенства указанных кодов в режиме считывания блок 14 сравнения циклов формирует сигнал, по которому блок синхронизации вырабатывает сигналы на увеличение содер сйй го счетчика 7 циклов на единицу. При этом содержимое счетчика 5 адресов не изменяется. Устройство снова переводится в режим записи информации, причем блок 10 формирования чисел вырабатывает прямую информацню, которая записывается в адрес начальной ячейки памяти. Блок 3 синхронизации блока 1 разрешает работу счетчика 5 адресов. Содер жимое последнего увеличивается на едини1Цу, блок 14 сравнения циклов фиксирует равенство кодов счетчиков 5 и 7 адресов и циклов по адресу второй ячейки памяти. Так же осуществляется запись инверсной информа1ЩИ во вторую ячейку, после чего устройство снова аналогичным образом переводится в режим считывания. Дальнейшая работа устройства при реализации алгоритмов бегущая 1 или О, осуществляется вышеописанным образом до тех пор, пока на выходе счетчика 7 циклов не установится код адреса коне% ной ячейки, что фиксируется блоком 9 сравнения количества циклов, который фopмиpyet сигнал для блока 3 синхронизации. При одновременном получении сигналов с блоков 6 и 9 сравнения адресов и циклов соответственно блок 3 синхронизации по окончании режима считывания формирует сигнал окончание контроля. Формулаизобретения , j Устройство для контроля блоков памяти, содержащее блок управления, подключенный выходами к программному блоку, счетчикам адресов и циклов и блоку формирования адресов, а входами - к блокам сравнения адресов и количества циклов и амплитудновременному дискриминатору, входы которого подключены к контактному блоку и программному блоку, связанному своими выходами со входами счетчика адресов, блоков сравнения адресов и количества циклов и блоков формирования чисел и управляющих импульсов причем последний своими выходами связан с контактным блоком, дешифратор, коммутатор, блок сравнения циклов, выход которого подключен к блоку формирования чисел, а входы связаны со счетчиком циклов, имеющим двустороннюю связь с блоком сравнения количества циклов, а через блок формирования адресов - со счетчиком адресов, имеющим двустороннюю связь с блоком сравнения адресов, отличающееся тем, что, с целью повышения точности контроля, введены блоки регистров адреса и «шсел, многовходовой элемент ИЛИ и два регистра, первые входы которых и блоков регистров адреса и чисел объединены и подключенй к блоку управления, вторые входы регистров раздельно подключены к блоку управления, выход первого регистра подключен ко входу амплитудно-временного дискриминатора, выход второго регистра - ко входу блока формирования управляющих импульсов, вторые входы блока регистров адреса подключены к блоку формирования адреса, а вь1ходы - к контактному блоку, выходы блока регистров чисел подключены к контактному блоку и амплитудио-временному дискриминатору, а его вторые входы к блоку формирования чисел, вход которого подключен к выходу многовходового элемента ИЛИ, связанного своими входами с коммутатором, первые входы которого подключены к выходам счетчика адресов, связанным со входами блока формирования адресов, а вторые входы через дешифратор подключены к программному блоку. . Источники информации, аршятые во внимание при экспертизе 1.Авторское свидетельство СССР N« 471560, кл. G 01 R 31/28, 1976. 2.Авторское свидетельство СССР N 526954, кл..6 01 R 29/00, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Генератор случайного процесса | 1982 |

|

SU1020820A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| Устройство для контроля блоков памяти | 1975 |

|

SU526954A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ ГРУППОЙ ЕДИНИЦ ТЕХНОЛОГИЧЕСКОГО ОБОРУДОВАНИЯ | 1991 |

|

RU2020537C1 |

Авторы

Даты

1980-02-25—Публикация

1978-04-04—Подача