I

Изобретение относится к автома- .тизированным системам контроля и предназначено для контроля больших и сверхбольших интегральных схем (БИС и СБИС) на функционирование при их массовом производстве.

Целью изобретения является повышение достоверности контроля БИС и СБИС путем выравнивания временных диаграмм каналов за счет привязки по времени всех каналов устройства к параметрам импульса, принятого з эталонный.

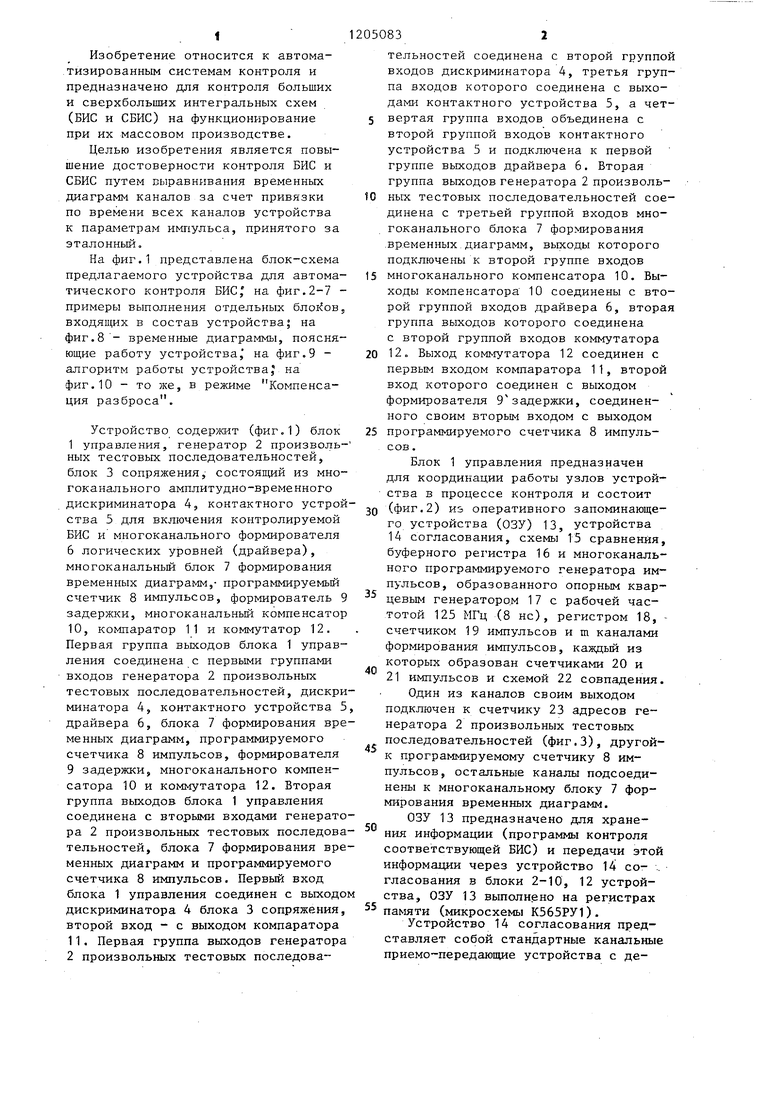

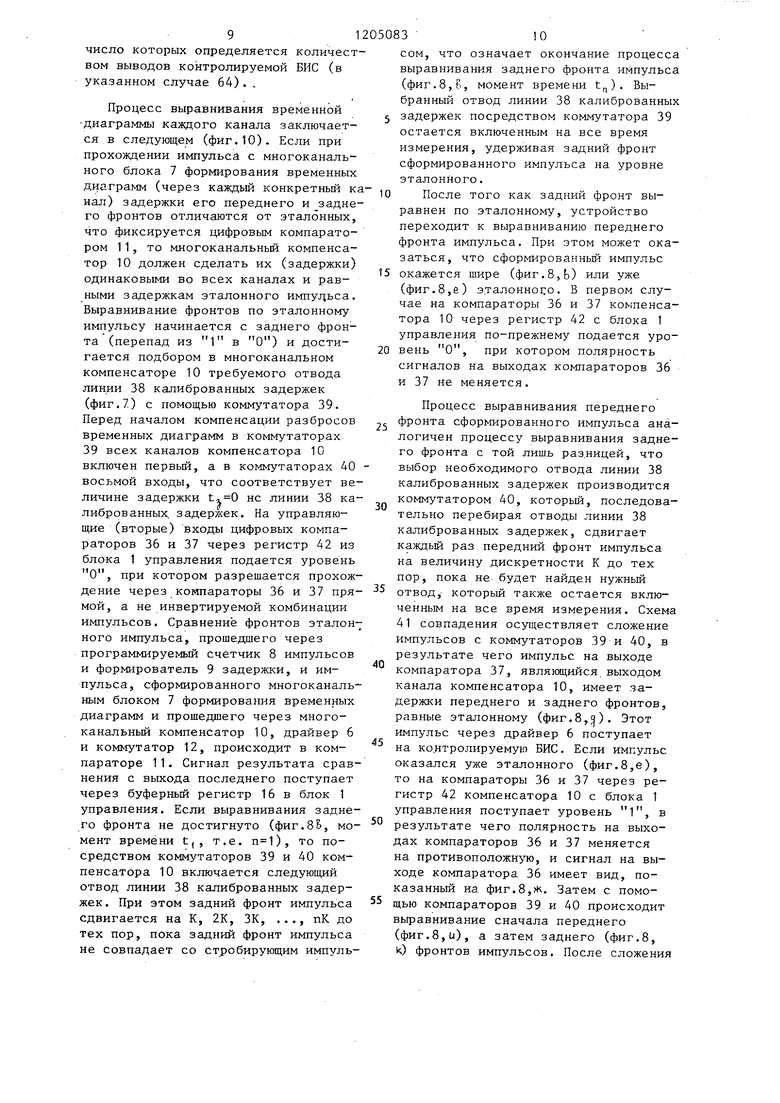

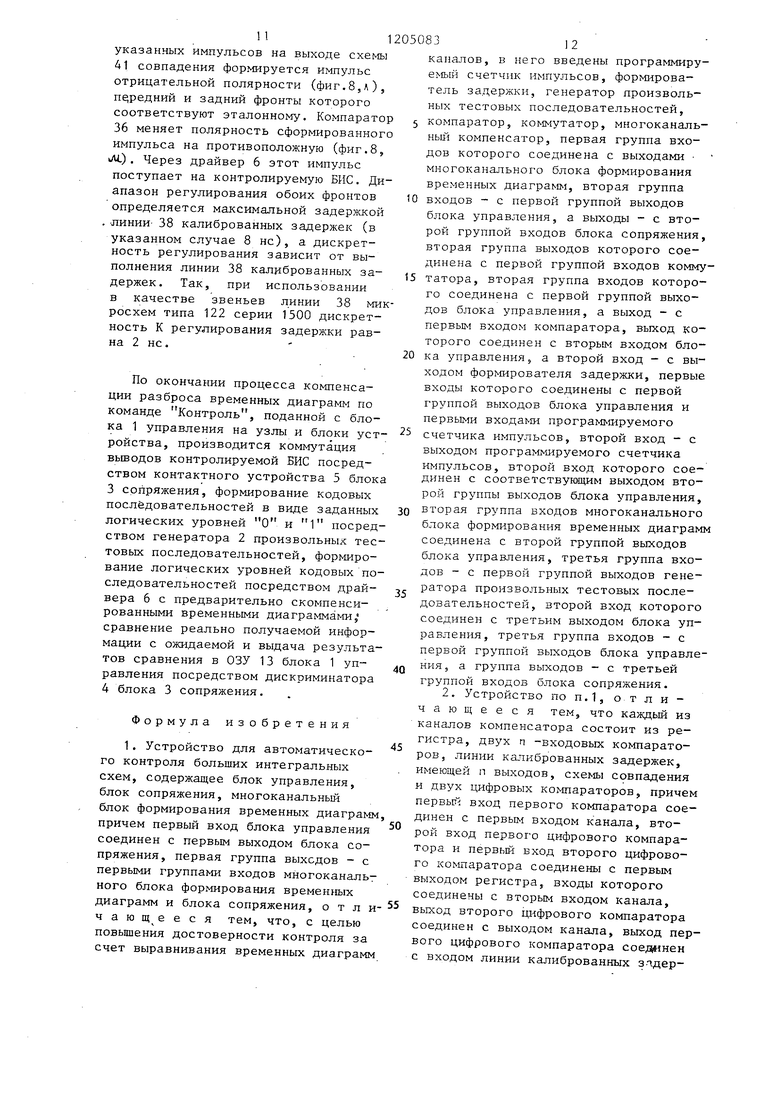

На фиг.1 представлена блок-схем предлагаемого устройства для автомтического контроля БИС на фиг,2-7 примеры выполнения отдельных входящих в состав устройства; на фиг.8- временные диаграммы, пояснющие работу устройства, на фиг. 9 - алгоритм работы устройства, на фиг.10 - то же, в режиме Компенсация разброса.

Устройство содержит (фиг.1) блок

1управления, генератор 2 произволь- ных тестовых последовательностей, блок 3 сопряжения, состоящий из многоканального амплитудно-временного дискриминатора 4, контактного устройства 5 для включения контролируемой БИС и многоканального формирователя

6 логических уровней (драйвера), многоканальный блок 7 формирования временных диаграмм,- программируемый счетчик 8 импульсов, формирователь 9 задержки, многоканальный компенсатор

10,компаратор 11 и коммутатор 12. Первая группа выходов блока 1 управления соединена с первыми группами входов генератора 2 произвольных тестовых последовательностей, дискриминатора 4, контактного устройства 5, драйвера 6, блока 7 формирования временных диаграмм, программируемого счетчика 8 импульсов, формирователя

9 задержки, многоканального компенсатора 10 и коммутатора 12. Вторая группа выходов блока 1 управления соединена с вторыми входами генератора 2 произвольных тестовых последовательностей, блока 7 формирования временных диаграмм и программируемого счетчика 8 импульсов. Первый вход блока 1 управления соединен с выходом дискриминатора 4 блока 3 сопряжения, второй вход - с выходом компаратора

11.Первая группа выходов генератора

2произвольньпс тестовых последова

0

тельностей соединена с второй группой входов дискриминатора 4, третья группа входов которого соединена с выходами контактного устройства 5, а четвертая группа входов объединена с второй группой входов контактного устройства 5 и подключена к первой группе выходов драйвера 6. Вторая группа вьпсодов генератора 2 произвольных тестовых последовательностей соединена с третьей группой входов многоканального блока 7 формирования временных.диаграмм, выходы которого подключены к второй группе входов многоканального компенсатора 10. Выходы компенсатора 10 соединены с второй группой входов драйвера 6, вторая группа выходов которого соединена с второй группой входов коммутатора 12„ Выход коммутатора 12 соединен с первым входом компаратора 11, второй вход которого соединен с выходом формирователя 9 задержки, соединенного своим вторьм входом с выходом

5 программируемого счетчика 8 импульсов .

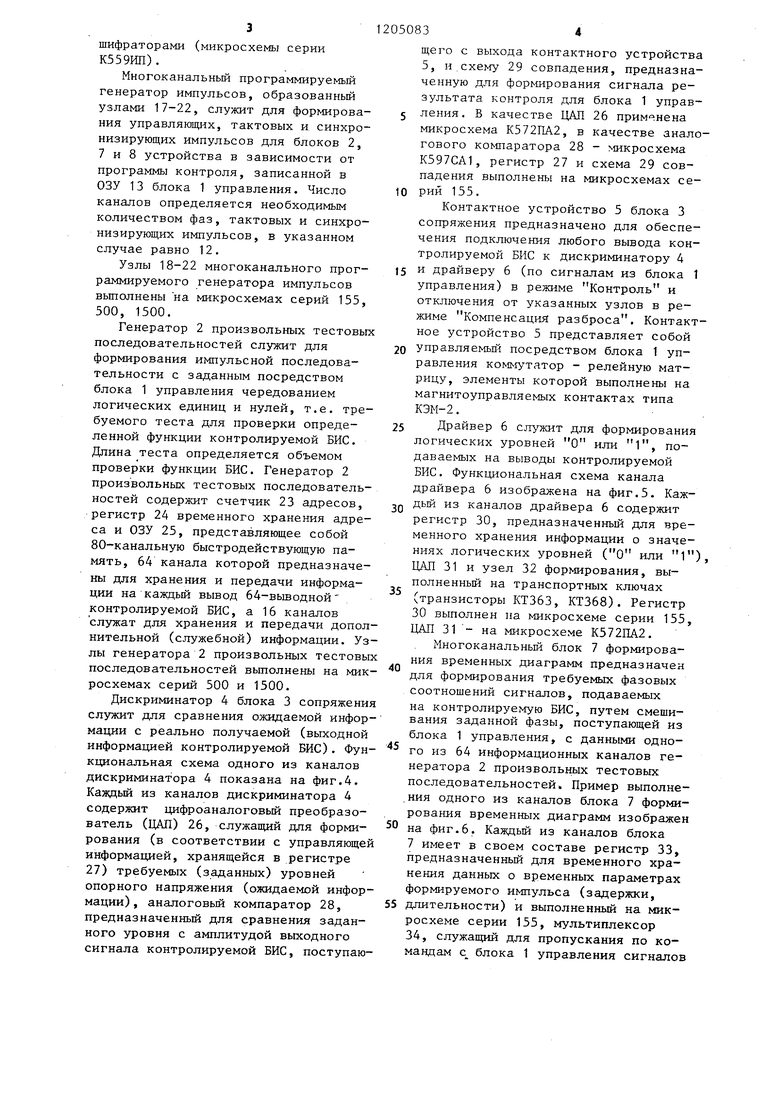

Блок 1 управления предназначен для координации работы узлов устройства в процессе контроля и состоит

0 (фиг.2) из оперативного запоминающего устройства (ОЗУ) 13, устройства 14 согласования, схемы 15 сравнения, буферного регистра 16 и многоканального программируемого генератора импульсов, образованного опорным кварцевым генератором 17 с рабочей частотой 125 МГц (8 не), регистром 18, - счетчиком 19 импульсов и m каналами формирования импульсов, каждый из которых образован счетчиками 20 и 21 импульсов и схемой 22 совпадения.

Один из каналов своим выходом подключен к счетчику 23 адресов генератора 2 произвольных тестовых последовательностей (фиг.З), другой- к программируемому счетчику 8 импульсов , остальные каналы подсоединены к многоканальному блоку 7 формирования временных диаграмм.

ОЗУ 13 предназначено для хранения информации (программы контроля соответствующей БИС) и передачи этой информации через устройство 14 со- .. гласования в блоки 2-10, 12 устройства, ОЗУ 13 выполнено на регистрах

памяти (микросхемы К565РУ1).

Устройство 14 согласования представляет собой стандартные канальные приемо-передающие устройства с де5

0

5

0

шифраторами (микросхемы серии К559ИП).

Многоканальный программируемый генератор импульсов, образованный узлами 17-22, служит для формирования управляющих, тактовых и синхронизирующих импульсов для блоков 2, 7 и 8 устройства в зависимости от программы контроля, записанной в ОЗУ 13 блока 1 управления. Число каналов определяется необходимым количеством фаз, тактовых и синхронизирующих импульсов, в указанном случае равно 12.

Узлы 18-22 многоканального программируемого генератора импульсов вьтолнены на микросхемах серий 155, 500, 1500.

Генератор 2 произвольных тестовых последовательностей служит для формирования импульсной последовательности с заданным посредством блока 1 управления чередованием логических единиц и нулей, т.е. требуемого теста для проверки определенной функции контролируемой БИС. Длина теста определяется объемом проверки функции БИС. Генератор 2 произвольных тестовых последовательностей содержит счетчик 23 адресов, регистр 24 временного хранения адреса и ОЗУ 25, представляющее собой 80-канальную быстродействующую память, 64 канала которой предназначены для хранения и передачи информации на каждый вывод 64-вьшодной контролируемой БИС, а 16 каналов служат для хранения и передачи дополнительной (служебной) информации. Узлы генератора 2 произвольных тестовы последовательностей выполнены на микросхемах серий 500 и 1500.

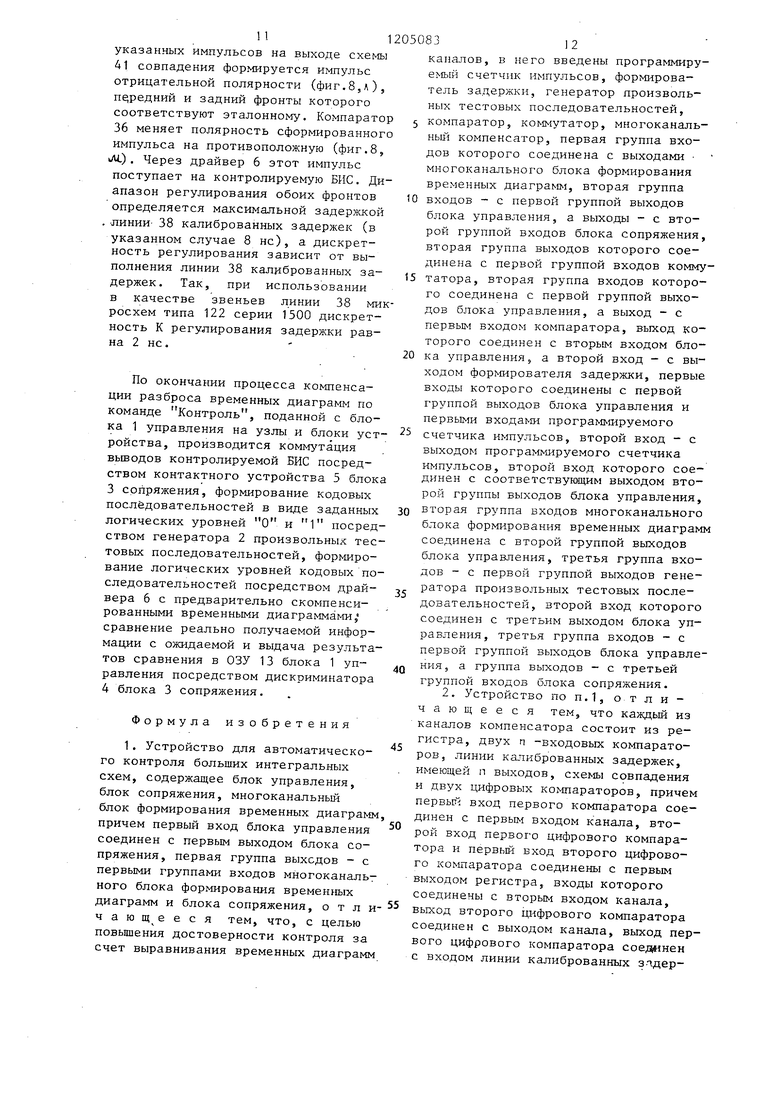

Дискриминатор 4 блока 3 сопряжени служит для сравнения ожидаемой информации с реально получаемой (выходной информацией контролируемой БИС). Функциональная схема одного из каналов дискриминатора 4 показана на фиг.4. Каждый из каналов дискриминатора 4 содержит цифроаналогоный преобразователь (ЦАП) 26, служащий для формирования (в соответствии с управляюще информацией, хранящейся в регистре 27) требуемых (заданных) уровней опорного напряжения (ожидаемой информации) , аналоговый компаратор 28, предназначенный для сравнения заданного уровня с амплитудой выходного сигнала контролируемой БИС, поступаюяй2050834

щего с выхода контактного устройства 5, и схему 29 совпадения, предназначенную для формирования сигнала результата контроля для блока 1 управ- с ления. Б качестве ЦАП 26

10

15

20

25

30

35

40

50

- микросхема схема 29 совпримо-нена

микросхема K572IIA2, в качестве аналогового KohfflapaTopa 28 К597СА1, регистр 27 и падения выполнены на микросхемах серий 155.

Контактное устройство 5 блока 3 сопряжения предназначено для обеспечения подключершя любого вывода контролируемой БИС к дискриминатору 4 и драйверу 6 (по сигналам из блока 1 управления) в режиме Контроль и отключения от указанных узлов в режиме Компенсация разброса. Контактное устройство 5 представляет собой управляемьш посредством блока 1 управления KONtNtyTaTop - релейную матрицу, элементы которой выполнены на магнитоуправляемых контактах типа КЭМ-2.

Драйвер 6 слзгйсит для формирования логических уровней О или 1, подаваемых на выводы контролируемой БИС. Функциональная схема канала драйвера 6 изображена на фиг.5. Каж- дьй из каналов драйвера 6 содержит регистр 30, предназначенный для временного хранения информации о значениях логических уровней (О или 1), ЦАП 31 и узел 32 формирования, выполненный на транспортных ключах (транзисторы КТ363, КТ368). Регистр 30 выполнен на микросхеме серии 155, ЦАП ЗГ- на микросхеме K572IIA2.

Многоканальный блок 7 формирования временных диаграмм предназначен для формирования требуемых фазовых соотношений сигналов, подаваемых

на контролируемую БИС, путем смешивания заданной фазы, поступающей из блока 1 управления, с данными одно го из 64 информационных каналов генератора 2 произвольных тестовых последовательностей. Пример выполнения одного из каналов блока 7 формирования временных диаграмм изображен на фиг.6. Каждьй из каналов блока 7 имеет в своем составе регистр 33, предназначенный для временного хранения данных о временных параметрах формируемого импульса (задержки,

55 длительности) и выполненный на микросхеме серии 155, мультиплексор 34, служащий для пропускания по командам с блока 1 управления сигналов

заданной фазы на схему 35 совпадения, выполненную на логических элементах ИЛИ-НЕ. Узлы 34 и 35 многоканального блока 7 формирования вре- манных диаграмм выполнены на микросхемах серии 1500 (1500 ИД 163, 1500 ЛМ 102).

Программируемый счетчик 8 импульсов предназначен для формирования задержки строб-импульса с дискретностьк, равной периоду опорного кварцевого генератора 17 блока 1 управления (8 не) и выполнен на микросхемах серии 500.

, Формирователь 9 задержки служит для формирования эталонной задержки строб-импульса с дискретностью

Д 0,1 НС и построен по широко известному стробоскопическому принципу, основанному на применении генератора пилообразного напряжения и компаратора, сравнивающего мгновенное значение пилообразного напряжения и опорного уровня, изменение которого изменяет задержку момента сравнения указанных напряжений и, следовательно, задержку выходного импульса компаратора, т.е. всего формирователя 9 задержки.

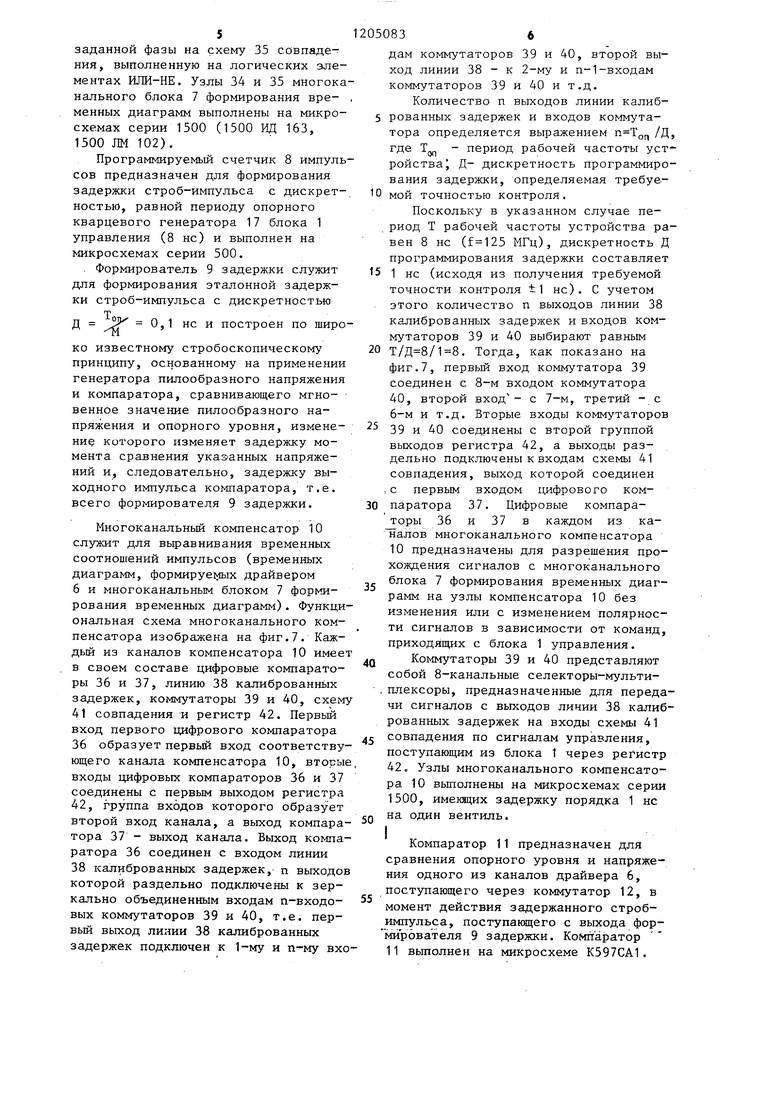

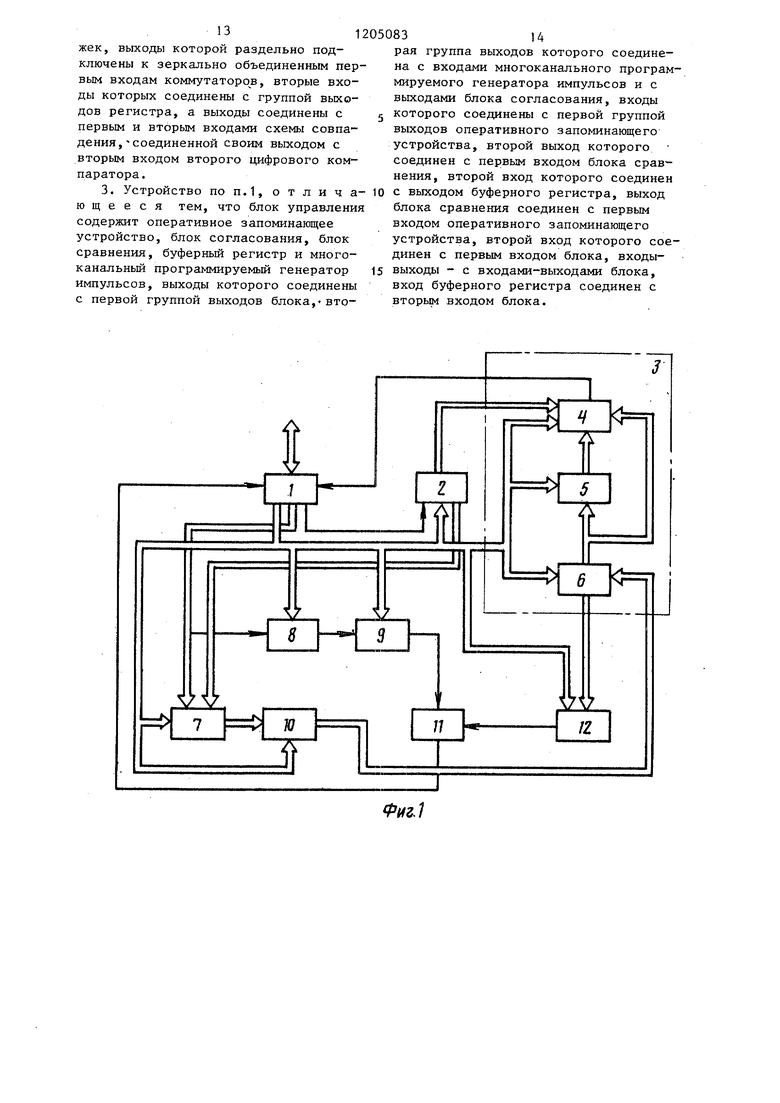

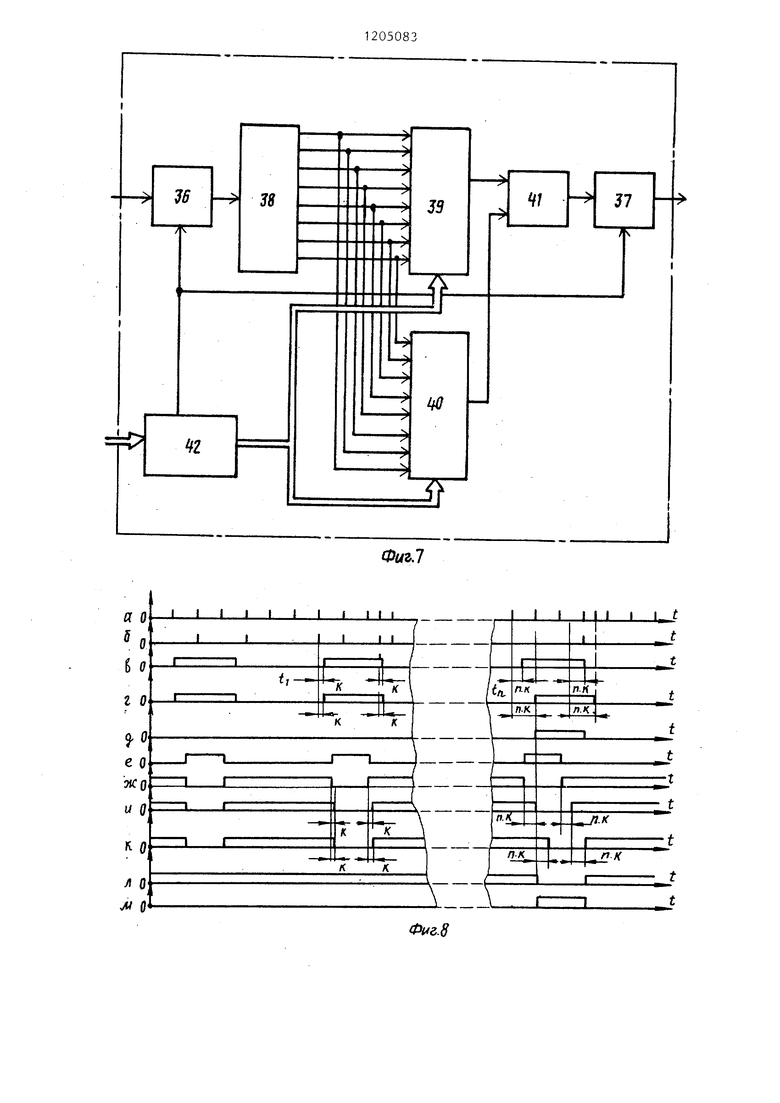

Многоканальньй компенсатор 10 служит для вьфавнивания временных соотношений импульсов (временных диаграмм, формируемых драйвером 6 и многоканальным блоком 7 формирования временных диаграмм). Функциональная схема многоканального компенсатора изображена на фиг.7. Каждый из каналов компенсатора 10 имеет в своем составе цифровые компараторы 36 и 37, линию 38 калиброванн;ь1х задержек, коммутаторы 39 и 40, схему 41 совпадения и регистр 42. Первый вход первого цифрового компаратора 36 образует первьй вход соответствующего канала компенсатора 10, вторые входы цифровых компараторов 36 и 37 соединены с первым выходом регистра 42, г руппа входов которого образует второй вход канала, а выход компаратора 37 - выход канала. Выход компаратора 36 соединен с входом линии 38 калиброванных задержек,- п выходов которой раздельно подключены к зеркально объединенным входам п-входо- вых коммутаторов 39 и 40, т.е. первый выход линии 38 калиброванных задержек подключен к 1-му и п-му вхо12050836

дам коммутаторов 39 и 40, второй выход линии 38 - к 2-му и п-1-входам коммутаторов 39 и 40 и т.д.

Количество п выходов линии калиб- i рованных задержек и входов коммутатора определяется выражением , где Тд - период рабочей частоты устройства j Д- дискретность программирования задержки, определяемая требуемой точностью контроля.

Поскольку в указанном случае период Т рабочей частоты устройства равен 8 НС ( МГц), дискретность Д программирования задержки составляет

1 НС (исходя из получения требуемой точности контроля ±1 не). С учетом этого количество п выходов линии 38 калиброванных задержек и входов коммутаторов 39 и 40 выбирают равным

. Тогда, как показано на фиг.7, первый вход коммутатора 39 соединен с 8-м входом коммутатора 40, второй с 7-м, третий - с 6-м и т.д. Вторые входы коммутаторов

39 и 40 соединены с второй группой выходов регистра 42, а выходы раздельно подключены к входам схемы 41 совпадения, выход которой соединен ,с первым входом цифрового компаратора 37. Пифровые компараторы 36 и 37 в каждом из ка- Налов многоканального компенсатора 10 предназначены для разрешения про- хозвдения сигналов с многоканального блока 7 формирования временных диаграмм на узлы компенсатора 10 без изменения или с изменением полярности сигналов в зависимости от команд, приходящих с блока 1 управления. Коммутаторы 39 и 40 представляют собой 8-канальные селекторы-мульти- плексоры, предназначенные для передачи сигналов с выходов линии 38 калиброванных задержек на входы схемы 41 совпадения по сигналам управления, поступающим из блока 1 через регистр 42 о Узлы многоканального компенсатора 10 выполнены на микросхемах серии 1500, имекяцих задержку порядка 1 не на один вентиль.

55

Компаратор 11 предназначен для сравнения опорного уровня и напряжения одного из каналов драйвера 6, поступающего через коммутатор 12, в момент действия задержанного строб- импульса, поступающего с выхода фор- мирователя 9 задержки. Компаратор 11 вьшолнен на микросхеме К597СА1.

Коммутатор 12 представляет собой компактную высокочастотную релейную матрицу, предназначенную для коммутации 64 выходов драйвера 6 на общий вход компаратора 11. В качестве элементов коммутатора 12 применены маг- нитоуправляемые контакты типа КЭМ-2.

Устройство работает следующим образом.

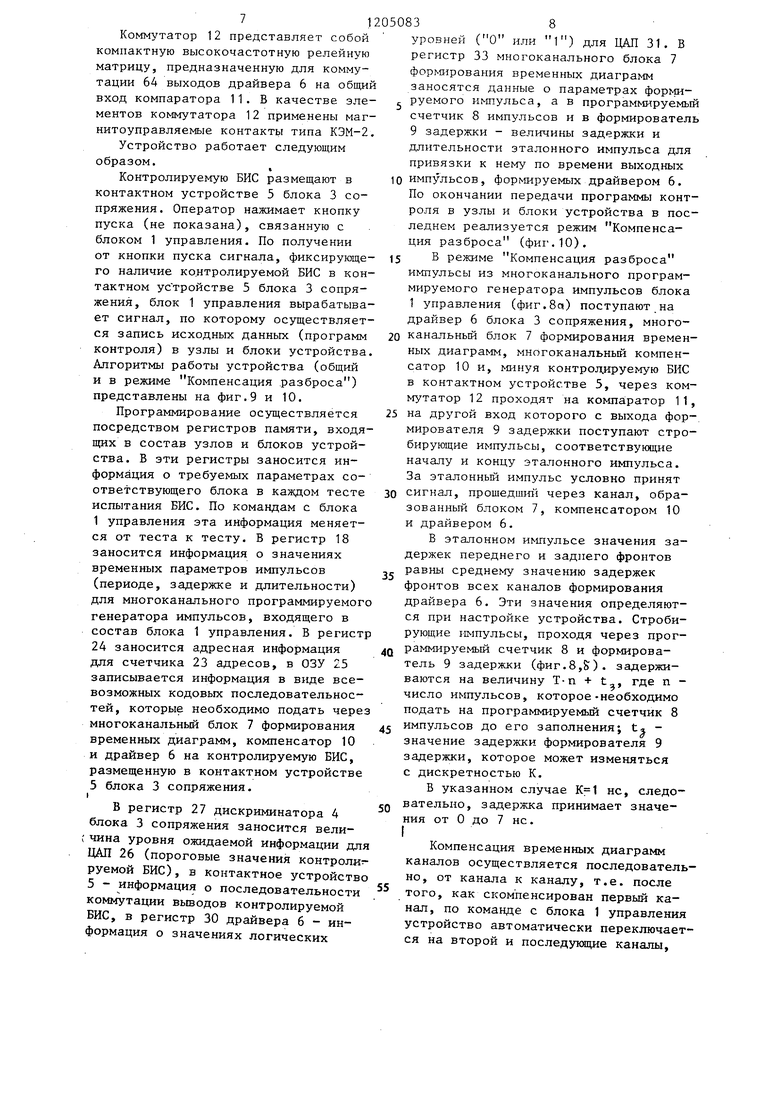

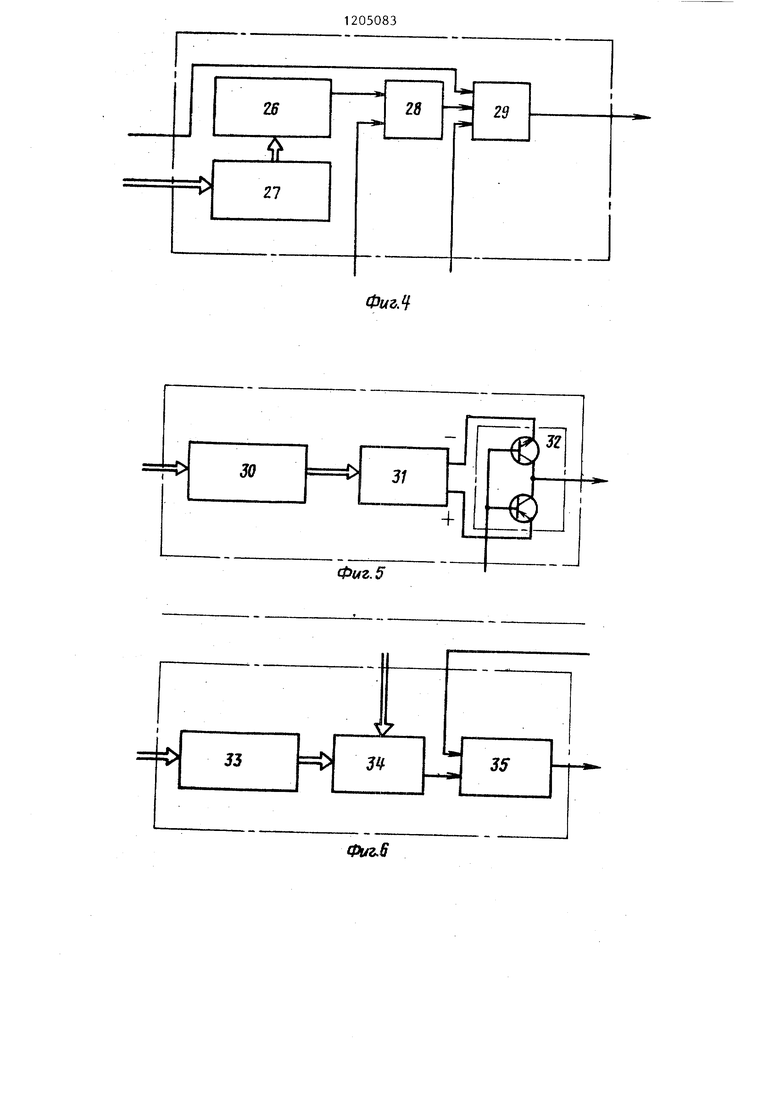

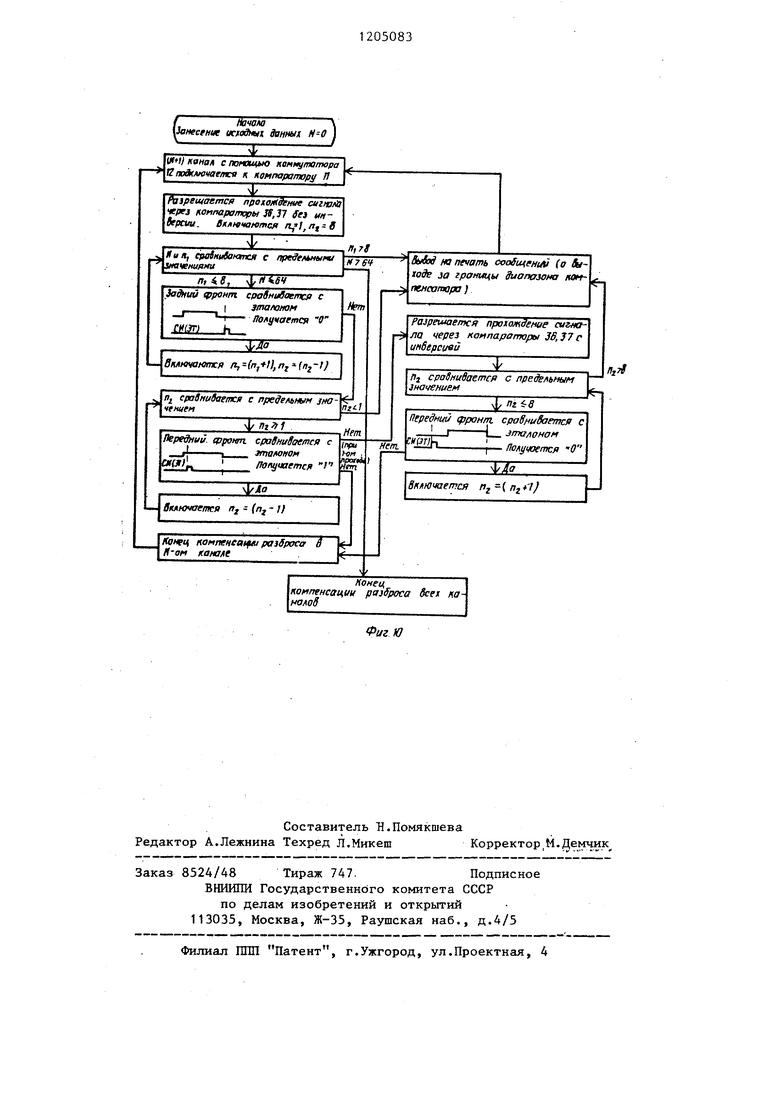

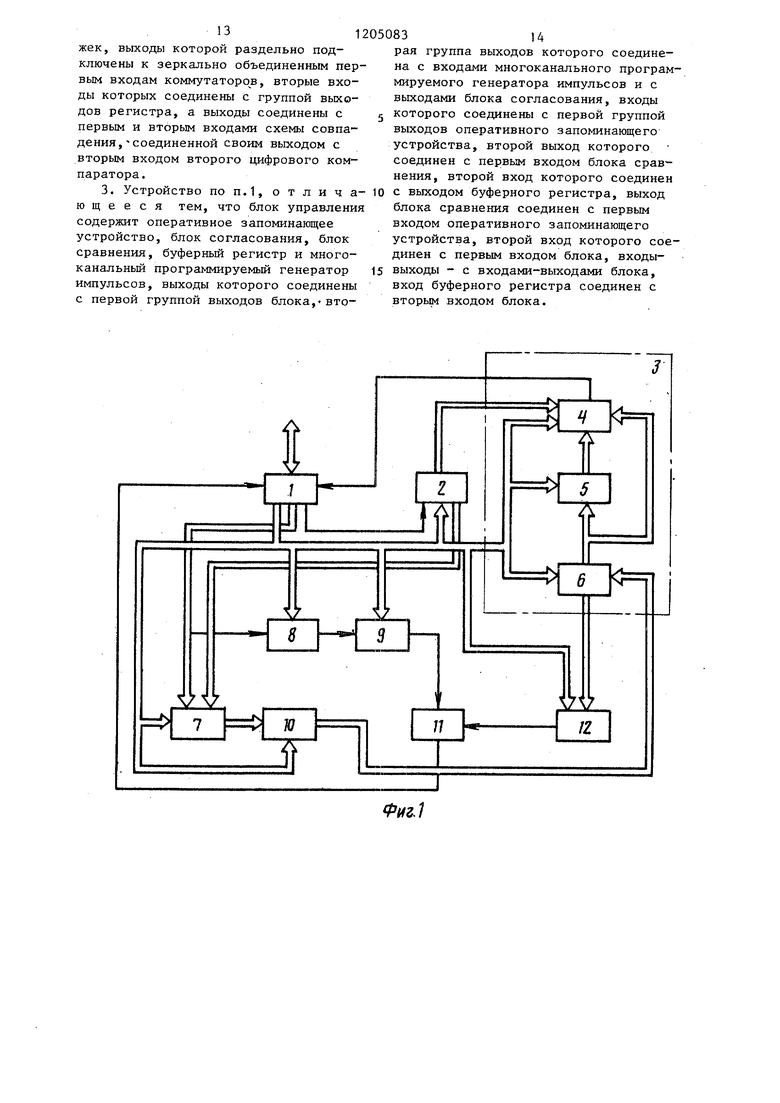

Контролируемую БИС размещают в контактном устройстве 5 блока 3 сопряжения. Оператор нажимает кнопку пуска (не показана), связанную с блоком 1 управления. По получении от кнопки пуска сигнала, фиксирующего наличие контролируемой БИС в контактном ус тройстве 5 блока 3 сопряжения, блок 1 управления вырабатывает сигнал, по которому осуществляется запись исходных данных (программ контроля) в узлы и блоки устройства Алгоритмы работы устройства (общий и в режиме Компенсация разброса) представлены на фиг.9 и 10.

Программирование осуществляется посредством регистров памяти, входящих в состав узлов и блоков устройства. В эти регистры заносится информация о требуемых параметрах соответствующего блока в каждом тесте испытания БИС. По командам с блока 1 управления эта информация меняется от теста к тесту. В регистр 18 заносится информация о значениях временных параметров импульсов (периоде, задержке и длительности) для многоканального программируемого генератора импульсов, входящего в состав блока 1 управления. В регистр 24 заносится адресная информация для счетчика 23 адресов, в ОЗУ 25 записывается информация в виде всевозможных кодовых последовательностей, которые необходимо подать через многоканальный блок 7 формирования временных диаграмм, компенсатор 10 и драйвер 6 на контролируемую БИС, размещенную в контактном устройстве

5 блока 3 сопряжения. I

В регистр 27 дискриминатора 4 блока 3 сопряжения заносится вели- ; чина уровня ожидаемой информации для ЦАП 26 (пороговые значения контролиг руемой БИС), в контактное устройство 5 - информация о последовательности коммутации вьшодов контролируемой БИС, в регистр 30 драйвера 6 - информация о значениях логических

уровней (О или 1) для ЦАП 31. В регистр 33 многоканального блока 7 формирования временных диаграмм заносятся данные о параметрах руемого и myльca, а в программируемый

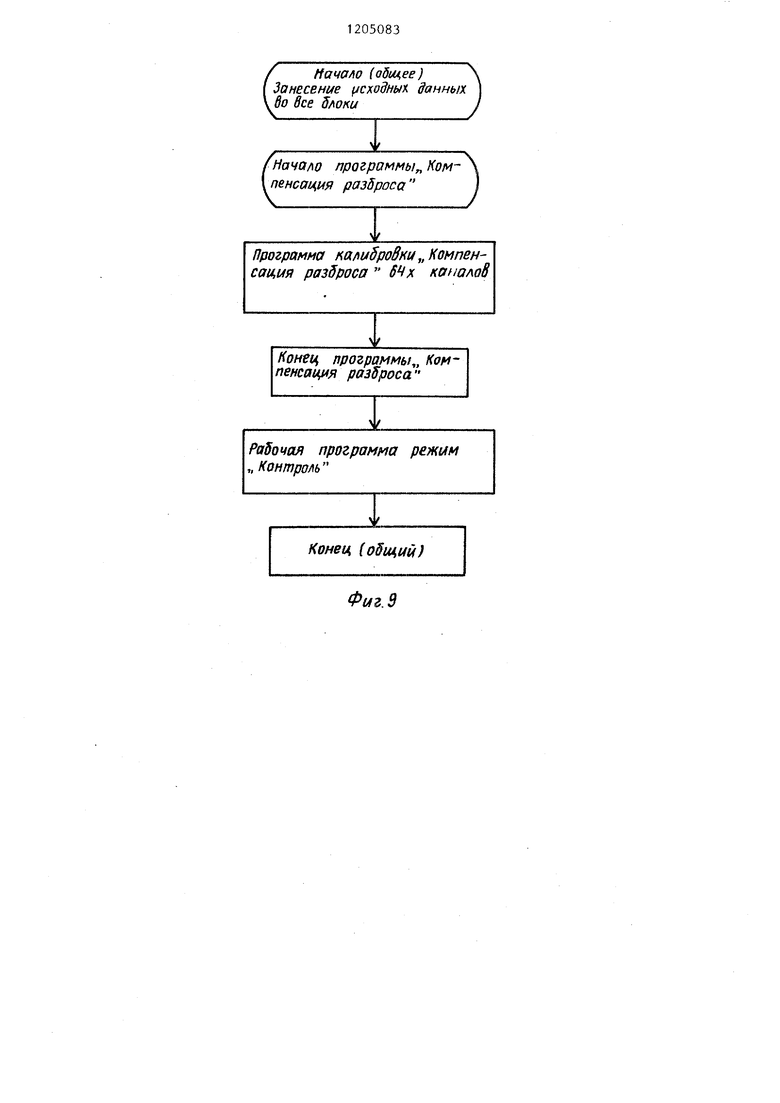

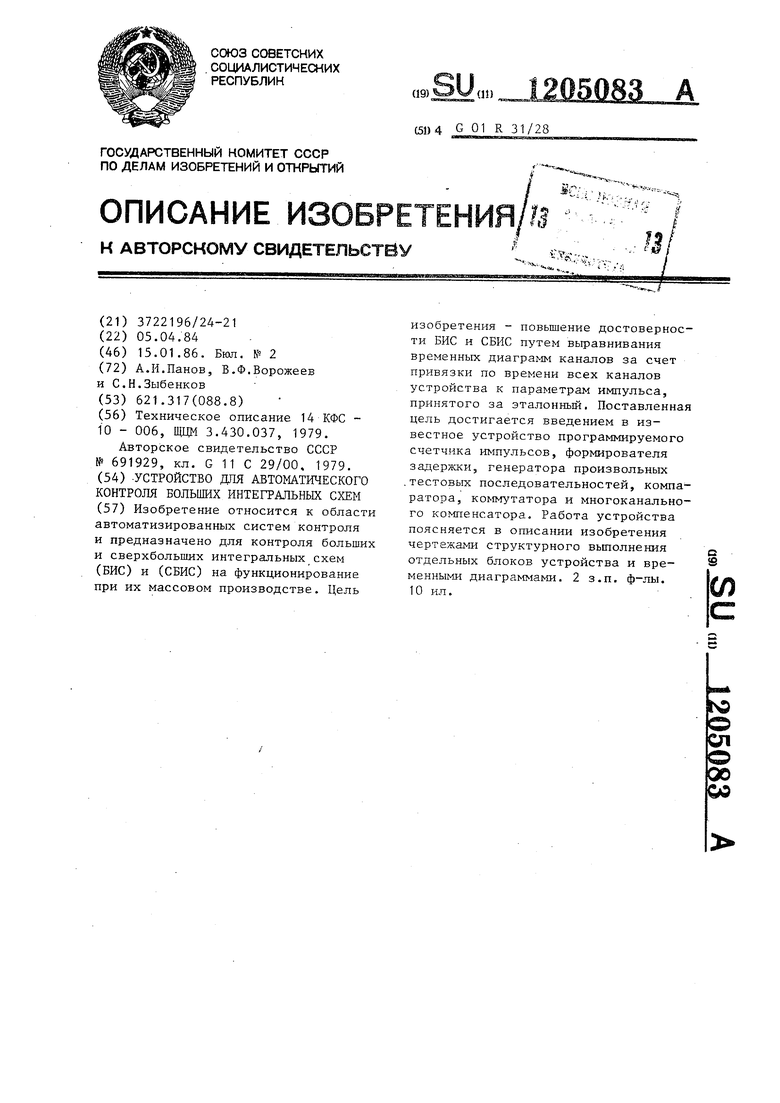

счетчик 8 импульсов и в формирователь 9 задержки - величины задержки и длительности эталонного импульса для привязки к нему по времени выходных 0 импульсов, формируемых драйвером 6. По окончании передачи программы контроля в узлы и блоки устройства в последнем реализуется режим Компенсация разброса (фиг,10). 5 В режиме Компенсация разброса импульсы из многоканального программируемого генератора импульсов блока 1 управления (фиг.8с() поступают на драйвер 6 блока 3 сопряжения, много- 0 канальный блок 7 формирования временных диаграмм, многоканальный компенсатор 10 и, минуя контролируемую БИС в контактном устройстве 5, через коммутатор 12 проходят на компа ратор 11, 5 на другой вход которого с выхода формирователя 9 задержки поступают стро- бирующие импульсы, соответствукнцие началу и концу эталонного импульса. За эталонньм импульс условно принят 0 сигнал, прошедш1-ш через канал, образованный блоком 7, компенсатором 10 и драйвером 6.

В эталонном импульсе значения задержек переднего и заднего фронтов равны среднему значению задержек фронтов всех каналов формирования драйвера 6. Эти значения определяются при настройке устройства. Строби- рующие импульсы, проходя через прог- Q раммируемый счетчик 8 и формирователь 9 задержки (фиг.8,&). задерживаются на величину Т-п + t, где п - число импульсов, которое-необходимо подать на программируемый счетчик 8 2 импульсов до его заполнения; t, - значение задержки формирователя 9 задержки, которое может изменяться с дискретностью К.

В указанном случае не, следо- Q вательно, задержка принимает значения от О до 7 НС. I

Компенсация временных диаграмм каналов осуществляется последовательно, от канала к каналу, т.е. после того, как скомпенсирован первый канал, по команде с блока 1 управления устройство автоматически переключается на второй и последукяцие каналы,

5

число которых определяется количеством выводов контролируемой БИС (в указанном случае 64).,

Процесс выравнивания временной диаграммы каждого канала заключается в следующем (фиг.10). Если при прохождении импульса с многоканального блока 7 формирования временных диаграмм (через каждый конкретньш ка нал) задержки его переднего и заднего фронтов отличаются от эталонных, что фиксируется цифровым компаратором 11, то многоканальньй компенсатор 10 должен сделать их (задержки) одинаковыми во всех каналах и равными задержкам эталонного импудьса. Выравнивание фронтов по эталонному импульсу начинается с заднего фронта (перепад из 1 в О) и достигается подбором в многоканальном компенсаторе 10 требуемого отвода линии 38 калиброванных задержек (фиг. 7.) с помощью коммутатора 39, Перед началом компенсации разбросов временных диаграмм в коммутаторах 39 всех каналов компенсатора 10 включен первый, а в коммутаторах 40 восьмой входы, что соответствует величине задержки не линии 38 ка

НС

либрованных. задержек. На управляющие (вторые) входы цифровых компараторов 36 и 37 через регистр 42 из блока 1 управления подается уровень О, при котором разрешается прохождение через компараторы 36 и 37 прямой, а не инвертируемой комбинации импульсов. Сравнение фронтов эталонного импульса:, прошедшего через программируемый счетчик 8 импульсов и формирователь 9 задержки, и импульса, сформированного многоканальным блоком 7 формирования временных диаграмм и прошедшего через многоканальный компенсатор 10, драйвер 6 и коммутатор 12, происходит в компараторе 11. Сигнал результата сравнения с выхода последнего поступает через буферный регистр 16 в блок 1 управления. Если выравнивания заднего фронта не достигнуто (фиг.8&, момент времени t,, т.е. ), то посредством коммутаторов 39 и 40 компенсатора 10 включается следующий отвод линии 38 калиброванных задержек. При этом задний фронт импульса сдвигается на К, 2К, ЗК, ..., пК до тех пор, пока задний фронт импульса не совпадает со стробирующим импуль

сом, что означает окончание процесса выравнивания заднего фронта импульса (фиг.8,ь, момент времени t,). Выбранный отвод линии 38 калиброванных задержек посредством коммутатора 39 остается включенным на все время измерения, удерживая задний фронт сформированного импульса на уровне эталонного.

После того как задний фронт выравнен по эталонному, устройство переходит к выравниванию переднего фронта импульса. При этом может оказаться, что сформированный импульс окажется шире (фиг.8,Ь) или уже

(фиг.8,е) эталонно1;о. В первом случае на компараторы 36 и 37 компенсатора 10 через регистр 42 с блока 1 управления по-прежнему подается уровень О, при котором полярность сигналов на выходах компараторов 36 и 37 не меняется.

Q

0

5

0

Процесс выравнивания переднего с фронта сформированного импульса аналогичен процессу выравнивания заднего фронта с той лишь раз.нидей, что выбор необходимого отвода линии 38 калиброванных задержек производится коммутатором 40, который, последовательно перебирая отводы линии 38 калиброванных задержек, сдвигает каждый раз передний фронт импульса на величину дискретности К до тех пор, пока не будет найден нужный отвод,- который также остается включенным на все время измерения. Схема 41 совпадения осуществляет сложение импульсов с коммутаторов 39 и 40, в результате чего импульс на выходе компаратора 37, являющийся выходом канала компенсатора 10, имеет задержки переднего и заднего фронтов, равные эталонному (фиг.8,). Этот импульс через драйвер 6 поступает на контролируемую БИС. Если импульс оказался уже эталонного (фиг.8,е), то на компараторы 36 и 37 через регистр 42 компенсатора 10 с блока 1 управления поступает уровень 1, в результате чего полярность на выходах компараторов 36 и 37 меняется на противоположную, и сигнал на выходе компаратора 36 имеет вид, показанный на фиг.8,к. Затем с помощью компараторов 39 и 40 происходит выравнивание сначала переднего (фиг.8,и), а затем заднего (фиг.8, k) фронтов импульсов. После сложения

5

10

15

20

указанных импульсов на выходе схемы 41 совпадения формируется импульс отрицательной полярности (фиг.8,л), передний и задний фронты которого соответствуют эталонному. Компаратор 36 меняет полярность сформированного импульса на противоположную (фиг.8, С) . Через драйвер 6 этот импульс поступает на контролируемую БИС. Диапазон регулирования обоих фронтов определяется максимальной задержкой -линии- 38 калиброванных задержек (в указанном случае 8 не), а дискретность регулирования зависит от выполнения линии 38 калиброванных задержек. Так, при использовании в качестве звеньев линии 38 микросхем типа 122 серии 1500 дискретность К регулирования задержки равна 2 не .

По окончании процесса компенсации разброса временных диаграмм по команде Контроль, поданной с блока 1 управления на узлы и блоки уст- ройства, производится коммутация вьшодов контролируемой БИС посредством контактного устройства 5 блока

3сопряжения, формирование кодовых последовательностей в виде заданных логических уровней О и 1 посредством генератора 2 произвольных тестовых последовательностей, формирование логических уровней кодовых последовательностей посредством драйвера 6 с предварительно скомпенсированными временными диаграммами, сравнение реально получаемой информации с ожидаемой и выдача результатов сравнения в ОЗУ 13 блока 1 управления посредством дискриминатора

4блока 3 сопряжения.

30

35

40

Формула изобретения

1. Устройство для автоматического контроля больших интегральных схем, содержащее блок управления, блок сопряжения, многоканальный блок формирования временных диаграмм причем первый вход блока управления соединен с первым выходом блока сопряжения, первая группа выходов - с первыми группами входов многоканального блока формирования временных диаграмм и блока сопряжения, о т л и тем, что, с целью повышения достоверности контроля за счет выравнивания временных диаграмм

0

5

0

0

5

0

5

0

5

каналов, в него введены программируемый счетчик импульсов, формирователь задержки, генератор произвольных тестовых последовательностей, компаратор, коммутатор, многоканаль- ньш компенсатор, первая группа входов которого соединена с выходами - многоканального блока формирования временных диаграмм, вторая группа входов - с первой группой выходов блока управления, а выходы - с второй группой входов блока сопряжения, вторая группа выходов которого соединена с первой группой входов коммутатора, вторая группа входов которого соединена с первой группой выходов блока управления, а выход - с первым входом компаратора, выход которого соединен с вторым входом блока управления, а второй вход - с выходом формирователя задержки, первые входы которого соединены с первой группой выходов блока управления и первыми входами программируемого счетчика импульсов, второй вход - с выходом программируемого счетчика импульсов, второй вход которого соединен с соответствующим выходом второй группы выходов блока управления, вторая группа входов многоканального блока формирования временных диаграмм соединена с второй группой выходов блока управления, третья группа входов - с первой группой выходов генератора произвольных тестовых последовательностей, второй вход которого соединен с третьим выходом блока управления, третья группа входов - с первой группой выходов блока управления , а группа выходов - с третьей группой входов блока сопряжения.

2. Устройство по П.1, отличающееся тем, что каждый из каналов компенсатора состоит из регистра, двух п -входовьпс компараторов, линии калиброванных задержек, имеющей п выходов, схемы совпадения и двух цифровых компараторов, причем первьй вход первого компаратора соединен с первым входом канала, второй вход первого цифрового компаратора и первый вход второго цифрового KONfflapaTopa соединены с первьм выходом регистра, входы которого соединены с вторым входом канала, выход второго щ фрового компаратора соединен с выходом канала, выход первого цифрового компаратора соединен с входом линии калиброванных з-ядер13

ключены к зеркально объединенным первым входам коммутаторов, вторые входы которых соединены с группой выходов регистра, а выходы соединены с первым и вторым входами схемы совпадения, соединенной своим выходом с вторым входом второго цифрового компаратора.

3. Устройство ПОП.1, отличающееся тем, что блок управления

содержит оперативное запоминающее устройство, блок согласования, блок сравнения, буферный регистр и многоканальный программируемый генератор импульсов, выходы которого соединены с первой группой выходов блока,- вто

508314

рая группа выходов которого соединена с входами многоканального программируемого генератора импульсов и с выходами блока согласования, входы 5 которого соединены с первой группой выходов оперативного запоминающего устройства, второй выход которого соединен с первым входом блока сравнения, второй вход которого соединен 10 с выходом буферного регистра, выход блока сравнения соединен с первым входом оперативного запоминающего устройства, второй вход которого соединен с первым входом блока, входы- 15 выходы - с входами-выходами блока.

вход буферного регистра соединен с вторьш входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Многоканальный программируемый генератор импульсов | 1981 |

|

SU953703A2 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1150755A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Многоканальный программируемый генератор импульсов | 1985 |

|

SU1348985A1 |

| Устройство для автоматического контроля больших интегральных схем | 1981 |

|

SU1027735A1 |

Изобретение относится к области автоматизированных систем контроля и предназначено для контроля больших и сверхбольших интегральных схем (БИС) и (СБИС) на функционирование при их массовом производстве. Цель изобретения - повьшение достоверности БИС и СБИС путем выравнивания временных диаграмм каналов за счет привязки по времени всех каналов устройства к параметрам импульса, принятого за эталонный. Поставленная цель достигается введением в известное устройство программируемого счетчика импульсов, формирователя задержки, генератора произвольных .тестовых последовательностей, компаратора, коммутатора и многоканального компенсатора. Работа устройства поясняется в описании изобретения чертежами структурного вьтолнения отдельных блоков устройства и временными диаграммами. 2 з.п. ф-лы. 10 ил.. (Л

/г./

От дискриминатора i

23

247

25

7Г

V

Фиг.З

.

Фиг. 5

33

Й

J

J5

Фиг.В

Начало (общее) Занесение смдны данных до все Злоки

Начало лраграммы„ Ком- пвнсаи,ия раздроса

Программа nafluSpoffHU, Компенсация разброса каиоло8

Конец программы,, Ком- пенсацил разброса

РаЬочая программа pemi/iM

„ Контроль

Коней, (o mtfif)

Фиг. 9

Иачаю

JoHecfHue жюдньц данных

( канал с понощыо каннутапюра ff гявКмгчае/пся к конпаратору П

Patpeuiaemcfi прохол вение сигнзгИ через компараторы Я,Л Уез инверсии. 6n it94a№mcft fif1,

Ж

Пия, С1иЛнивоются с преЗеглныг91

зночениями

п,8, 4 S

Задний ippOHtn сравнивается с

I этапном

- I Получается О СШЗП h

ф.

J Включаются /t, (п, /i п (п t)

/7j сравнивается с зно- чениен

ф nt t 1

Передний, cppown. сравнийае/пся с

J,зталонон

СЖЛГ nanijtaeincn

Ло

OnnHfotemca л - (п П

(Конец KOHneneaifMразУроса в Я-ои канале

LJ

Конец

KOf rifHcauiUu разброса осек ка- намв

Составитель В.Помякшева Редактор А.Лежнина Техред Л.Микеш Корректор,М,Демчик

Заказ 8524/48 Тираж 747.Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ШШ Патент, г.Ужгород, ул.Проектная, 4

ЗыМ на печать оооУи ени (о йи юде за границы диапазона кои- tKHcamofn )

fajpeiaae/rrcff npotamdenae сиъна- ло через компараторы 3S,J7 с инберсивй

- -- - сраУниваетсо с предельным значением

Htm

ф nt S

Передний qjpoHm. сравнивается с . эталона floxytneiucfi О

Включается ()

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Устройство для контроля полупроводниковой памяти | 1977 |

|

SU691929A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-01-15—Публикация

1984-04-05—Подача