(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВРЕМЕННОГО ПОЛОЖЕНИЯ ОСНОВНОГО МАКСИМУМА ПЕРИОДИЧЕСКОГО

1

Изобретение относится к радиотехнике и может быть использовано ь системах передачи дискретной информации.

Известно устройство для определения временного положения основного максимума периодического сигнала которое анализирует электрический сигнал в некотором числе интервалов времени и определяет временное положение основного максимума периодического сигнала путем .. сравнения задержанного входного сигнала с уровнем отсечки на компораторе ij .

Такое устройство сложно и не обеспечивает высокой помехоустойчивости при определении временного положения ро- jj новного максимума периодического сигнала.

Наиболее близким к изобретению по технической сушности является устройство для определения временного положа- ju ния основного максимума периоцичес кого сигнала; содержащее аналогоцифровой преобразователь, первый вход которого соединен с входом устройства, СИГНАЛА

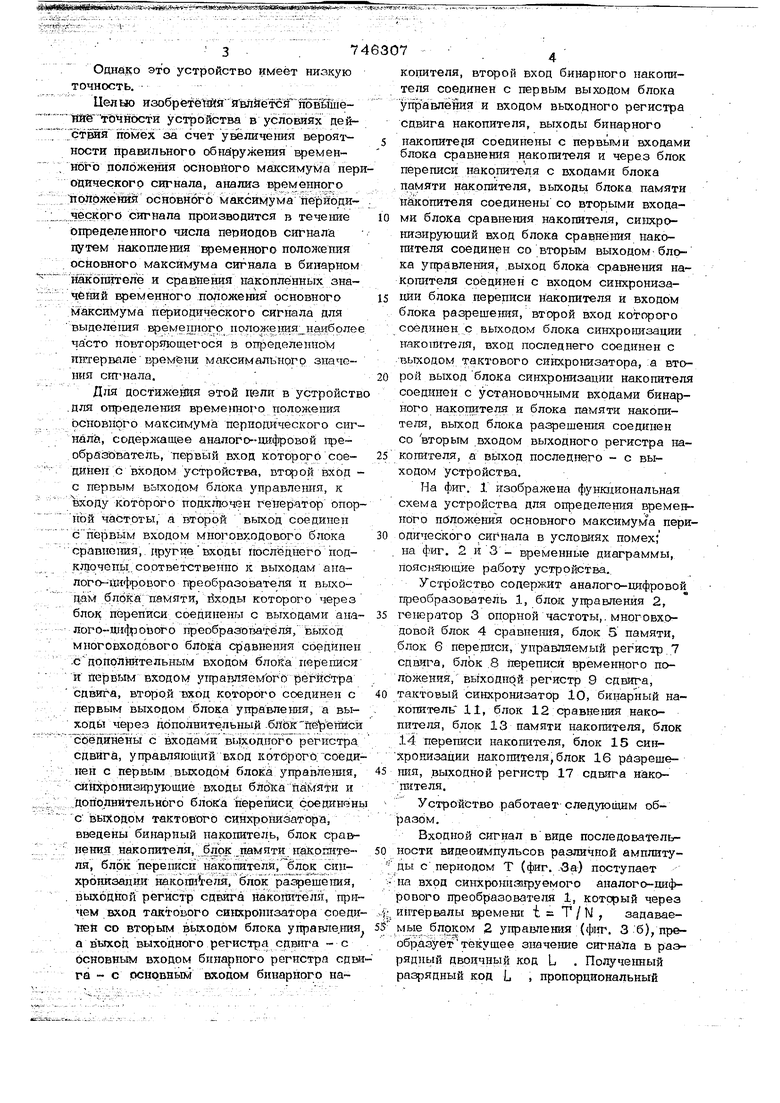

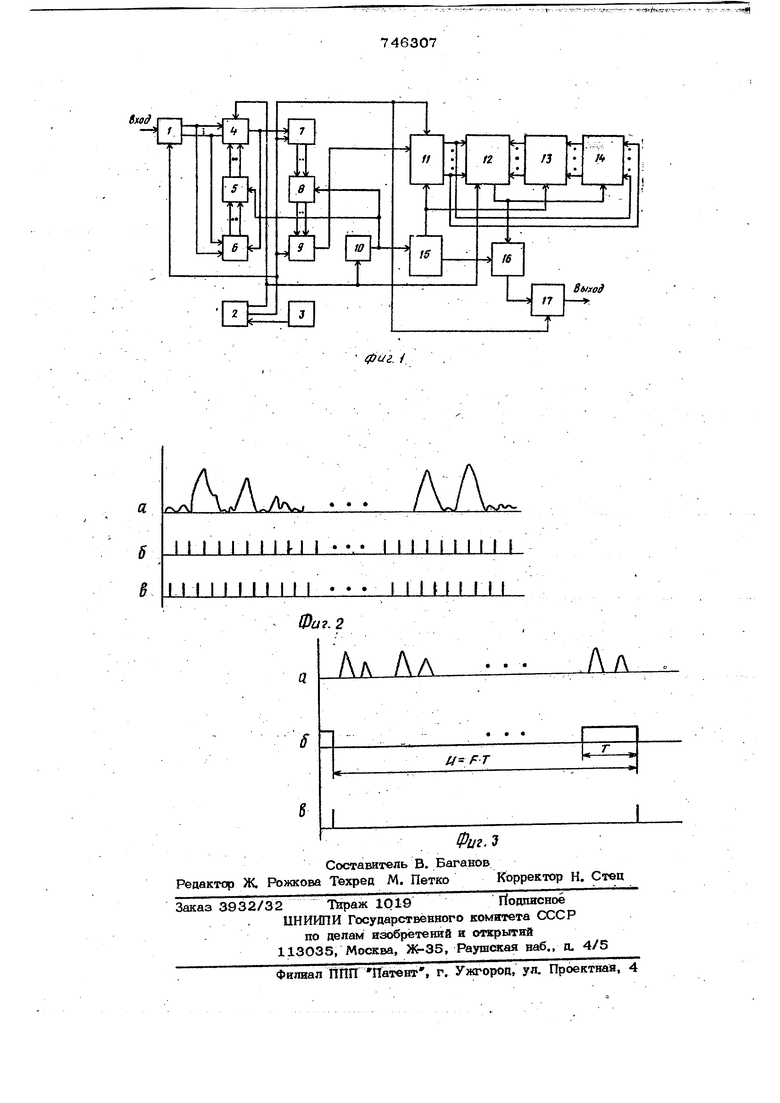

второй вход - с первым выходом блока управления, ко входу которого подключен генератор опорной частоты, а второй выход соединен с первым входом многовходового блока сравнения, другие входы которого подключены соответственно к выходам аналогр-1Щ(|ровог6 преобразователя и выходам блока памяти, входы которого через блок переписи соединены с выходами аналого-цифрового преобразователя, выход многовходового блока сравнения coetWHeH с дополнительным входом блока переписи и первым входом уп)авпяёмбро регистра сдвига, второй вход которого соединен с первым выходом блока управпения, а выходы - через дополнительный блок переписи соединены с входа «1И выходного регистра сдвига,управаяюошй. вход которого соединен с первым выходом блока управления, синхронизирующие входы блока памяти и дополннтепьного блока переписи соединены с выходом тактового синхронезатора 2. : 3 ..74 Однако это устройство имеет низкую точность. Целые изобрётёМяямйется поВьТше ййё точности устройства в условиях дей.стетя ггомёх за счет увеличе1шя верояа-ности правильного обнаружения временного положения основйого мшссимуК а пери одического сигнала, анализ временного ;попржё1яйя основного максимума йфйодическрго сигнала производится в течегше определенного числа периодов сигнала накопления нременного положения основного максимума сигнала в бинарном накогпггепё и срав1иеюга накоплённьк значений временного положения основного максимума периодического сигнала для выделе1шя временного положешя; наибрпее часто повторяющегося Б ощзеделенном иетервалеврем&ни мшссимальногр значения стчшла. Цля достижеййя этой цели в устройств .для определешет временного положения основного максимума перногшческого сигнала, содержащее аналого-цифровой ipe образователь, первый вход которого соединен с входом устройства, второй вход с первым выходом блока управления, к входу которого подключен генератор опорной частоты, а второй выход соединен с первым входом многовходового блока сравнения,, другиевходы последнего под. кгаочены.. со.ответствеино к выходам аналого-цифрового преобразователя и выхоцаМ .блока памяти, йх.оды которого через блок переписи, соединены с выходами ана лого-ци 1росогопреобразотзагеля, выход многовходового блока сравненля соединен .с допрЛ ните ль ным вхо до м блока не ре писи и первым входом упрапляёмогб рёгйстра сдвига, второй вход которого соединен с первым выходом блока управления, а вы ходьт через цбполнитепьный .блЬК пфепйсй coeSHHelibi с йходами вь1ходного регистра. сдвига, управляющей вход котброго. соединен с первым выходом блока управлешш, сйгкронизирующие входы блб1са паШти и дойолнйтельного блока переписи, соединены С йыходом тактового синхронизатора, введены бинарный накопитель, блок срав нения накопителя, блок памяти накопителя, блок переписи накопителя, блок сиихронизаии.и накопителя, блок разрешения, выходной регистр сдвига накопителя, Щ1И чем вход тактового синхронизатора соеди -нен со вторым выходом блока управле.Ш1Я Q выхои выходного регистра сдвига с основным входом бинарного регистра сдви га с рсновньш входом бинарного 7 копителя, второй вход бинарного накопителя соединен с первым выходом блока управления и входом выходного регистра сдвига накопителя, выходы бинарного накопите{Ш соединены с первьтми входами блока сравнешш накопителя и через блок переписи накопителя с входами блока памяти накопителя, выходы блока памяти нйсопителя соединены со вторыми входами блока сравнения накопителя, синхронизирующий вход блока сравнения накопителя соединен со вторым выходомблока управления, выход блока сравнения накрпителя соединен с входом сиггхрониза1ШИ блока переписи накопителя и входом блока разрешешм, второй вход которого соединен,.с выходом блока синхронизации . какопите/ет, вход последнего соединен с выходом тактового синхро1шзатора, а второй выход блока синхронизации накопителя соединен с установочными входами бинарного накопителя и блока памяти накопителя, выход блока разрешения соединен со вторым входом выходного регистра накопителя, а выход последне ГО - с выходом устройства. На фиг. 1 ргзображена фуша иональная схема устройства для определения временного пс5дожения основного максимума периодического в условиях помех; на фщ--, 2 и 3 - временные диаграммы, поясняющие работу устройства.. Устройство содержит аналого-шгфровой преобразователь 1, блок управления 2, генератор 3 опорной частоты,. многовх.одовой блок 4 сравнения, блок 5 памяти, блок б пере.писи, управляемый регистр..7 сдвига, блок .8 йзереписи временного положения,вБ1Ходной регистр 9 сдвига, тактовый синхронизатор 10, бинарный накопитель 11, блок 12 сравнения накопителя, блок 13 памяти накопителя, блок 14 переписи накопителя, блок 15 синхропизации накопнтеля блок 16 разрешешгя, выходной регистр 17 сдвига накопителя. Устройство работает след5гющим образбм. Входной сигнал ввиде последователькости видеоимпульсов различной амплиту,Ды с периодом Т (фиг. .За) поступает на вхрд синхронизируемого аналого-цифрового преобразователя 1, который через интервалы времешг t T/N , задаваемь е блоком 2 угфавления (фиг. 3 б), преобразуёттекушее значегоге сигнала в раэряциый двоичный код L . Получе)Ешый разрядный код L , пропорциональный значеюоо входного сигнала в текущи,й момент времени, поступает одновременно на блок 4 и блок 6, На другие входы блока сравнения поступает также р азрядный двоичный код М с блока 5 памяти, хранящий максимал1Ьное значение сигнала с начала интервала анализа. Бло сравнения по кажаому импульсу синхрони зации:, поступающему с блока управления с некоторой задержкой относительно моментов преобразования входного сигнала в код (фиг, Зв), вырабатывает импульс в том случае, если код, поступающий от аналого-цифрового преобразовател превышает код, поступающий от блока памяти. Этим импульсом блока сравнения производится перепись кода с аналого-цифрового преобразователя через блок переписи в блок памяти, а также запись 1 в первый разряд управляемого регистра 7 сдвига, имеющего N разрядов, и запись О во все остальньш раэряды управляемого регистра 7 сдвига. На сдвигающий вход управляемого регистра сйвига поступают с блока управгления сдвигающие импульсы, имеющие тот же период t , что и импульсы синхронизации преоб эазователя 1. Таким образом, положение 1 в управляемом регистре сдвига характеризует временное положение основного максимума сигнала относительно начала интервала анализа. Информация из управляемого регист ра сдвига в параллельном разрядном коде N через блок 8 переписи временного положения переписывается в выходной регистр 9 сдвига, имеющий также N раэрядов, по сигналу, поступающему на блок 8 с выхода тактового синхронизатора 10 На выходе такто.вого синхронизатора 10 один раз за период Т сигнила появляется импульс, совпадающий по временному положению с импульсами, синхроттазирующими аналого-цифровой преобразователь. для чего выход схемы управления 2 соединен с входом тактового.синхронизатора Благодаря сбросу в О (М -1) старших разрядов управляемого регистра сдвига, в нем, а следовательно и в выходном регистре 9 сдвига, в любой момент времени находится только одна 1, характеризутощая временное положение основного максимума сигнала относите льпо начала интервала анализа. В конце интервала анализа импульсом, поступающим с тактового синхронизатора 10 производится обнуление сблока 5 памята, что подготавливает устройство к определению вре-

6 мешюго положения основного максимума cifTHarta на следующем периоде сигнала. Импульсы с выхода регистра 9 поступают на бинарный накош тель 11 сигнала, который построен известным образом на регистрах сдвига. Число регистров сдвига в бинарном накопителе М, число разрядов в каждом регистре сдвига W. Импульсы сдыгга для регистров бинарного накопителя поступают в той же фазе что и импульсы сдвига для регистров 7 и 9. На М выходах бинарного накопителя 11 образуется М-разрядное двоичное число, которое меняется с интервалом времени t и равно чис11у появившихся епиниц.на выходе регистра 9 сдвига в соответствующем интервале BpeMeHir-t . Интервал времени накопления бинарного накопителя г: РТ, где Г - число анализируемых периодов сигнала. Максимально возможное значение F может быть задано как F . При воздействии помех наиболее вероятно накопление наибольшего числа в том столбце матрицы, образованной М регистрами сдвига бинарного накопителя, который совпадает во временном положении с основным максимумом периодического сигнала. С М выходов бинарного накопителя 11 поступает М-разрядное двоичное число в параллельном коде на блок 12 сравнения накопителя. На другие входы блока сравнения накопителя поступает двоичное М-разрядное числб с блока памяти накопителя 13. Эти числа сравниваются в блоке 12 по сигналу, поступающему на его .вход с блока 2 управления. Если число, поступающее с бинарногонакопителя 11, больше числа поступающего с блока памяти накопителя, то в блок памяти 13 по сигналу, поступающему с выхода блока сравнения накопителя, переписывается соответствующее число из столбца матрицы, образованной регистрами 11 сдвига бинарного накопителя через блок 14 переписи накопителя. В конце интервала времени накопления с выхода блока 15 синхронизации бинарного накопителя поступает сигнал длительностью Т на блок разрещегая 16 (фиг. 4а, б). По этому сигналу импульы превышения с блока 12 поступают через блок 16 на установочные входы выходного регистра 17 сдвига накопнеля,содержащего W. разрядов. Каждый з этих импульсов устанавливает в О ( W -1) старший разряд регистра 17 сдвига и в его младший разряд. Им- пульсы сдвига поступают на вход выходного регистра 17 сдвига в той же фазе, что и на сдвигающие регистры 7 и 9 и бинарный накопитель 11. Таким образом, по окончании интервала времени накопителя И Р Т в одном из разрядов выходного регистра 17 сдвига бинарного накопителя будет записана 1 совпадающая по времени с основным максимумом периодичеркого сигнала, выделенного путем накопления его во времени за F периодов сигнала. По окончании интервала накопления И с 5 блока синхронизации бинарного йакопнтеля поступает на вход установки в О бинарного накопителя 11 и блока памяти накопителя сигнал, устанавливающий в О бинарный накопитель и блок памяти накопителя, подготавливая их тем самым к новому интервалу работы (фиг, 4в), Тем самым достигается по выше нная: помехоустойчивость устройства определения еременного по;1ожения основного МаксиК 1ума периодического сигнала в условиях действия помех. Выход регистра сдвига 17 и является выходом устройств Формула изобретения Устройство для определения BpeMejfного положения основного максимума пер одического сигнала, содержащее анаяогоцифрО1Вой преобразователь, первый вход которого соединен с входом устройства, второй вход - с первым выходом блока управления, к входу которого подключен генератор опорной частоты, а второй выход соединен с первым входом многсьвходового блока сравнения, другие входы последнего подключены соответственно к выходам аналого-цифрового преобразователя и вьпсодам блока памяти, входы которого через блок переписи соединены с выходами аналого-цифрового преобразователя, выход многовходового блока сравнегшя соединен с дополнительным вхо . дом блока переписи и первым входом управляемого .регистра сдвига, второй вход которого соединен с первым выходом блока управления, а выходы через 10 полннтельный блок переписи соединены с входами выходного регистра сдвига, уп- i равляюший вход которого соединен с первым выходом блока управления, синхронизкруюшие входы блока памяти и дополнительного блока переписи соединены с выходом тактового синхронизатора, о т л ичаюшееся тем, что, с целью повышения точности устройства в условиях действия помех, в него введены бинарный накопитель, блок сравнения накопителя, блок памяти накопителя, блок переписи накопителя, блок синхронизации накопителя, блок разрешения, выходной регистр сдвига аакопителя, причем вход тактового синхронизатора соединен со вторым выходом блока управления, а выход выходного регистра сдвига - с основным входом бинарного накопителя, второй вход последнего соединен с первым выходом блока управления и входом выходного регистра сдвига накопителя, выходы бинарного накопитеяя соединены с первыми входами блока сравнения накопителя и через блок переписи накопителя с входами блока памяти накопителя, выходы блока памяти, накопителя соединены со вторыми входами блока сравнения накопителя, си19сровизирующий вход блока сравтення накопятеля соединен со вторым выходом блока управления, выход блока сравнейня накопитетю соединен с входом синхронизации блока переписи накопителя и входом бло-ка разрешения, втсрой вход которого соедивен с выходом блока синхронизации накопителя, вход последнего соединен с . выходом тактового синхронизатора, а второй вь$ход блока синхронизации накопителя соединен с установочными входами бинарного накопителя и блока памяти какопителя, вЬ1ход блока разрешения соедийен со втбрым входом выходного регистра сдвига накопителя, а выход последнего с выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3891930 кл. 328-131, 11.09.75. 2.Авторское свидетельство СССР № 577661, кл. Н 03 К 5/18, 1975.

фиг. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения временного положения основного максимума периодического сигнала | 1976 |

|

SU577661A1 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

| Устройство автоматической коррекции координатных искажений телевизионного изображения | 1981 |

|

SU1012456A1 |

| Аналого-цифровой фазовращатель | 1988 |

|

SU1584082A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ВЗАИМНОЙ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ В РАЗНЕСЕННОЙ РАДИОЛОКАЦИОННОЙ СИСТЕМЕ | 1999 |

|

RU2163383C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| СИСТЕМА ДЛЯ СЖАТИЯ ДВУХМЕРНОГО МАССИВА ИНФОРМАЦИИ | 1993 |

|

RU2046398C1 |

| Цифровой регистратор импульсных процессов | 1987 |

|

SU1441333A1 |

JVA

а

1 11 I I I и и I у I И I I 1 I It t

I i I I I I I I I I I у М I и { t I t

Фи.2

AA

Авторы

Даты

1980-07-05—Публикация

1978-02-03—Подача