(Л

00 00

процессов с максимальными амплитудами, а также за счет одновременности регистрации и вывода введенной информации. Цель достигается тем, что в регистратор дополнительно введены три узла управления, три узла памяти, три формирователя импульса, четыре регистра 38, 39, 40 и 41, две схемы 44 и 45 сравнения, два блока 20 и 21 элементов И, коьшаратор 11 кодов.

счетчик 14 интервала анализа, выходной регистр, блок элементов ИЛИ, восемь элементов И, два элемента ИЛИ-НЕ, что позволяет одновременно производить регистрацию двух импульсных процессов С максимальными амплитудами из -серии поступающж на вход и выводить информацию о двух других процессах, зарегистрированных ранее. 2 з.п. ф-лы, 10 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU991511A2 |

| Запоминающее устройство | 1981 |

|

SU1018150A1 |

| Устройство для контроля параметров | 1989 |

|

SU1783477A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Умножитель частоты | 1988 |

|

SU1562908A1 |

| Устройство для регистрации информации | 1982 |

|

SU1037300A1 |

| Устройство для учета стоимости в междугородном монетном телефонном аппарате | 1981 |

|

SU1029424A1 |

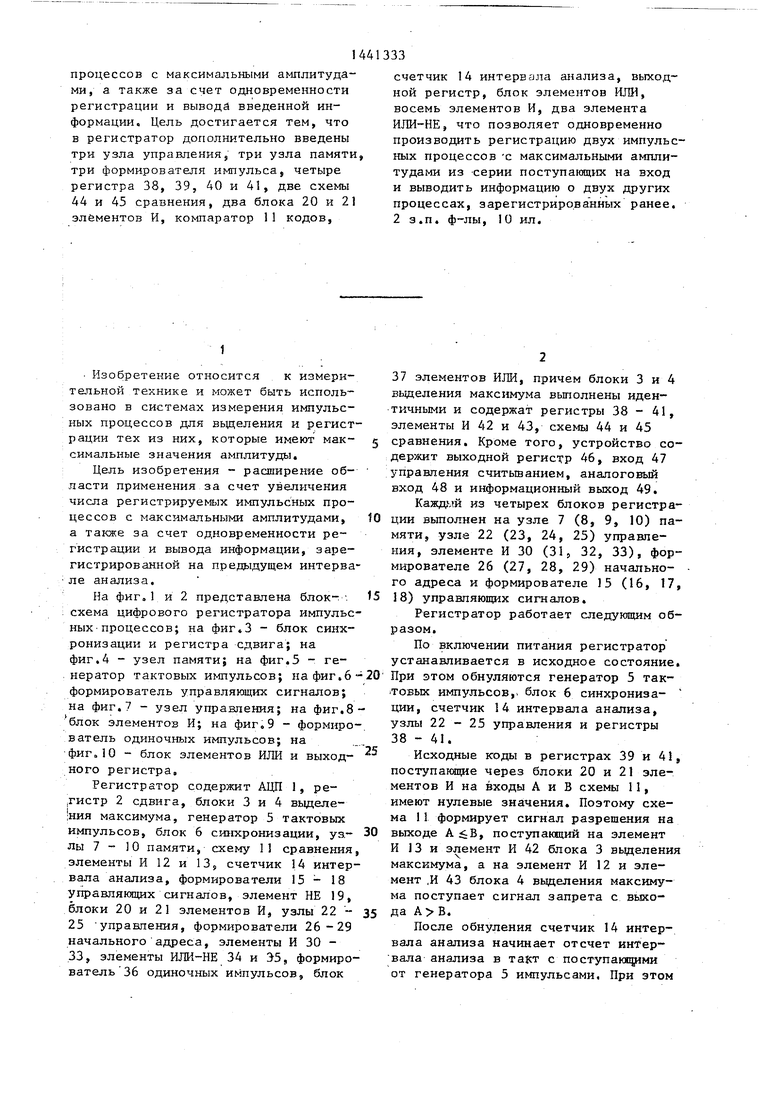

Изобретение относится к измерительной технике и может быть использовано в системах измерения импульсных процессов для вьщеления и регистрации тех из них, которые имеют максимальные значения амплитуды. Целью изобретения является растирение области применения за счет увеличения числа регистрируемых импульсных

1

Изобретение относится к измериельной технике и может быть использовано в системах измерения импульсых процессов для вьщеления и регистации тех из них, которые имеют мак- g симальные значения амплитуды.

Цель изобретения - расширение об- асти применения за счет увеличения числа регистрируемых импульсных процессов с максимальными амплитудами, tO а также за счет одновременности регистрации и вывода информации, зарегистрированной на предыдущем интерва- ле анализа.

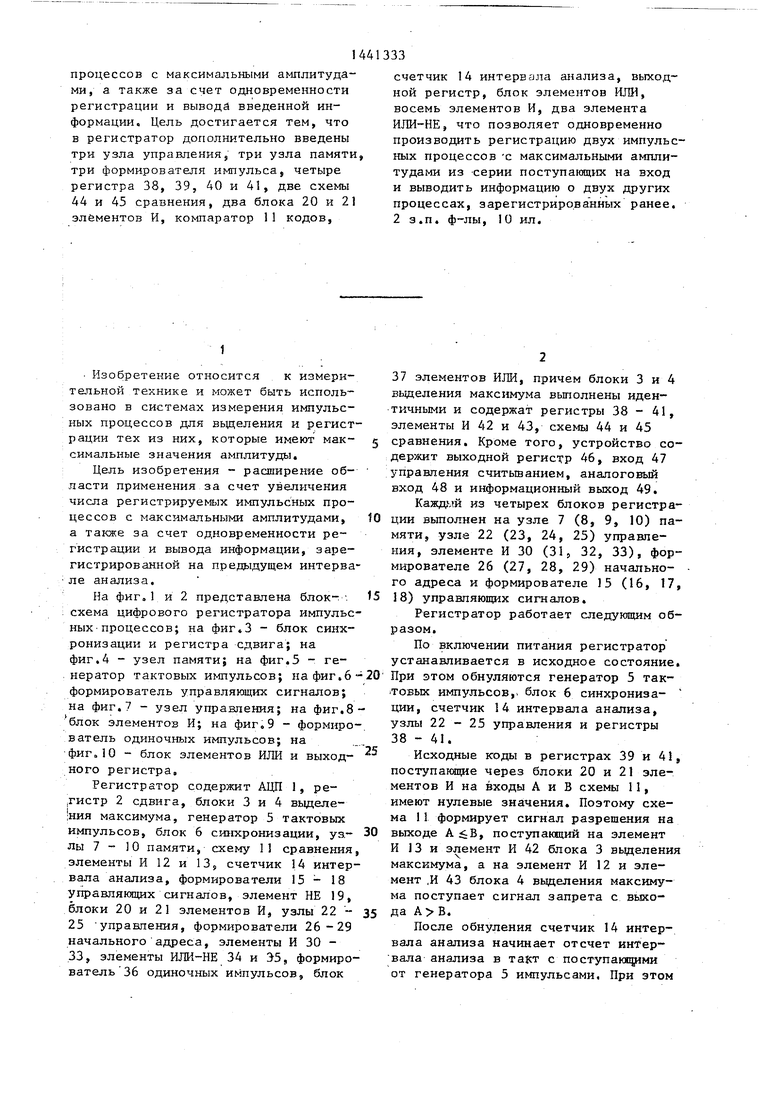

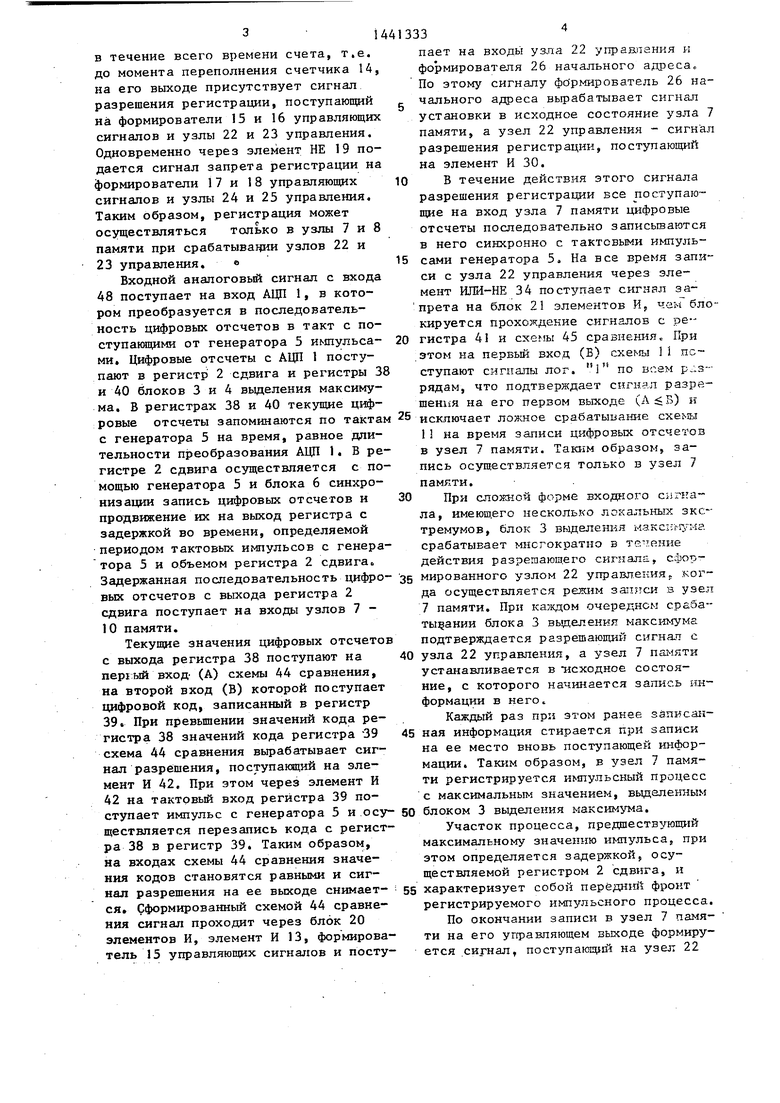

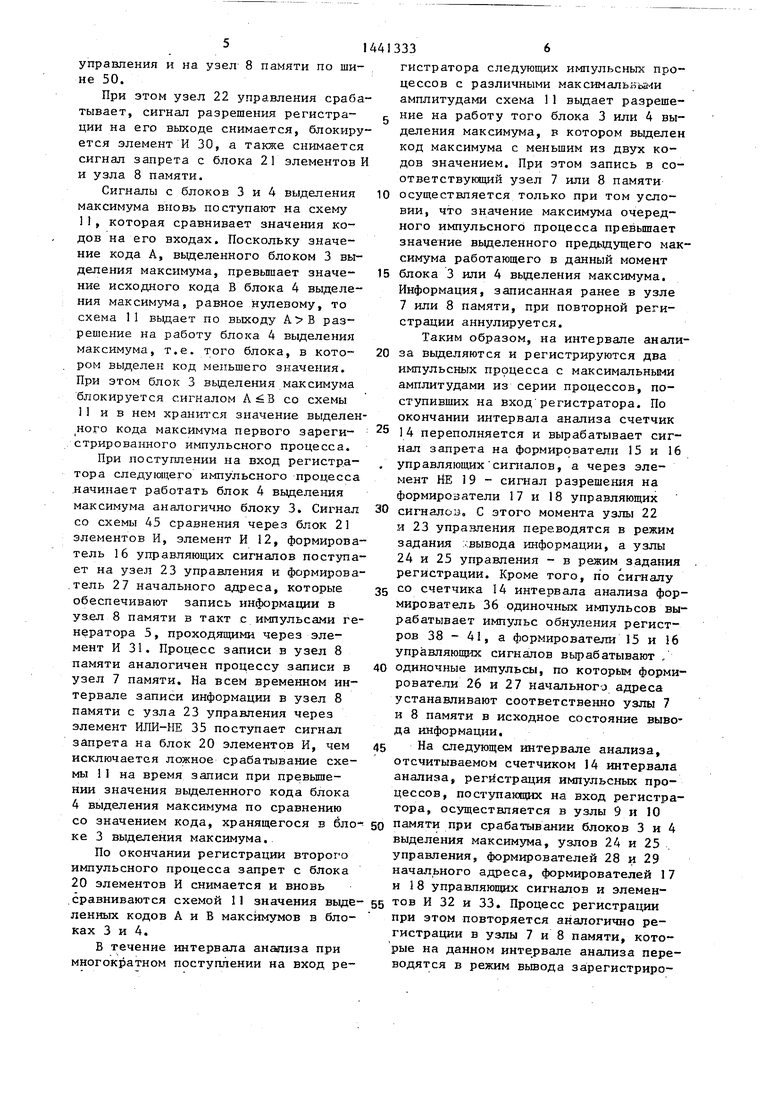

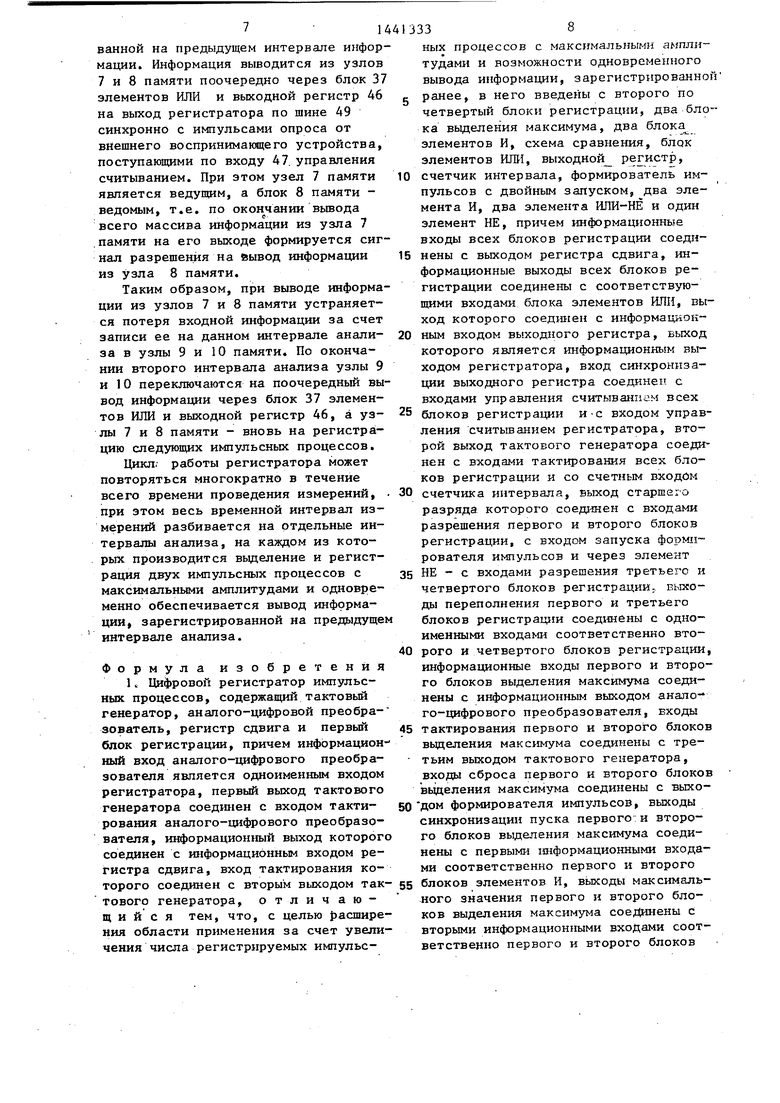

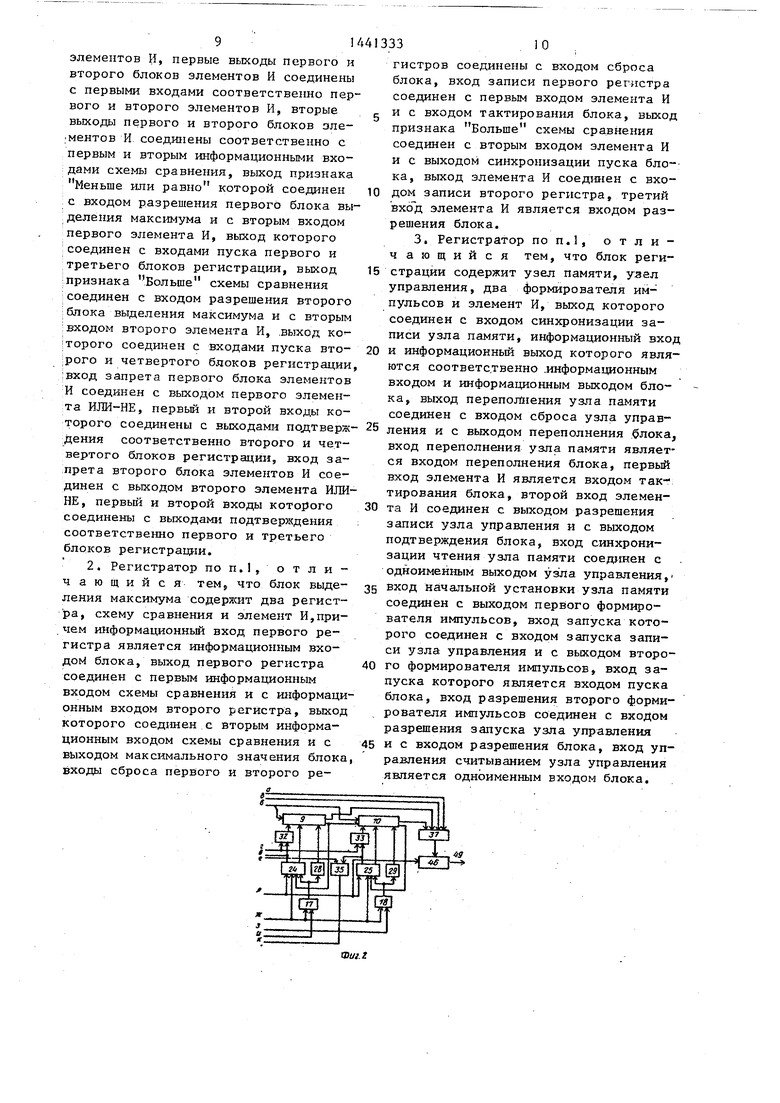

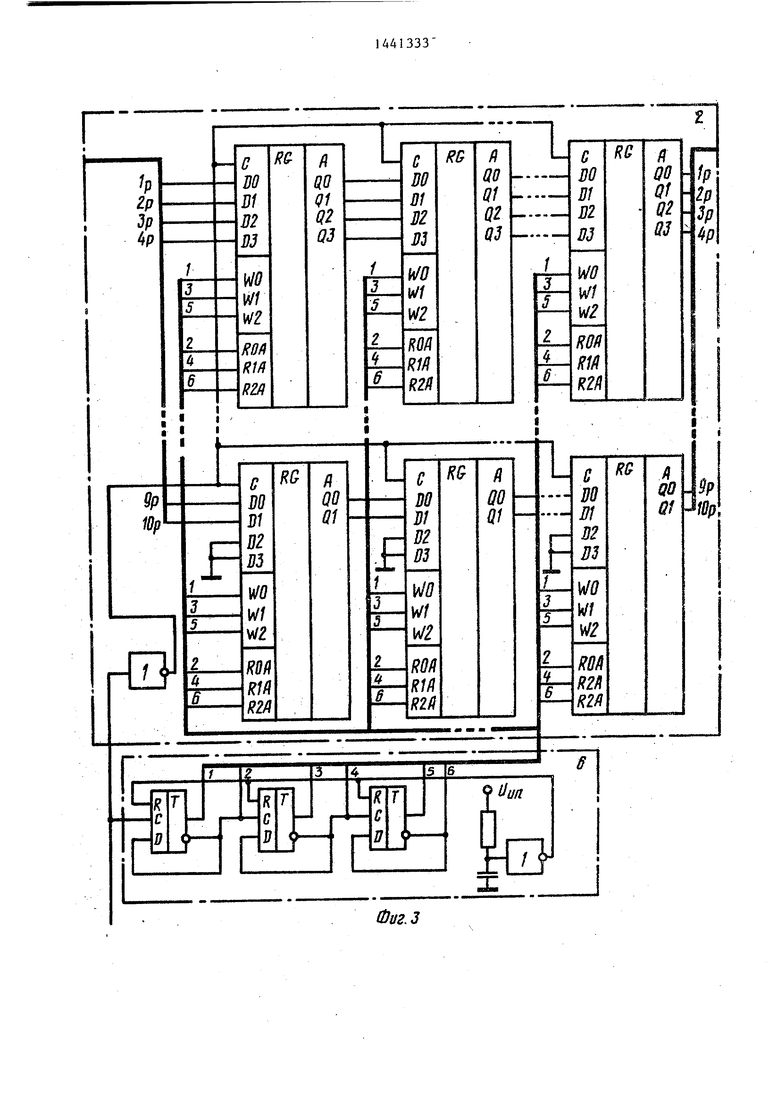

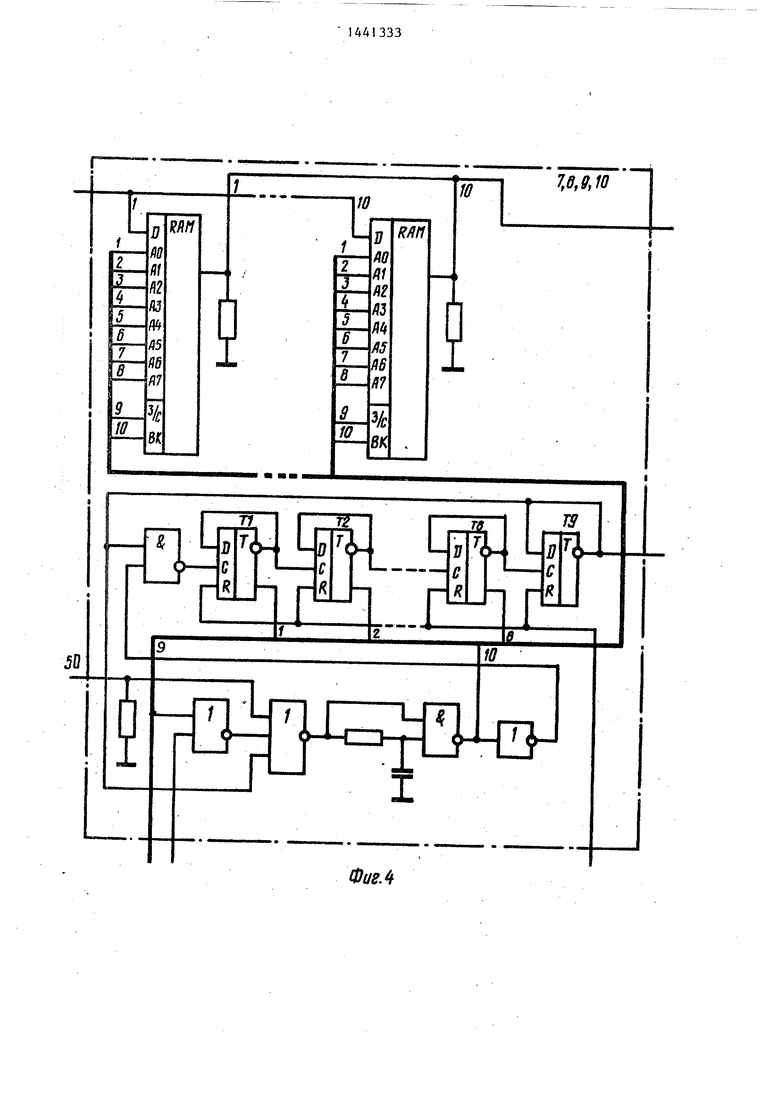

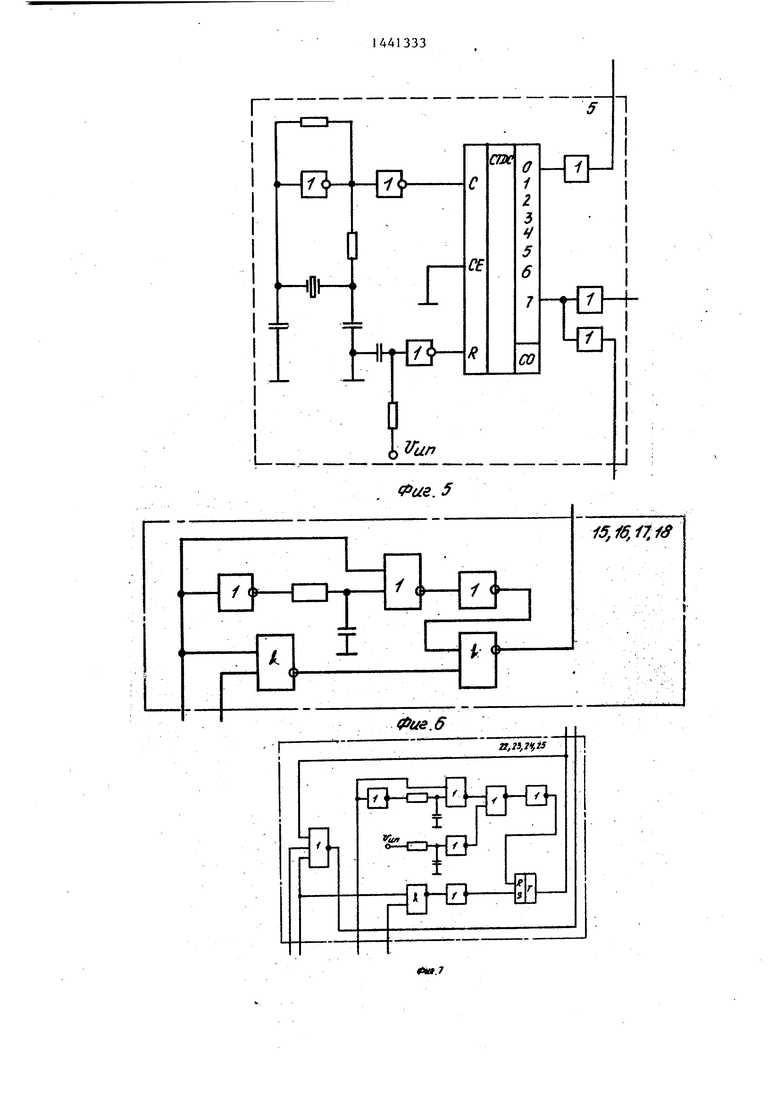

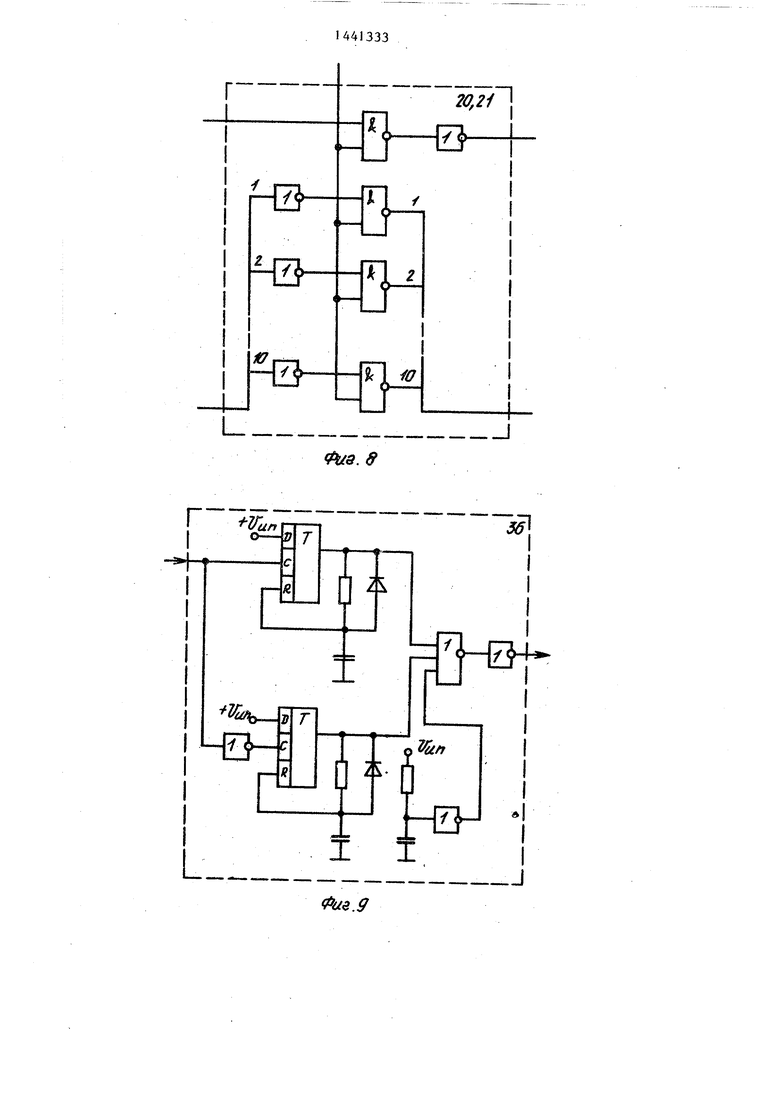

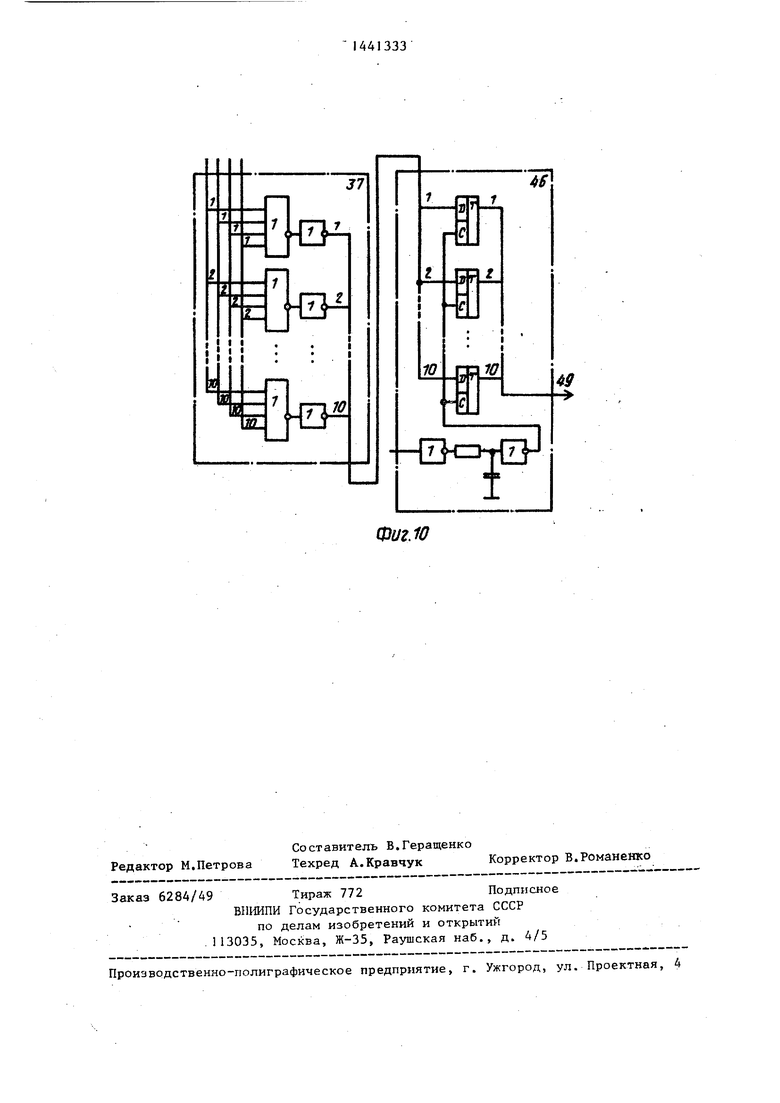

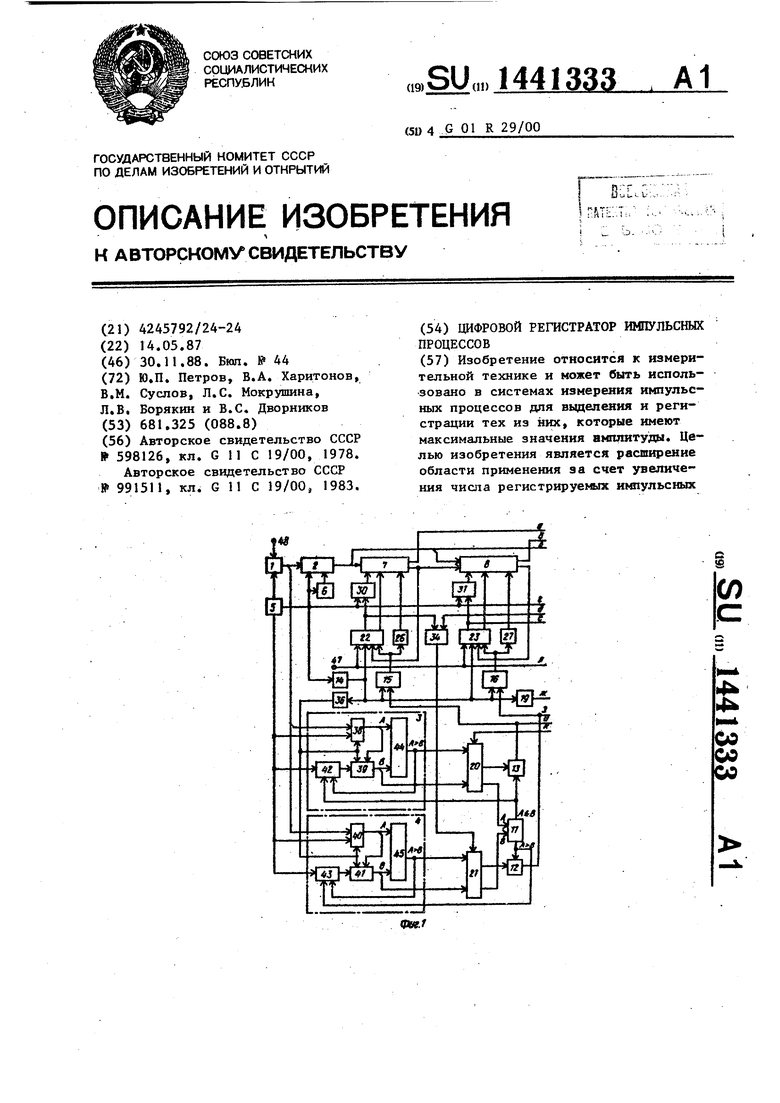

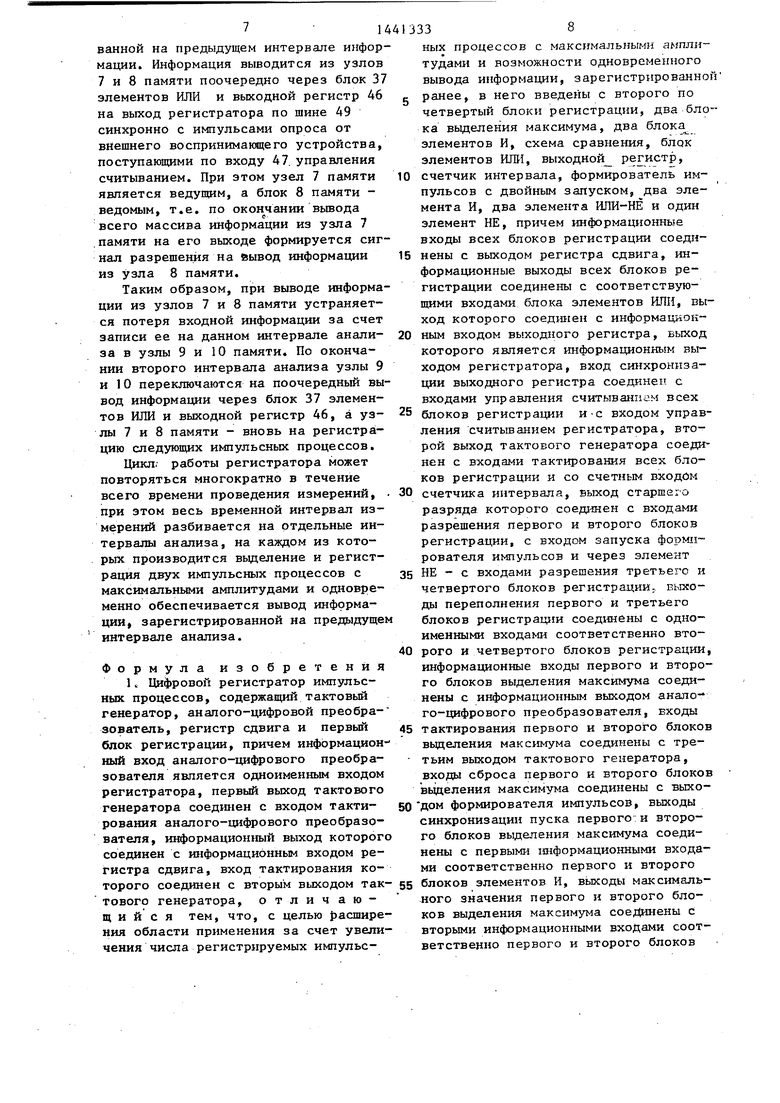

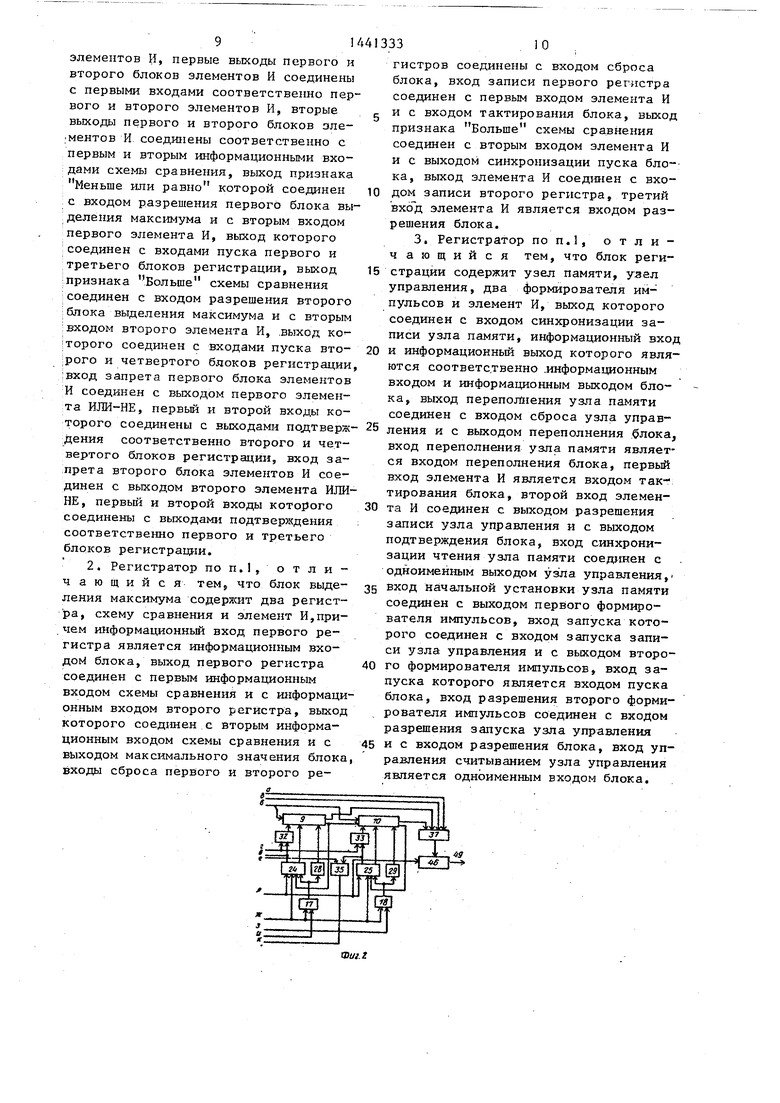

На фиг, 1 и 2 представлена блок- . 5 схема цифрового регистратора импульсных- процессов; на фиг.З - блок синхронизации и регистра сдвига; на фиг.4 - узел памяти; на фиг.З - генератор тактовых импульсов; на фиг.6-20 формирователь управляющих сигналов; на фиг. 7 - узел управления; на фиг.8- блок элементов И; на фиг,9 - формирователь одиночных импульсов; на фиг.10 - блок элементов ИЛИ и выход- него регистра.

Регистратор содержит АЦП I, ре- гистр 2 сдвига, блоки 3 и 4 выделе- ;ния максимума, генератор 5 тактовых импульсов, блок 6 синхронизации, уз- 30 лы 7 - 10 памяти, схему 11 сравнения, элементы И 12 и 13, счетчик 14 интервала анализа, формирователи 15 - 18 управляющих сигналов, элемент НЕ 19, блоки 20 и 21 элементов И, узлы 22 - 35 25 управления, формирователи 26-29 начального адреса, элементы И 30 - 33, элементы ИЛИ-НЕ 34 и Э5, формирователь 36 одиночных импульсов, блок

37 элементов ИЛИ, причем блоки 3 и 4 вьщеления максимума вьшолнены идентичными и содержат регистры 38 - 41, элементы И 42 и 43, схемы 44 и 45 сравнения. Кроме того, устройство содержит выходной регистр 46, вход 47 управления считьтанием, аналоговый вход 48 и информационный выход 49.

Кажд.чгй из четырех блоков регистрации вьтолнен на узле 7 (8, 9, 10) памяти, узла 22 (23, 24, 25) управления, элементе И 30 (31, 32, 33), формирователе 26 (27, 28, 29) начального адреса и формирователе 15 (16, 17, 18) управляющих сигналов.

Регистратор работает следующим образом.

По включении питания регистратор устанавливается в исходное состояние. При этом обнуляются генератор 5 так- товых импульсов,, блок 6 синхрониза- ции, счетчик 14 интервала анализа, узлы 22 - 25 управления и регистры 38-41.

Исходные коды в регистрах 39 и 41, поступакнцие через блоки 20 и 21 элементов И на входы А и В схемы 11, имеют нулевые значения. Поэтому схема 11 формирует сигнал разрешения на выходе А :В, поступакщий на элемент И 13 и элемент И 42 блока 3 вьщеления максимума, а на элемент И 12 и элемент ,И 43 блока 4 выделения максимума поступает сигнал запрета с выхода А В.

После обнуления счетчик 14 интервала анализа начинает отсчет интервала анализа в такт с поступакш5нмя от генератора 5 импульсами. При этом

в течение всего времени счета, т.е. до момента переполнения счетчика 14, на его выходе присутствует сигнал разрешения регистрации, поступающий на формирователи 15 и 16 управляющих сигналов и узлы 22 и 23 управления. Одновременно через элемент НЕ 19 подается сигнал запрета регистрации на формирователи 17 и 18 управляющих сигналов и узлы 24 и 25 управления. Таким образом, регистрация может осуществляться только в узлы 7 и 8 памяти при срабатывании узлов 22 и 23 управления. в

Входной аналоговый сигнал с входа 48 поступает на вход АЦП 1, в котором преобразуется в последовательность цифровых отсчетов в такт с поступающими от генератора 5 и шyльca- ми. Цифровые отсчеты с АЩ1 1 поступают в регистр 2 сдвига и регистры 38 и 40 блоков 3 и 4 вьщеления максиму20 гистра 41 и схемы 45 cpaBneHiiH, При этом на первый вход (Б) схемы И поступают сигналы лог. 1 по впам р.:.з- рядам, что подтверждает сигн.л разрешения на его первом выходе () н

ма. В регистрах 38 и 40 текущие цифровые отсчеты запоминаются по тактам 25 исключает ложное срабатывание схемы с генератора 5 на время, равное дли- 1 1 на время записи цифровых отсчетов

в узел 7 памяти. Таким образом, запись осуществляется только в узел 7 памяти.

30 При слозЕНой форме входаого сигнала, имеющего несколько локальных экстремумов, блок 3 выделения макс:г;г1умг срабатывает многократно в течение действия разрешающего сигнала, сфор- Задержанная последовательность цифро- 35 мированного узлом 22 угфавления,, ког- вьк отсчетов с выхода регистра 2 да осуществляется записи в узел сдвига поступает на входы узлов 7 - 7 памяти. При очередном сраба- 10 памяти.тыкании блока 3 вьщеления максимума

Текущие значения цифровых отсчетов подтверждается разрешающий сигнал с с выхода регистра 38 поступают на 40 узла 22 управления, а узел 7 памяти

устанавливается в -исходное состоятельности преобразования АЦП 1. В регистре 2 сдвига осуществляется с помощью генератора 5 и блока 6 синхронизации запись цифровых отсчетов и продвижение их на выход регистра с задержкой во времени, определяемой периодом тактовых импульсов с генератора 5 и объемом регистра 2 сдвига.

пер1;ый ВХОД (А) схемы 44 сравнения, на второй вход (В) которой поступает цифровой код, записанный в регистр 39. При превышении значений кода регистра 38 значений кода регистра 39 схема 44 сравнения вырабатывает сигнал разрешения, поступающий на элемент И 42. При этом через элемент И 42 на тактовый вход регистра 39 поние, с которого начинается запись информации в него

Каждый раз при этом ранее записан- 45 ная информация стирается при записи на ее место вновь поступающей информации. TaKiiM образом, в узел 7 памяти регистрируется и myльcный проздесс с максимальным значением, вьщеле гаым ступает импульс с генератора 5 и .осу- 50 блоком 3 вьщеления максимума. ществляется перезапись кода с регист-Участок процесса, предшествующий

ра 38 в регистр 39. Таким образом, на входах схемы 44 сравнения значения кодов становятся равными и сигнал разрешения на ее выходе снимается рформированный схемой 44 сравнения сигнал проходит через блок 20 элементов И, элемент И 13, формирова-

максимальному значению импульса, при этом определяется задержкой $ осуществляемой регистром 2 сдвига, и 55 характеризует собой переднш фронт регистрируемого импульсного процесса. По окончании записи в узел 7 памяти на его угфавпяющем выходе формирутель 15 управляющих сигналов и посту- ется .сигнал, поступающие на узел 22

441333

пает на входы узла 22 упраапания и формирователя 26 начального адреса По этому сигналу фо рмирователь 26 нае чального адреса вырабатывает сигнал установки в исходное состояние узла 7 памяти, а узел 22 управления - сигнал разрешения регистрации, поступающий на элемент И 30.

10 В течение действия этого сигнала разрешения регистрации все поступающие на вход узла 7 памяти цифровые отсчеты последовательно записьшаются в него синхронно с тактовыми импуль15 сами генератора 5, На все время записи с узла 22 управления через элемент ИЛИ-НЕ 34 поступает сигнал за- прета на блок 21 элементов И; че;---; блокируется прохождение сигналов с ре20 гистра 41 и схемы 45 cpaBneHiiH, При этом на первый вход (Б) схемы И поступают сигналы лог. 1 по впам р.:.з- рядам, что подтверждает сигн.л разрешения на его первом выходе () н

25 исключает ложное срабатывание схемы 1 1 на время записи цифровых отсчетов

ние, с которого начинается запись инмаксимальному значению импульса, при этом определяется задержкой $ осуществляемой регистром 2 сдвига, и 55 характеризует собой переднш фронт регистрируемого импульсного процесса. По окончании записи в узел 7 памяти на его угфавпяющем выходе формирууправления и на узел 8 памяти по шине 50.

При этом узел 22 управления срабатывает, сигнал разрешения регистрации на его выходе снимается, блокируется элемент И 30, а также снимается сигнал запрета с блока 21 элементов И и узла 8 памяти.

Сигналы с блоков 3 и 4 выделения максимума вновь поступают на схему 11, которая сравнивает значения кодов на его входах. Поскольку значение кода А, выделенного блоком 3 выделения максимума, превьшает значение исходного кода В блока 4 выделения максимума, равное н улевому, то схема 11 выдает по выходу разрешение на работу блока 4 выделения максимума, т.е. того блока, в котором выделен код меньшего значения. При этом блок 3 выделения максимума блокируется сигналом со схемы 11 и в нем хранится значение выделен- ного кода максимума первого зареги- стрированного импульсного процесса.

При поступлении на вход регистратора следующего импульсного процесса .начинает работать блок 4 выделения максимума аналогично блоку 3. Сигнал со схемы 45 сравнения через блок 2 элементов И, элемент И 12, формирователь 16 управляющих сигналов поступает на узел 23 управления и формирова- ,тель 27 начального адреса, которые обеспечивают запись информации в узел 8 памяти в такт с импульсами генератора 5, проходящими через элемент И 31. Процесс записи в узел 8 памяти аналогичен процессу записи в узел 7 памяти. На всем временном интервале записи информации в узел 8 памяти с узла 23 управления через элемент ИЛИ-НЕ 35 поступает сигнал запрета на блок 20 элементов И, чем исключается ложное срабатывание схемы 11 на время записи при превьше- нии значения выделенного кода блока 4 выделения максимума по сравнению

гистратора cлeдyюш x импульсных процессов с различными максималькьа- и амплитудами схема 11 выдает разрешес ние на работу того блока 3 или 4 выделения максимума, в котором вьщелен код максимума с меньшим из двух кодов значением. При этом запись в соответствующий узел 7 или 8 памяти

10 осуществляется только при том условии, что значение максимума очередного импульсного процесса превьппает значение выделенного предыдущего максимума работающего в данный момент

15 блока 3 или 4 выделения максимума. Информация, записанная ранее в узле 7 или 8 памяти, при повторной регистрации аннулируется.

Таким образом, на интервале анали20 за вьщеляются и регистрируются два импульсных процесса с максимальными амплитудами из серии процессов, поступивших на вход регистратора. По окончании интервала анализа счетчик

25 14 переполняется и вырабатывает сигнал запрета на формирователи 15 и 16

. управляющих сигналов, а через элемент НЕ 19 - сигнал разрешения на формирователи 17 и 18 управляющих

30 сигналоя о С этого момента узлы 22 и 23 управления переводятся в режим задания ;.вывода информации, а узлы 24 и 25 управления - в режим задания регистрации. Кроме того, по сигналу

35 со счетчика 14 интервала анализа формирователь 36 одиночных импульсов вырабатывает импульс обнуления регистров 38-41, а формирователи 15 и 16 управляющих сигналов вырабатывают /

40 одиночные импульсы, по которым формирователи 26 и 27 начального адреса устанавливают соответственно узлы 7 и 8 памяти в исходное состояние вывода информации,

45 На следующем интервале анализа, отсчитываемом счетчиком 14 интервала анализа, регистрация импульсных процессов, поступающих на вход регистратора, осуществляется в узлы 9 и 10 со значением кода, хранящегося в ёло 50 памяти при срабатывании блоков 3 и 4 ке 3 выделения максимума.выделения максимума, узлов 24 и 25 .

По окончании регистрации второго управления, формирователей 28 и 29 импульсного процесса запрет с блока начального адреса, формирователей 17 20 элементов И снимается и вновь и 18 управляющих сигналов и элемен- сравниваются схемой 11 значения вьще- 55 32 и 33, Процесс регистрации ленных кодов А и В максимумов в бло- при этом повторяется аналогично реках 3 и 4.гистрации в узлы 7 и 8 памяти, котоВ течение интервала анализа при рые на данном интервале анализа перемногократном поступлении на вход ре- водятся в режим вьшода зарегистрирогистратора cлeдyюш x импульсных процессов с различными максималькьа- и амплитудами схема 11 выдает разрешение на работу того блока 3 или 4 выделения максимума, в котором вьщелен код максимума с меньшим из двух кодов значением. При этом запись в соответствующий узел 7 или 8 памяти

осуществляется только при том условии, что значение максимума очередного импульсного процесса превьппает значение выделенного предыдущего максимума работающего в данный момент

блока 3 или 4 выделения максимума. Информация, записанная ранее в узле 7 или 8 памяти, при повторной регистрации аннулируется.

Таким образом, на интервале анализа вьщеляются и регистрируются два импульсных процесса с максимальными амплитудами из серии процессов, поступивших на вход регистратора. По окончании интервала анализа счетчик

14 переполняется и вырабатывает сигнал запрета на формирователи 15 и 16

управляющих сигналов, а через элемент НЕ 19 - сигнал разрешения на формирователи 17 и 18 управляющих

сигналоя о С этого момента узлы 22 и 23 управления переводятся в режим задания ;.вывода информации, а узлы 24 и 25 управления - в режим задания регистрации. Кроме того, по сигналу

со счетчика 14 интервала анализа формирователь 36 одиночных импульсов вырабатывает импульс обнуления регистров 38-41, а формирователи 15 и 16 управляющих сигналов вырабатывают /

одиночные импульсы, по которым формирователи 26 и 27 начального адреса устанавливают соответственно узлы 7 и 8 памяти в исходное состояние вывода информации,

На следующем интервале анализа, отсчитываемом счетчиком 14 интервала анализа, регистрация импульсных прованной на предыдущем интервале информации. Информация выводится из узлов 7 и 8 памяти поочередно через блок 37 элементов ИЛИ и выходной регистр 46 на выход регистратора по шине 49 синхронно с импульсами опроса от внешнего воспринимающего устройства, поступающими по входу 47. управления считыванием. При этом узел 7 памяти является ведушрм, а блок 8 памяти - ведомым, т.е. по окончании вьшода всего массива информации из узла 7 памяти на его выходе формируется сигнал разрешения на вывод информации из узла 8 памяти.

Таким образом, при выводе информации из узлов 7 и 8 памяти устраняется потеря входной информации за счет записи ее на данном интервале анализа в узлы 9 и 10 памяти. По окончании второго интервала анализа узлы 9 и 10 переключаются на поочередный вывод информации через блок 37 элементов ИЛИ и выходной регистр 46, а узлы 7 и 8 памяти - вновь на регистрацию следующих импульсных процессов.

Цикл, работы регистратора может повторяться многократно в течение всего времени проведения измерений, при этом весь временной интервал измерений разбивается на отдельные интервалы анализа, на каждом из которых производится вьщеление и регистрация двух импульсных процессов с максимальными амплитудами и одновременно обеспечивается вывод информации, зарегистрированной на предыдущем интервале анализа.

Формула изобретения

1е Цифровой регистратор импульсных процессов, содержащий тактовый генератор, аналого-цифровой преобра- зователь, регистр сдвига и первый блок регистрации, причем информационный вход аналого-цифрового преобразователя является одноимент 1м входом регистратора, первый выход тактового генератора соедш1ен с входом тактирования аналого-цифрового преобразователя, информационный выход которого соединен с информационным входом регистра сдвига, вход тактирования ко25

ных процессов с максимальными амплитудами и возможности одновременного вывода информации, зарегистрированно с ранее, в него введены с второго по четвертый блоки регистрации, два бло ка выделения максимума, два блока элементов И, схема сравнения, блок элементов ИЛИ, выходной регистр, 10 счетчик интервала, формирователь импульсов с двойным запуском, два элемента И, два элемента ИЛИ-НЕ и один элемент НЕ, причем информационные входы всех блоков регистрации соедн- 15 нены с выходом регистра сдвига, информационные выходы всех блоков регистрации соединены с соответствующими входами блока элементов ИЛИ, выход которого соедшшн с информациок- 20 ным входом выходного регистра, выход которого является информационным выходом регистратора, вход сштхрониза- ции выходного регистра соединен с входами управления считыванием всех блоков регистрации И С входом управления считыванием регистратора, второй выход тактового генератора соединен с входами тактирования всех блоков регистрации и со счетным входом счетчика интервала, выход старшего разряда которого соединен с входами разрешения первого и второго блоков регистрации, с входом запуска формирователя импульсов и через элемент 35 НЕ - с входами разрешения третьего и четвертого блоков регистрации., Bijxo- ды переполнения первого и третьего блоков регистрации соединены с одноименными входами соответственно вто- 40 рого и четвертого блоков регистрации, информационные входы первого и второго блоков выделения максимума соединены с информационным выходом анало- го-цифрового преобразователя, входы 45 тактирования первого и второго блоков

выделения максимума соединены с тре- тьим выходом тактового генератора, входы сброса первого и второго блоков выделения максимума соединены с выхо- 50 дом формирователя импульсов, выходы синхронизации пуска первого:и второго блоков вьщеления максимума соединены с первыми 1шформационными входа30

ми соответственно первого и второго торого соединен с вторым выходом так- 55 блоков элементов И, выходы максималь- тового генератора, отличаю- ного значения первого и второго бло- щий ся тем, что, с целью расшире ков выделения максимума соединены с НИЛ области применения за счет увели- вторыми информационными входами соот- чения числа регистрируемых импульс-ветственно первого и второго блоков

ных процессов с максимальными амплитудами и возможности одновременного вывода информации, зарегистрированной ранее, в него введены с второго по четвертый блоки регистрации, два блока выделения максимума, два блока элементов И, схема сравнения, блок элементов ИЛИ, выходной регистр, счетчик интервала, формирователь импульсов с двойным запуском, два элемента И, два элемента ИЛИ-НЕ и один элемент НЕ, причем информационные входы всех блоков регистрации соедн- нены с выходом регистра сдвига, информационные выходы всех блоков регистрации соединены с соответствующими входами блока элементов ИЛИ, выход которого соедшшн с информациок- ным входом выходного регистра, выход которого является информационным выходом регистратора, вход сштхрониза- ции выходного регистра соединен с входами управления считыванием всех блоков регистрации И С входом управления считыванием регистратора, второй выход тактового генератора соединен с входами тактирования всех блоков регистрации и со счетным входом счетчика интервала, выход старшего разряда которого соединен с входами разрешения первого и второго блоков регистрации, с входом запуска формирователя импульсов и через элемент НЕ - с входами разрешения третьего и четвертого блоков регистрации., Bijxo- ды переполнения первого и третьего блоков регистрации соединены с одноименными входами соответственно вто- рого и четвертого блоков регистрации, информационные входы первого и второго блоков выделения максимума соединены с информационным выходом анало- го-цифрового преобразователя, входы тактирования первого и второго блоков

выделения максимума соединены с тре- тьим выходом тактового генератора, входы сброса первого и второго блоков выделения максимума соединены с выхо- дом формирователя импульсов, выходы инхронизации пуска первого:и второго блоков вьщеления максимума соединены с первыми 1шформационными входа

элементов И, первые выходы первого и второго блоков элементов И соединены с первыми входами соответственно первого и второго элементов И, вторые выходы первого и второго блоков зле- Ментов И соединены соответственно с первым и вторым информационными входами схемы сравнения, выход признака Меньше или равно которой соединен с входом разрешения первого блока выделения максимума и с вторым входом первого элемента И, выход которого :соединен с входами пуска первого и третьего блоков регистрации, выход признака Больше схемы сравнения i соединен с входом разрешения второго ;блока выделения максимума и с вторым : входом второго элемента И, .выход iToporo соединен с входами пуска вто- :рого и четвертого блоков регистрации :вкод запрета первого блока элементов И соединен с выходом первого элемента ИЛИ-НЕ, первьй и второй входы которого соединены с выходами подтверждения соответственно второго и четвертого блоков регистрации, вход запрета второго блока элементов И соединен с выходом второго элемента ИЛИ НЕ, первый и второй входы которого соединены с выходами подтверждения соответстве шо первого и третьего блоков регистрации.

гистров соединены с входом сброса блока, вход записи первого регистра соединен с первым входом элемента И и с входом тактирования блока, выход признака Больше схемы сравнения соединен с вторым входом элемента И и с выходом синхронизации пуска бло-; ка, выход элемента И соед1шен с вхо- дом записи второго регистра, третий элемента И является входом разрешения блока.

s

Т1

s 6

ет

-1 г-Л -1

Ci-C

ЛО

rs

ГУ

Я С

О- и,

в

Ю

Wlb

.4

Г

1

Hft-Г/

Фиг. 5

15,16,17, f

УП

Фие.6

a,ii,J4,is

-Q- jiibQ-S I

ff

L-

Фаз. f

г %

о--Z

III

Фи9.9

СИ

20,2i

.J

Ш

Van

.J

Фиг,10

Авторы

Даты

1988-11-30—Публикация

1987-05-14—Подача