Изобретение относится к вычислительной технике и может быть применено для обнаружения ошибок нечетной кратности при передаче и хранении данных в двоичном коде. Известно устройство VlJ , содержащее ключи, группы элементов И и ИЛИ, позволяющее контролировать параллельный двоичный код. Недостатком устройства является невысокое быстродействие. Известно устройство по основному авт. свид. hfe 530332 2, содержащее триггер, два элемента И и регистр сдви- га, нулевые разрядные выходы которого соединены с входами первого элемента И выхоа которого соединен с первым входом второго элемента И, второй вход второго элемента И соединен с щиной тактовой частоты, а его выход - с входом сдвига регистра сдвига, выход которого соедине со счетным входом триггера, выход триггера является выходом устройства. Недостатком известного устройства является его низкое быстродействие и большой объем оборудования. Целью изобретения является повышение быстродействия и сокращение объема оборудования устройртва. Поставленная цель достигается тем, что устройство содержит группу двухвходовых элементов ИЛИ, число которых равно половине количества разрядов контролируемого кода, группу двухвходовых элементов И, группу трехвходовых элементов И и элемент задержки. Первый и второй входы каждого элемента ИЛИ группы соединены с первым и вторым входами соответствующего трехвходового элемента И группы, третьи входы которых соединены с выходом элемента задержки, вход которого соединен с первыми входами двухвходовых элементов И групп. Второй вход каждого двухвходового элемента И группы соединен с выходом соответствующего двухвходового элемента ИЛИ группы. Выходы двухвходовых элементов И группы соединены с еди-

ничными входами триггеров регистра сцвйга, нулевые входы которых соединены с выходами трехвходовых элементов И группы. Входы двухвходовых элементов ИЛИ группы и элемента задержки являются Входами устройства.. .,

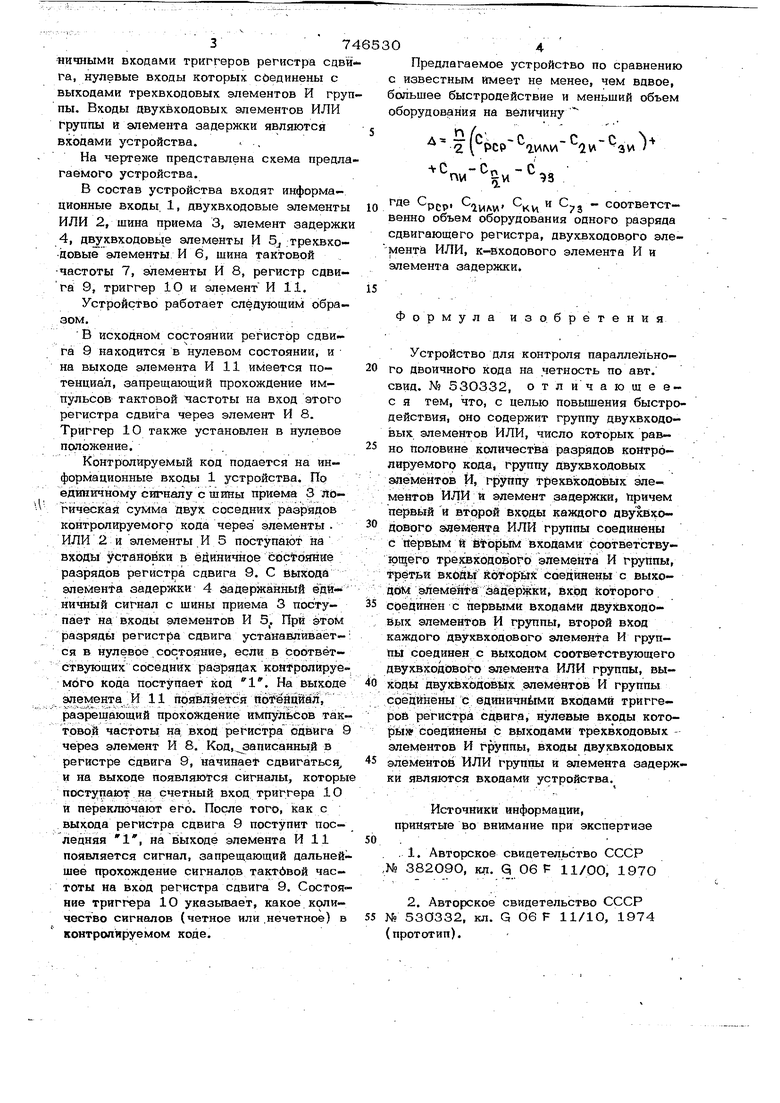

На чертеже представлена схема предлагаемого устройства.

В состав устройства входят информационные входы. 1, двухвходовые элементы ИЛИ 2, шина приема 3, элемент задержки 4, двухвходовые элементы И 5j трехвходовые элементы И 6, шина тактовой -частоты 7, элементы И 8, регистр сдвига 9, триггер 10 и элемент И 11.

Устройство работает следующим образом.

В исходном состоянии pet-истор сдвига 9 находится в нулевом состоянии, и на выходе элемента И 11 имеется потенциал, запрещающий прохождение импульсов тактовой частоты на вход этого регистра сдвига через элемент И 8. Триггер 10 также установлен в нулевое положение.

Контролируемый код подается на информационные входы 1 устройства. По единичному сигналу с шины приема 3 йо- гйческая сумма двух соседних разрядов контролируемого кода через элементыИЛИ 2 и элементы И 5 поступают на вкояы стййовки в ёйиничнсе состояние разрядов регистра сдвига 9. С выхода элемента задержки 4 задержанный ничный сигнал с шины приема 3 поступает на входы элементов И 5. При этом разряды регистра сдвига устанавливается в нулевое состояние, если в соответствующих соседних разрядах кон ролируембго кода поступает код 1. На выходе элементами 11 прявлйется по бйайал, разрешающий прохождение импул1ьсов тактовой частоты на, вход регистра сдвига 9 через элемент И 8. Код,.вписанный в регистре сдвига 9, начинает сдвигаться и на выходе появляются сигналы, которы поступают на счетный вход триггера 10 и переключают еГо. После того, как с выхода регистра сдвига 9 поступит последняя , на выходе элемента И 11 пойвляется сигнал, запрещающий дальнейшее прохождение сигналов тактбвой частоты на вход регистра сдвига 9. Состояние триггера Ю указывает, какое количество сигналов (четное или .нечетное) в контролируемом коде.

Предлагаемое устройство по сравнению с известным имеет не менее, чем вдвое, большее быстродействие и меньший объем оборудования на величину

(с- СС - С

2.(

РСР Т-ИЛИ И ЗИ

-с

эз

г-Де Сррр, , С и С.,3 - соответственно объем оборудования одного разряда сдвигающего регистра, двухвходового элемента ИЛИ, к-входового элемента И и элемента задержки

ормула изо. бретения

Устройство для контроля параллельного двоичного кода на четность по авт. свид. N9 53О332, отличающеес я тем, что, с целью повышения быстродействия, оно содержит группу двухвходовых элементов ИЛИ, число которых равно половине количества разрядов койтролируемого кода, группу двухвходовых элементов И, группу трехвходовых элемейтов Или н элемент задержки, причем первый И второй входы каждого двухвходового а емента ИЛИ группы соединены с первым и вторьгм входами соответствующего трехвходового элемента И группы, третьи входы которых соедннаны с выходом элемента задержки, вход которого соединен с первыми входами двухвходо8ых элементов И группы, второй вход каждого двухвходового элемента И группы соединен с выходом соответствующего двухвходового элемента ИЛИ группы, вы-

0 ходы двухвходовых элементов И группы соединены с бдяничн гми входами триггерОй регистра сдвига, нулевые входы котоjibi соедйяены с выходами трехвходовых элементов И группы, входы двухвходовых

элементов ИЛИ группы и элемента задержки являются входами устройства.

Источники информации, примятые во внимание при экспертизе

1.Авторское свидетельство СССР ..№ 382090, кл. Q Об Р 11/00, 1970

2.Авторское свидетельство СССР 55 № 530332, кл. G 06 F И/1О, 1974

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU962955A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Генератор псевдослучайных чисел | 1979 |

|

SU868734A1 |

| Устройство для контроля параллельного кода на четность | 1979 |

|

SU883910A1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| Устройство для определения максимальной последовательности из @ @ -разрядных двоичных чисел | 1983 |

|

SU1096638A1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

| Преобразователь кодов | 1975 |

|

SU763885A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-03—Подача