Изобретение относится к вычислительной технике-и может быть использовано в составе вычислительного комплекса автоматизированных систем контроля и управления.

Известно устройство для контроля параллельного двоичного кода на четность, содержащее триггер, регистр и элементы И tl

Недостатком устройства является низкое быстродействие.

Известно также устройство для контроля параллельного двоичного кода на четность, содержащее группу элементов ИЛИ, две группы элементов И и (Элемент задержки, причем первый и второй входы каждого элемента ИЛИ группы соединены с первым и вторым входами соответствующего трехвходового элемента И группы, третьи входы которых соединены с выходом элемента задержки, вход которого соединен с первыми входами двухвходовых элементов И группы, второй вход каждого элемента И первой группы соединен с выходом соответствующего двухвходового элемента ИЛИ группы, выходы элементов И первой группы соединены с единичными входами триггеров регистра сдвига, нулевые входы которыхJDO,еданены с выходами элементов И второй группы, входы элементов ИЛИ группы и элементы задержки являются входами устройства 2.

Недостатком данного устройства является большой объем оборудования.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля двоичного

10 кода на четность, содержащее распределитель импульсов, группу элементов И, три элемента ИЛИ, два триггера и два элемента И, причем вход распределителя импульсов является одним из

15 входов устройства, первые входы каждого элемента И группы являются входами соответствующих контролируемых разрядов, вторые входы элементов И группы попарно объединены и подклю20чены к.соответствующим выходам распределителя импульсов, выходы элементов И нечетных разрядов группы соединены с входами первого элемента ИЛИ, выхода четных разрядов соединены с

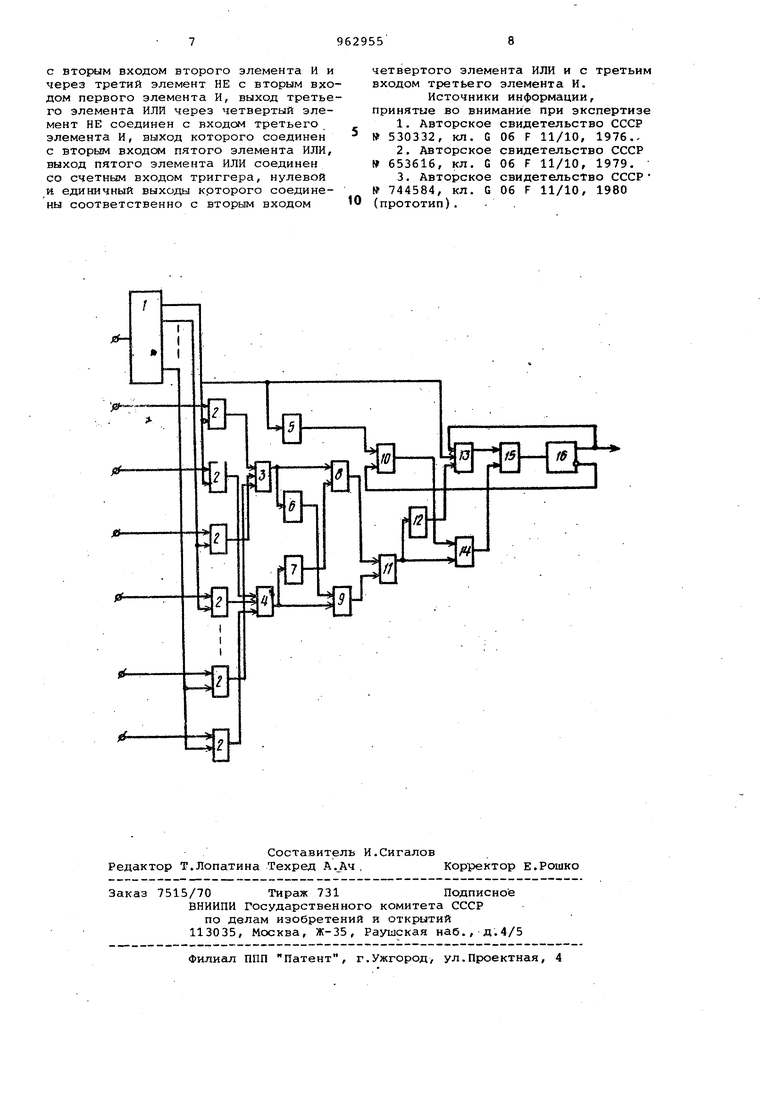

25 входами второго элемента ИЛИ, выход которого подключен к счетному входу второго триггера, первый выход распределителя импульсов соединен с нулевыми входами триггеров, выход пер30 .вого элемента ИЛИ подключен к счетному входу первого триггера, единичный выхо,, которого подключен к перво му входу первого элемента И, нулевой выход второго триггера соединен с вторым входом первого элемента И, вы ход которого подключен к первому вхо ду третьего элемента ИЛИ, единичный выход второго триггера соединен с первым входом второго элемента И, нулевой выход первого триггера, соединен с вторым входом второго элемента И, выход которого подключен к вто рому входу третьего элемента ИЛИ, вы ход которого является выходом устройства 3 . Недостатком устройства является низкое быстродействие. Цель изобретения - повышение быст родействия. Поставленная цель достигается тем что в устройство для контроля двоичного кода на четкость, содержащее распределитель импульсов, группу эле ментов И, первый, второй и третий элементы ИЛИ, триггер, первый и второй элементы И, причем вход распреде лителя импульсов является тактовым входом устройства, первые входы каж|дого элемента И группы являются входами соответствующих контролируемых разрядов устройства, вторые входы элементов И группы попарно объединены и подключены к соответствующим выходам распределителя импульсов, выходы нечетных элементов И группы соединены с соответствующими входами первого элемента ИЛИ, выходы четных элементов И группы соединены с соответствующими входами второго элемента ИЛИ, выходы первого и второго эле ментов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, единичный выход триггера является выходом устройства, введены первый, второй, третий, и чет вертый элементы НЕ, четвертый и пятый элементы ИЛИ, третий и четвертый элементы И, причем первый выход распределителя импульсов соединен с пер вым входом третьего элемента И и через первый элемент НЕ - с первым вхо дом четвертого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выход третьего элемента ИЛИ соединен с вторым входом четвертого элемента И, выход которого соединен с первым входом пя того элемента ИЛИ, выход первого эле .мента ИЛИ соединен с первым входом первого элемента И и через второй элемент НЕ с первым входом второго элемента И, выход второго элемента ИЛИ соединен с вторым входом второго элемента И и через третий элемент НЕ с вторым входом первого элемента И, выход третьего элемента ИЛИ через четвертый элемент НЕ соединен с входом третьего элемента И,выход которого соединен, с вторым входом пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен со счетным входом триггера, нулевой ii единичный выходы которого соединены соответственно с вторым входом четвертого элемента .ИЛИ и с третьим входом третьего элемента И. На чертеже представлена структурная схема устройства для контроля двоичного кода на четность. Устройство содержит распределитель 1импульсов, группу элементов 2 И, первый и второй элементы 3 и 4 ИЛИ, первый,, второй, и третий элементы 5-7 НЕ, первый и второй элементы 8 и 9 И, третий и четвертый элементы 10 и 11 ИЛИ четвертый элемент 12 НЕ, третий и четвертый элементы 13 и 14 И, пятый элемент 15 ИЛИ и триггер 16. Вход распределителя 1 импульсов является одним из входов устройства. Первый выход распределителя 1 импульсов соединен с входом элемента 5 НЕ и с первым входом элемента 13 И. Первые входы каждого элемента 2 И группы являются входами соответствующих контролируемых разрядов устройства, вторые входы, элементов 2 И группы попарно объединены и подключены к соответствующим выходам распределителя 1 импульсов, выходы элементов 2 И нечетных разрядов группы соединены с входами первого элемента 3 ИЛИ, выходы элементов 2И четных разрядов группы соединены с входами второго элемента 4 ИЛИ, выход которого подключен к входу третьего элемента 7 НЕ, и к второму входу второго элемента 9 И, выход первого элемента 3 ИЛИ соединен с входом второг® элемента 6 НЕ и с первым входом первого элемента 8 И, выход второго элемента 6 НЕ подключен к первому входу второго элемента 9 И, выход которого соединен с вторым входом -третьего элемента 11 ИЛИ, выход третьего элемента 7 НЕ подключен к второму входу первого элемента 8 И, выход которого соединен с первым входом третьего элемента 11 ИЛИ, выход которого подключен к входу .четвертого элемента 12 НЕ и второму входу четвертого элемента 14 И, выход первого элемента 5 НЕ соединен с первым входом четвертого элемента 10 ИЛИ, нулевой выход триггера 16 подключен к второму входу четвертого элемента 10 ИЛИ, выход которого соединен с первым ВХОДОМ четвертого элемента 14 И, выход которого подключен к второму входу пятого элемента 15 ИШ, выход четвертого элемента 12 НЕ соединен с вторым входом третьего элемента 13 И, единичный выход триггера 16 подключен к третьему входу третьего элемента 13 И, выход которого соединен с первым входом пятого элемента 15 ИЛИ, выход которого подключей к счетному входу триггера 16. ЕДИНИЧНЫЙ выход триггера 16 является выходом устройства. Устройство для контроля двоичного кода на четность работает следующим образом. Импульсы с выходов распределителя 1 поочередно поступают на соединенны попарно вторые входы элементов 2 И нечетного и четного разрядов контролируемого кода. Импульсы с выходов элементов 2 И поступают попарно на соответствующие входы элементов 3 и 4 ИЛИ (3 ИЛИ - нечетные разряды, 4 ИЛИ - четные). Если в паре разрядов контролируемого коДа два нуля или две единицы, то на выходе элемен тов 8 и 9 И и 11 ИЛИ появляется нулевой сигнал, а если в одном из пары разрядов единица, то на выходе элемента 11 ИЛИ появляется единичный сигнал. Пусть триггер 16 находится в единичном состоянии и на первом выходе распределителя 1 импульсов единичный сигнал. Тогда, если в паре разрядов две единицы или два нуля, то на выходе элемента 13 И единичный сигнал (на первом входе - единичный сигнал с единичного выхода триггера 16, на втором входе - единичный сигнал с первого выхода распределителя импуль сов, на третьем входе - единичный сигнал с выхода элемента 12 НЕ), который устанавливает через элемент 15 ИЛИ триггер 16 в нулевое состояние. Если триггер находится в нулевом состоянии, то на выходе элемента 15 ИЛИ устанавливается ну:51евой сигнал, не меняющий, состояние триггера. Если в одном из двух контролируемых разрядов единица, то на выходе элемента 11 ИЛИ - единичный сигнал. В том случае, когда триггер 16 находит ся в единичном состоянии, на выходе элементов 13-15 ИЛИ устанавливаются нулевые сигналы и состояние триггера не меняется. А если триггер находится в нулевом состоянии, то на выходе элементов 10 ИЛИ, 14 И и 15 ИЛИ нахо дится единичный сигнал, который уста навливает триггер в единичное состояние . Таким образом, в первом такте работы (единичный сигнал на первом выходе распределителя 1 импульсов) триггер 16 независимо от исходного положения устанавливается в единично состояние, если в одном разряде первой пары контролируемого кода нуль, а в другом - единица, и в нулевое состояние, если в двух разрядах нули или единицы. При отсутствии единичного сигнала на первом входе распределителя 1 импульсов триггер 16 изменяет своё сос тояние, если контролируемая пара оаз рядов содержит один нуль и одну единицу, и не меняет свое состояние, если разряды содержат два нуля или две единицы. Следовательно, если в результате контроля в исходном коде .выявлено нечетное число единиц, то на единичном выходе триггера 16 устанавливается единичный сигнал, а если четное число единиц - нулевой. Таким образом, использование введенных элементов повышает быстродействие устройства, а также уменьшает аппаратурные затраты путем сокращения объема оборудования. , При этом выигрыш составит: Та й/2 i-i .где п - число разрядов контролируе|мого двоичного кода. Формула изобретения I Устройство для контроля двоичного кода на четность, содержащее распределитель импульсов, группу элементов И, первый, второй и третий элементы ИЛИ, триггер, первый и второй элементы И, причем вход распределителя импульсов является тактовым входом устройства, первые входы каждого элемента И группы являются входами соответствующих контролируемых разрядов устройства, вторые входы элементов И группы попарно объединены и подключены к соответствующим выходам распределителя импульсов, выходы нечетных элементов И группы соединены с соответствующими входами первого элемента ИЛИ, выходы четных элементов И группы соединены с соответствующими входами второго элемента ИЛИ, выходы первого и второго элементов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, единичный выход триггера является выходом устройства, отлич а-юще е с я тем, что, с целью повышения быстродействия, в устройство введены первый, второй, третий и четвертый элементы НЕ, четвертый и пятый элементы ИЛИ, третий и четвертый элементы И, причем первый выход распределителя импульсов соединен с первым входом третьего элемента И и через первый элемент НЕ - с первым входом четвертого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, выход третьего элемента ИЛИ соединен с вторым входом четвертого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом первого эле.мента И и через второй элемент НЕ с первым входом второго элемента И, выход второго элемента ИЛИ соединен

с вторым входом второго элемента И и через третий элемент НЕ с вторым входом первого элемента И, выход третьего элемента ИЛИ через четвертый элемент НЕ соединен с входом третьего элемента И, выход которого соединен с вторым входом пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен со счетным входом триггера, нулевой и единичный выходы крторого соединены соответственно с вторым входом

четвертого элемента ИЛИ и с третьим входом третьего элемента И.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 530332, кл. G Об F 11/10, 1976.2.Авторское свидетельство СССР 653616, кл. G 06 F 11/10, 1979.

3.Авторское свидетельство СССР 744584, кл. G 06 F 11/10, 1980

(прототип). - .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода на четность | 1978 |

|

SU744584A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для сравнения числа единиц в двоичных кодах | 1988 |

|

SU1509867A2 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для определения четности информации | 1981 |

|

SU1013959A1 |

| Устройство для контроля двоичного кода на нечетность | 1981 |

|

SU1012261A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для сравнивания рефлексных кодов | 1972 |

|

SU458823A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

Авторы

Даты

1982-09-30—Публикация

1981-03-23—Подача