1

Изобретение относится к области вычислительной техники и может быть использовано в устройствах ввода-вывода и преобразования информации.

Известен преобразователь кодов из 5 двоичной системы в двоично-десятичную 1 , .содержащий в каждой тетраде четырехразрядный триггерный регистр сдвига и корректирующий блок, состоящий из тринадцати комбинацион- Ю ных логических элементов. Это устройство реализует алгоритм преобразования, заключакидийся в сдвиге входного кода на один разряд по каждому такту преобразования и коррек- 15 ции полученного в результате сдвига двоично-десятичного кода.

Известный преобразователь требует для своей реализации большое количчество оборудования и не обеспечива- 20 ет возможности преобразования последовательного кода Грея в двоично-десятичный код 8,- 4, 2, 1.

Цель изобретения заключается в уменьшении количества оборудования 25 и обеспечении возможности преобразования последовательного кода Грея в двоично-десятичный код.

Цель достигается тем, что в каждой тетраде шина установки режима 30

преобразования соединена с вторым входом первого триггера и с первым входом первого двухвходового элемента И-НЕ, выход, которого подключен к четвертому входу первого триггера. Прямой вход тетрады связан с пятым входом, а инверсивный вход - с третьим входом первого триггера. Шина синхронизации подсоединена к синхронизирующим входам первого, второго, третьего и четвертого триггеров, а шина логической единицы - к вторым входам второго, третьего и четвертого триггеров. Прямой выход первого триггера соединен с его первым входом, с пятым входом второго триггера и с вторым входом первого двухвходового элемента И-НЕ, а инверсивный выход первого триггера - с третьим входом второго триггера и с первыми входами первого и второго трехвходовых элементов И-НЕ и четвертого двухвходового элемента И-НЕ. Прямой выход второго триггера подключен к пятому входу третьего триггера и к второму входу второго трехвходового элемента И-НЕ, а инверсивный выход второго триггера - к третьему входу третьего триггера и к второму входу первого трехвходового элемента: .Прямой выхо третьего триггера связан с пятым входом четйёртого триггера и с третьими входами первого и второго трехвхо- довых элементов И-НЕ, а инверсивный выход третьего триггера - с третьим входом четвертого триггера и с первым входом второго двухвходового элемента И-НЕ. Прямой и инверсивный выходы четвертого триггера, являющиеся прямым и инверсивным выходами тетрады, подсоединены соответственно к вторым входам четвертого и второго двухвходовых элементов И-НЕ. Выходы первого трехвходового элемента И-НЕ и второго двухвходового элемента И-НЕ подсоединены к входам третьего двухвходового элемента И-НЕ, выход которого связан непосредственно с четвертым входом и через первый элемент НЕ с первым входом второго триггера. Выходы второго трехвходового элемента И-НЕ и четвертого двухвходового элемента И-НЕ подключены к входам пятого двухвходового элемента И-НЕ, выход которого подсоединен непосредственно к первому входу и через второй элемент НЕ к четвертому входу третьего триггера. Выход третьего трехвходового элемента И-НЕ, подсоединенного входами к выходам первого трехвходового элемента И-НЕ и второго и четвертого двухвходовых элементов И-НЕ, связан непосредственно с четвертым входом и через третий элемент НЕ с первым входом четвертого триггера. Выходы третьего двухвходового элемента И-Н и первого элемента НЕ являются также инверсивным и прямым выходами переноса данной тетрады.

Каждый разрядный триггер, на основе которых выполнен регистр сцвига, построем из пяти элемертов И-НЕ и элемента И-ИЛИ-НЕ. Первый вход триггера соединен с первым входом первого элемента И, входящего в состав элемента И-ИЛИ-НЕ, второй вход триггера соединен с вторымвходом, а третий вход - с третьим входом этого же элемента. Четвертый вход триггера подключен к первому входу второго элемента И, входящего в состав элемента И-ИЛИ-НЕ, пятый вход триггера подключен к второму, а логическая единица - к третьему входу этого же элемента. Выход элемента И-ИЛИ-НЕ подсоединен к первому входу первого элемента И-НЕ и к BTODpMy входу пятого элемента И-НЕ. Синхронизирующий вход триггера связан с вторым входом первого элемента И-НЕ и с первым входом третьего элемента И-НЕ, выход которого соеди нен с третьим входом первого эле. мента И-НЕ, вторым входом четвертого элемента И-НЕ и первым входом

пятого элемента И-НЕ. Выход пятого элемента И-НЕ подключен к второму входу, третьего элемента И-НЕ, Выход первого элемента И-НЕ связан с четвертыми входами первого и второго элементов И, входящих в состав элемента И-ИЛИ-НЕ, и с вторым входом второго элемента И-НЕ, выход которого, являющийся инверсивным выходом триггера, подсоединен к первому входу четвертого элемента И-НЕ.

0 Выход четвертого элемента И-НЕ является прямым выходом триггера и соединен с третьим входом второго элемента И-НЕ. Первый вход второго элемента И-НЕ и третий вход четвертого элемента И-НЕ являются соответственно входами установки триггера в нуль и установки триггера в единицу.

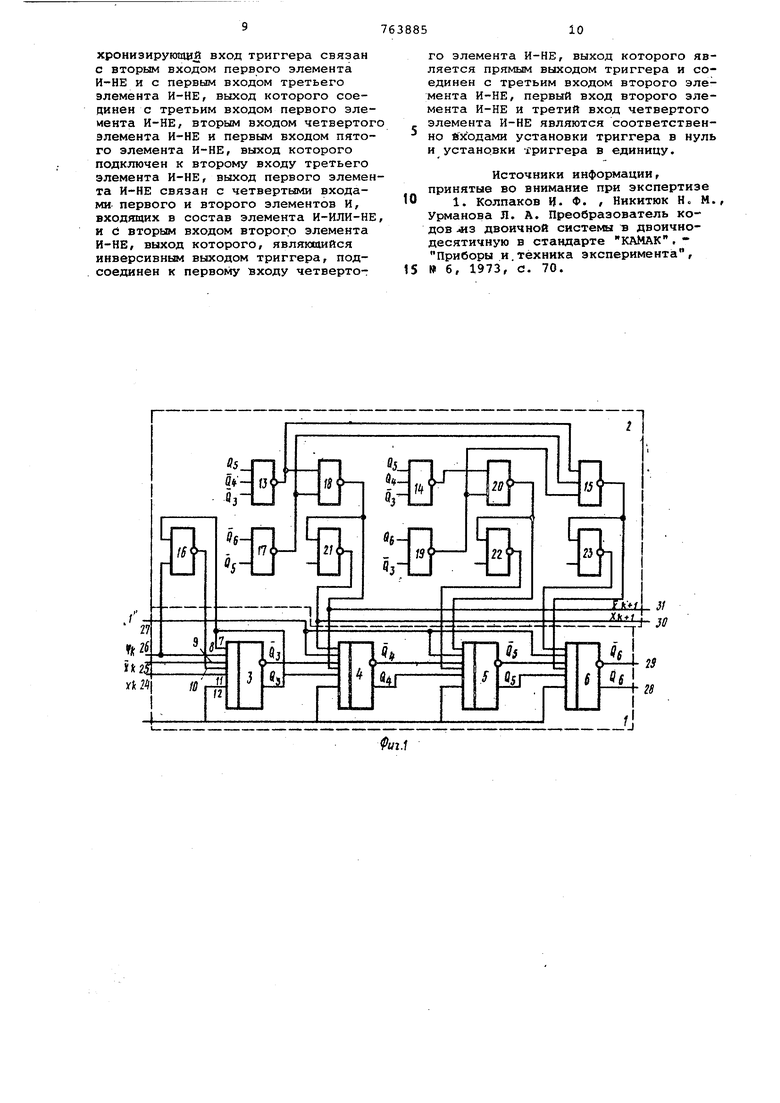

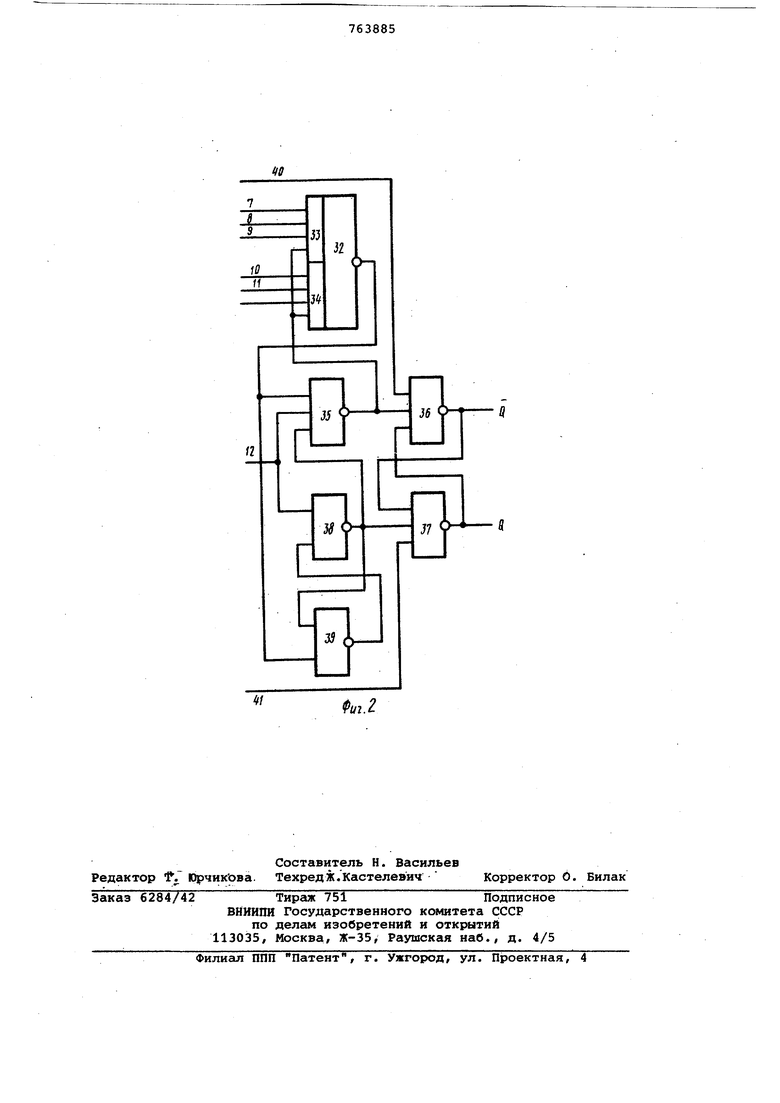

На фиг. 1 представлена функциональная схема одной тетрады преобразователя кодов; на фиг. 2 - функциональная схема триггера, используемого в преобразователе.

Тетрада преобразователя кодов содержит четырехразрядный регистр сдвига 1 и корректирующий блок 2. Регистр Сдвига включает в себя первый 3, второй. 4, третий 5 и четвертый б разрядные триггеры, каяодый из которых

Q имеет первый 7, второй 8, третий 9, четвертый 10, пятый 11 входы и вход 12 синхронизации. Корректирующий блок состоит из трехвходовых элементов И-НЕ 13-15, двухвходовых элементов И-НЕ 16-20 и элементов НЕ 21-23. Входы 24 и 25 являются прямым и инверсивным входами тетрады, шина 26 шиной уотановки режима преобразования, а шина 27 - шиной логической единицы. Выходы 28 и 29 представляют

0 собой прямой и инверсивный выходы тетрады, а выхо,ды 30 и 31 - выходы переноса.

Разрядный триггер фиг. 2J содержит элемент И-ИЛИ-НЕ 32, в который

5 входят элементы И 33 и 34, трехвходовые логические элементы И-НЕ 35-37 и двухвходовые элементы И-НЕ 38 и 39. Входы 40 и 41 являются входами установки триггера в ноль и в единицу

Q соответственно.

При подаче, например, на входы 7 и 10 триггера сигналов, соответствующих прямому и инвертированному значению одной логической переменной-. на входы 9 и 11 сигналов, соответствующих инвертированному и прямому значению другой логической переменной, и при наличии на входе 8 сигнала логической единицы триггер по синхроимпульсу, поступающему на

0 вход 12, устанавливается в состояние, -соответствующее сумме по модулю два значений обеих логических переменных.

При нгшичии на входе 8 сигнала,

5 :::оответствующего логическому нулю. а на входах.10 и 11 сигналов, соот ветствующих логическрйединице, что означает равенство единице первой и равенство нулю второй логических переменных, триггер выполняет Функ цию элемента задержки входной пере менной на один такт. Устройство работает следующим образом. Обратная связь с прямого выхода триггера 3 непосредственно на его вход 7 и через управляемый по второму входу сигналом установки режима преобразования S элемент И-НЕ 16 на вход 10 этого триггера-обеспечивает при значении , соответ ствующем логической единице, ело- . жение по модулю два значения, соответствующего состоянию триггера в момент времени t, со значением входного стенала х на входе 1Г триггера в тот же момент времени t Таким образом, при наличии сигнала соответствующего логической единице, на шине 26 и, следовательно, на входе элемента И-НЕ 16, а также на входе 8 .триггера 3 тетрада преобразователя осуществляет сдвиг и оррекцию двоично-десятичного кода тет рады по тактовым синхроимпульсам, а триггер 3 одновременно с этим выпол няет операцию сложения по модулю два значений входных сигналов Х и сигналов do, на выходе триггера 3 Так как переносы следующую тетраду представпядот собой позиционный двоичный код, то такой алгоритм работы триггера 3 необходим только в младшей тетраде при преобразовании последовательного кода Грея в двоично-десятичный код. Следовательно, при таком преобразовани на шину 26 младшей тетрады преобра.зователя должен быть подан сигнал, соответствующий логической единице а на эти же шины всех последующих тетрещ преобразователя должен быть подан сигнал, соответствующий логическому нулю, т.е. Ч, 1, а S О где к 2, 3, 4,... При преобразовании в двоично-десятичный код позиционного двоичного кода необходиМО, чтоЪы Q для всех к 1, 2 J f л f « Пусть подлежащая преобразованию в двоично-десятичный код 8, 4, 2, комбинация кода Грея следующая: 10110111, что соответствует двоично позиционному коду 11011010. Десятич ным эквивалентом этого кбда являет ся число 218, двоично-десятичное представление которого 0010, 0001, 1000. Исходное сотояние преобразов теля следующее: Qi. 0; 1 5, 1; Ф-.Л О, х 1 х„ 1 ... О, где Qy - состояние триггера -i,j , L 3, 4, 5, 6 - позиция триггера в тетраде согласно обозначениям на фиг.1, j 1, 2, 3,.., - номер тетрады преобразователя. Таким образом, на входы 7 триггеров 3.J воздействуют сигналы, соответствующие логическому нулю, на вход 8 триггера 3.1 воздействует сигнал, соответствующий логической единице, а на входы 8 триггеров 3 всех последующих тетрад воздействуют сигналы,, соответствующие логическому нулю. На вход 9 триггера 3.1 воздействует сигнал, соответствующий логическому нулю, а на входы 9 триггеров 3 всех последующих тетрад воздействуют сигналы, соответствующие логической единице. Аналогично можно установить, что на входах 10 триггеров 3.J присутствуют сигналы единицы, на входе 11 триггера 3.1 - сигнал единицы, на входах 11 триггеров 3 остальных тетрад - сигналы нуля, на входах 7 и 11 триггеров 4.J ,5.j , 6.j - сигналы нуля, а на входах 8, 9, 10 этих триггеров - сигналы единицы. При таком начальном состоянии преобразователя и в случае продвижения преобразуемого кода старшими разрядами вперед при поступлении первого тактового синхроимпульса младшая тетраща переходит в состояние 0001, а состояния остальных тетрад не изменяются. Так как после этого ij,i .-. QM Д1 л - QSJ Ь.л ° (j 2, 3, 4. . .) ; :П Т- J. г - U f Х Х X., . . . О, то на входах 7, 8 и 9 триггера 3.1 присутствует сигнал единицы, на входах 10 и 11 триггера 3.1 - сигнал нуля, на вход 9 триггера 4.1 воздействует сигнал логического нуля, на вход 11 этого триггера - сигнал логической единицы, на входах 7-11 остальных триггеров значения сигналов не изменяются. Следовательно, после второго синхроимпульса младшая тетрада преобразователя установлена в состояние ООН, а состояния тетрад не изменяются. Происходящее в результате изменения состояний разрядных триггеров изменение сигналов на их входах приводит к тому, что после третьего синхроимпульса тетрады преобразователя устанавливаются в состояние 0000, 0000,0110, после четвертого 0000, 0001, ООН, после пятого 0000, 0010, 0111, после шестого 0000,0101, 0100j после седьмого 0001,0000, 1001, и, наконец, после восьмого синхроимпульса в регистре

сдвига хранится код 0010, 0001, 1000 что является двоично-десятичным представлением числа 218.

При преобразовании позиционного двоичного кода в двоично-десятичный код устройство работает аналогично, однако при этом необходимо исключить операцию сложения по модулю два значения кода, хранящегося в младшем разрядном триггере младшей тетрады преобразователя, с очередным значением разряда кода на входе преобразователя. Для этого на шине 26 установки режима преобразования должен быть установлен сигнал, соответствующий логическому нулю.

Преобразователь кода, выполненный согласно изобретению требует для своей реализации четыре разрядных триггера и одиннадцать логических элементов на каждую тетраду, т.е. на два логических элемента меньше, чем известное устройство, и позволяет производить преобразование в двоично-десятичный кол не только позиционного кода, но и кода Грея.

При преобразовании кода Грея происходит повышение быстродействия устройства за счет совмещения преобразования кода Грея в позиционный двоичный код с преобразованием последнего в двоично-десятичный код.

Формула изобретения

1. Преобразователь кодов, содержащий в каждой тетраде четырехразрядный триггерный регистр сдвига и корректирующий блок, выполненный на комбинационных логических элементах, отличающийся тем, что, с целью уменьшения количества оборудования и обеспечения возможности преобразования последовательного кода Грея в двоично-десятичный код, шина установки режима преобразования со.единена с вторым входом первого триггера и с первым входом первого двухвходового элемента И-НЕ, выход которого подключен к четвертому входу первого триггера, прямой вход тетрады связан с пятым входом, а инверсивный вход - с третьим входом первого триггера, шича синхронизации подсоединена к синхронизирующим входам первого, второго, третьего и четвертого триггеров, а шина логической единицы - к вторым входам второго, третьего и четвертого триггеров, прямой выход первого триггера соединен с его первым входом, с пятым входом второго триггера и с вторым входом первого двухвходового элемента И-НЕ, а инверсивный выход первого триггера - с третьим входом второго триггера и с первыми входами первого и второго трехвходовых элементов И-НЕ и четвертого двухвходового элемента И-НЕ, прямой выход второго триггера подключен к входу третьего триггера и к второму входу второго трехвходового элемента И-НЕ, а инверсивный выход второго триггера к третьему входу третьего триггера и к второму входу первого трехвходового элемента И-НЕ, прямой выход третьего триггера связан с пятым входом четвертого триггера и с третьими входами первого и второго трехвходовых элементов И-НЕ, а инверсивный выход третьего триггера - с третьим входом четвертого триггера и с перВЕлм входом второго двухвходового элемента И-НЕ, прямой и инверсивный выходы четвертого триггера, являющиеся Прямым и инверсивным выходами тетрады, подсоединены соответственно к вторым входам четвертого и второго двухвходовых элементов -И-НЕ, выходы первого трехвходового элемента И-НЕ и второго двухвходового элемента И-НЕ подсоединены к входам третьего двухвходового элемента И-Н выход которого связан непосредственно с четвертым входом и через первый элемент НЕ с первым входом второго триггера, выходы второго трехвходового элемента И-НЕ и четвертого двухвходового элемента И-НЕ подключены к входам пятого двухвходового элемента И-НЕ, выход которого подсоединеннепосредственно к перво входу и через второй элемент НЕ к четвертому входу третьего триггера, выход третьего трехвходового элемента И-НЕ, подсоединенного входами к выходам ..первого трехвходового элемента И-НЕ и второго и четвертого двухвходовых элементов И-НЕ, связан непосредственно с четвертым входом и через третий элемент НЕ с первым входом четвертого триггера, а выходы третьего двухвходового элемента И-НЕ и первого элемента НЕ являются также инверсивным и прямым выходами переноса данной тетрады.

2. Преобразователь кодов по п. 1 отличающийся тем, что разрядный триггер построен из пяти элементов И-НЕ и элемента И-ИЛИ-НЕ, причем первый вход триггера соединен с первым входом первог.о элемента И, входящего в состав элемента И-ИЛИ-НЕ, второй вход, .триггера соединен с вторым входог, а третий вход - с третьим взводом этого же элемента, четвертый вход триггера подключен к первому входу второго элемента И, входящего в состав элемента И-ИЛИ-НЕ, пятый вход триггера подключен к второму, а вход логической единицы - к третьему входу этого же элемента, выход элемента И-ИЛИ-НЕ подсоединен к первому входу первого элемента И-НЕ и к второму входу пятого элемента И-НЕ, сиихронизИРУ клад и вход триггера связан с BTOpfcJM входом первого элемента И-НЕ и с первым входом третьего элемента И-НЕ, выход которого соединен с третьим входом первого элемента И-НЕ, вторым входом четвертого элемента И-НЕ и первым входом пятого элемента И-НЕ, выход которого подключен к второму входу третьего элемента И-НЕ, выход первого элемента И-НЕ связан с четвертыми входами- первого и второго элементов И, входящих в состав элемента И-ИЛИ-НЕ, и d вторым входом второго элемента И-НЕ, выход которого, являющийся инверсивным выходом триггера, подсоехсинен к первому входу четвертого элемента И-НЕ, выход которого является прямым выходом триггера и соединен с третьим входом второго элемента И-НЕ, первый вход второго элемента И-НЕ и третий вход четвертого элемента И-НЕ являются соответственно входами установки триггера в нуль и установки триггера в единицу.

Источники информации, принятые во внимание при экспертизе

1. Колпаков И. Ф. Никитюк И., М., Урманова Л. А. Преобразователь кодов мз двоичной системы двоичиодесятичную в стандарте КАМАК. Приборы и.техника эксперимента,

№ б, 1973,с. 70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования интервалов времени в цифровой код | 1985 |

|

SU1411701A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Преобразователь кода грея в двоичный код | 1977 |

|

SU658556A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Счетчик последовательности импульсов | 1974 |

|

SU538492A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Многоканальное устройство контроля температурных режимов инкубаторов | 1983 |

|

SU1157528A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1005027A1 |

Авторы

Даты

1980-09-15—Публикация

1975-12-08—Подача