Изобретение относится к автоматике и вычислительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, в измерительных и вычислительных устройствах, устройствах обработки аудио и видео сигналов, а также при разработке элементов импульсных нейронных сетей, в частности прототипов импульсных нейронов.

Известно устройство [RU Патент № 2015539, опубл. 30.06.94] для деления частоты с переменным коэффициентом деления, содержащее n-разрядный двоичный счетчик, входы синхронизации, разрешения счета, установки в начальное состояние и разрешения деления, являющиеся соответствующими входами счетчика, выход переполнения, являющийся соответствующим выходом счетчика, n-разрядная шина управления, информационный выход делителя частоты, n логических элементов с функцией И, первые входы которых соединены соответственно с прямыми разрядными выходами n-разрядного счетчика, а вторые входы этих элементов соединены с n-разрядами шины управления в обратном порядке, причем делитель частоты содержит также двухвходовой элемент И-НЕ, а логические элементы с функцией И по двум входам реализуют еще функцию 2ИЛИ, по выходам - функцию НЕ, составляя таким образом функцию 2ИЛИ-И-НЕ, кроме того, первый вход элемента И-НЕ соединен с выходом первого логического элемента, составляющего функцию 2ИЛИ-И-НЕ, а второй вход - с инверсным выходом синхронизации двоичного счетчика, при этом выход элемента И-НЕ является информационным выходом делителя частоты, выход расширения которого соединен с выходом первого логического элемента 2ИЛИ-И-НЕ, третьи входы всех логических элементов 2ИЛИ-И-НЕ соединены соответственно с инверсными разрядными выходами n-разрядного двоичного счетчика, четвертый вход i-го элемента 2ИЛИ-И-НЕ (i=1, n–1) соединен с выходом (i+1)-го элемента 2ИЛИ-И-НЕ, четвертый вход n-го элемента 2ИЛИ-И-НЕ является входом расширения делителя частоты, причем первые и вторые входы всех логических элементов 2ИЛИ-И-НЕ относятся к первому элементу ИЛИ, а третьи и четвертые входы–ко второму элементу ИЛИ.

Устройство осуществляет деление за счет последовательного преобразования потенциальных (по отношению к сигналу на входе синхронизации) управляющих сигналов с шины управления и от разрядов счетчика на элементах 2ИЛИ-И-НЕ, включенных последовательно, с выделением выходного информационного сигнала из потенциального (по отношению к сигналу на входе синхронизации) сигнала на выходе расширения делителя. Сигнал на выходе расширения получается путем последовательного преобразования с использованием элементов 2ИЛИ-И-НЕ сигналов от прямого и инверсного выходов разряда счетчика, сигнала с шины управления и сигнала с выхода последующего элемента 2ИЛИ-И-НЕ. Элементы 2ИЛИ-И-НЕ образуют итеративную (последовательную) цепочку, в которой на каждом элементе на первой ступени в первой паре сигнал с выхода каждого последующего элемента преобразуется с сигналом с инверсного выхода счетчика, во второй паре сигнал с шины управления преобразуется с сигналом от прямого выхода счетчика, причем на нечетный элемент 2ИЛИ-И-НЕ поступает инверсный управляющий сигнал с шины управления, а на четный–прямой сигнал с шины управления, затем на второй ступени сигналы обеих пар преобразуются в сигнал выхода элемента 2ИЛИ-И-НЕ.

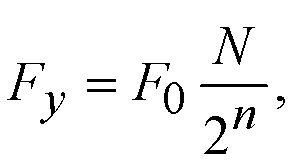

Средняя частота Fy импульсного потока на выходе элемента И-НЕ, то есть на выходе устройства, определяется выражением

где N - код, поступающий по n-разрядной шине управления,

F0 - частота, поступающая на вход синхронизации.

Недостатком этого устройства является большое время преобразования, связанное с последовательной обработкой сигналов.

Из числа аналогов наиболее близким по технической сущности является делитель частоты с переменным коэффициентом деления [RU Патент № 2273043, опубл. 27.03.2006], который и выбран в качестве прототипа. В прототипе повышено быстродействие работы устройства при упрощении коммутации формирователя информационного сигнала.

Делитель частоты с переменным коэффициентом деления, содержащий элемент ИЛИ с n входами, последовательную триггерную структуру, входы синхронизации, разрешения счёта, установки в начальное состояние, разрешения деления, являющиеся соответствующими входами последовательной триггерной структуры, n логических трехвходовых элементов И, первые входы которых соединены с соответствующими разрядами шины управления, а выходы элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты.

Кроме того, устройство содержит вторую последовательную триггерную структуру, которая, как и первая, выполнена в виде n-разрядного двоичного счетчика c объединёнными входами разрешения счета, установки в начальное состояние и разрешения деления, являющимися соответствующими входами в счётчиках, выход переполнения устройства, являющийся соответствующим выходом первого счетчика, а вход синхронизации второго счётчика соединен с инверсным выходом тактовой частоты первого счетчика, у которого прямые разрядные выходы соединены соответственно со вторыми входами элементов И, третьи входы этих элементов И соединены с соответствующими инверсными разрядными выходами второго счетчика, а третьи входы этих элементов И соединены с разрядами шины управления в обратном порядке.

Прототип работает следующим образом.

На вход синхронизации счетчика поступает импульсный поток (тактовая последовательность) с частотой F0. На входы разрешения счета и деления поступают разрешающие сигналы. С помощью сигнала установки в начальное состояние счетчики сбрасываются: выходы  устанавливаются в ноль, а выходы

устанавливаются в ноль, а выходы  - в единицу.

- в единицу.

При появлении на входе синхронизации импульсов тактовой частоты F0 начинается одновременная работа счетчиков, причем их состояние отличается на пол такта. За эти пол такта выполняется выделение разряда, в котором происходит изменение состояния из нуля в единицу, и формируется единичный импульс. Этот импульс пропускается на выход сигналом разрешения, который при наличии единицы на соответствующем разряде шины, управляет прохождением импульсов на выход. Управление прохождением импульсов на выход осуществляется сигналами шины управления в обратном порядке.

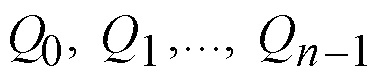

Логическое выражение для выхода Fyимеет вид:

,

,

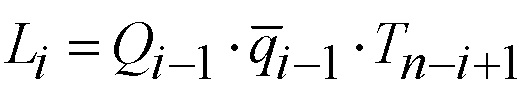

где функция L в общем случае  , a i – номер разряда шины управления (от 1 до n).

, a i – номер разряда шины управления (от 1 до n).

Очевидно, что для любого i равенство единице  достигается при одновременном равенстве единице

достигается при одновременном равенстве единице  , и

, и  . Такая ситуация возникает для каждого единичного состояния

. Такая ситуация возникает для каждого единичного состояния  в течение времени длительности импульса тактовой частоты τ только при начале этого единичного состояния. Это связано с тем, что переход состояния

в течение времени длительности импульса тактовой частоты τ только при начале этого единичного состояния. Это связано с тем, что переход состояния  из единицы в ноль сдвинут на время (относительно перехода

из единицы в ноль сдвинут на время (относительно перехода  из нуля в единицу), и обеспечено тактированием второго счетчика инверсным выходом синхронизации первого счетчика, то есть сигналом

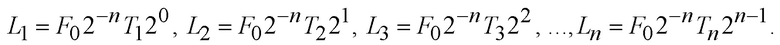

из нуля в единицу), и обеспечено тактированием второго счетчика инверсным выходом синхронизации первого счетчика, то есть сигналом  . На выходе любого логического элемента Li будет формироваться импульсная последовательность с частотой

. На выходе любого логического элемента Li будет формироваться импульсная последовательность с частотой

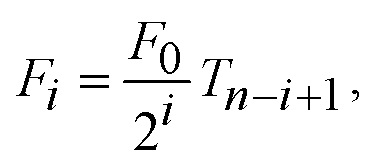

,

,

где  - логическое состояние i-x разрядов кодов управления N.

- логическое состояние i-x разрядов кодов управления N.

Импульсы в этих последовательностях разнесены по времени, поэтому на выходе логического элемента ИЛИ, являющегося выходом устройства в целом, происходит формирование суммарной частоты, среднее значение которой, как и у аналога, имеет вид

.

.

Недостатком прототипа является большое время преобразования, связанное с работой двух счетчиков, построенных на двухступенчатых триггерах со статическим управлением.

Задачей, на решение которой направлено заявляемое изобретение, является повышение быстродействия устройства за счет использования быстрых сдвигающих регистровых операций при взвешенном формировании выходного импульсного потока

Техническим результатом является высокое быстродействие работы устройства при его схемотехническом упрощении.

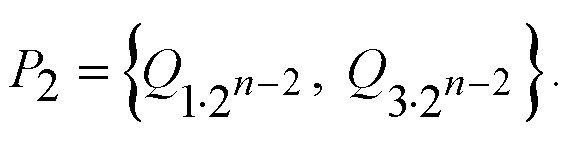

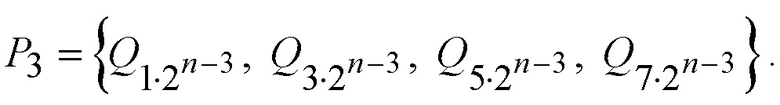

Поставленная задача решается тем, что в делитель частоты с переменным коэффициентом деления, содержащий элемент ИЛИ с n входами, последовательную триггерную структуру, входы синхронизации, установки в начальное состояние, разрешения деления, являющиеся соответствующими входами последовательной триггерной структуры, n логических трехвходовых элементов И, первые входы которых соединены с соответствующими разрядами шины управления, а выходы элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты, введены n–1 элементов ИЛИ на два, четыре, …, 2n–1 входов, элемент ИЛИ-НЕ на 2n–1 входов, а последовательная триггерная структура выполнена в виде сдвигового регистра на 2n–1 разрядов, информационный D-вход которого подключен к выходу элемента ИЛИ-НЕ, соединённому по входам с соответствующими выходами разрядов регистра, которые объединены также со входами элементов ИЛИ в следующем порядке: у двухвходового элемента ИЛИ1- выходы разрядов  регистра, у четырёхвходового элемента ИЛИ2 - выходы разрядов

регистра, у четырёхвходового элемента ИЛИ2 - выходы разрядов

регистра и так далее до

регистра и так далее до  -входового элемента ИЛИn-1- выходы разрядов

-входового элемента ИЛИn-1- выходы разрядов  соответственно регистра, причём выход

соответственно регистра, причём выход  регистра подсоединён к второму входу первого элемента И1, а на вторые входы остальных элементов И - второго И2, третьего И3 и так далее до n-го элемента Иn подключены выходы элементов ИЛИ соответственно первого ИЛИ1, второго ИЛИ2 и так далее до (n–1)-го элемента ИЛИn–1, при этом третьи входы элементов И объединены с входом синхронизации устройства.

регистра подсоединён к второму входу первого элемента И1, а на вторые входы остальных элементов И - второго И2, третьего И3 и так далее до n-го элемента Иn подключены выходы элементов ИЛИ соответственно первого ИЛИ1, второго ИЛИ2 и так далее до (n–1)-го элемента ИЛИn–1, при этом третьи входы элементов И объединены с входом синхронизации устройства.

Сущность предполагаемого изобретения состоит в создании делителя частоты с переменным коэффициентом деления путем организации циклического сдвигового режима прохождения импульса с весовым формированием частотных последовательностей, из которых в зависимости от управляющего кода формируется выходная импульсная последовательность.

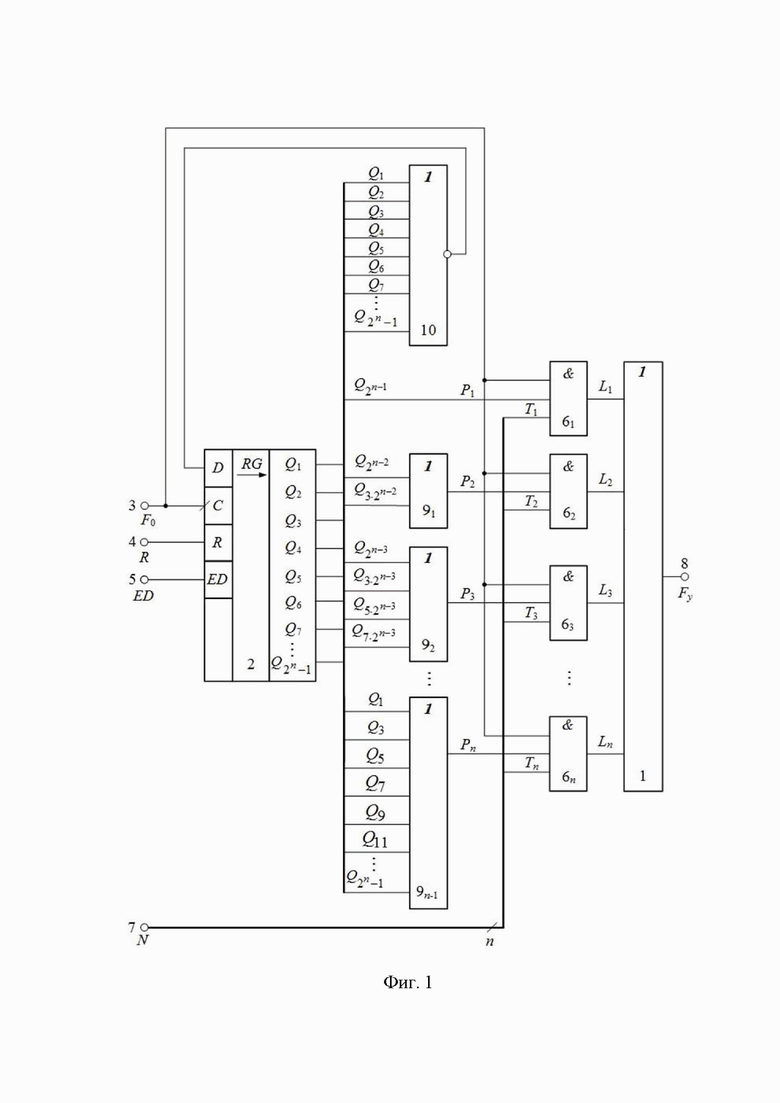

Сущность предлагаемого изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема предлагаемого делителя частоты, на фиг. 2 - временные диаграммы процессов, протекающих в устройстве для N=3 (011) и для N=7 (111).

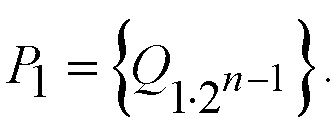

Делитель частоты с переменным коэффициентом деления, содержит элемент ИЛИ 1 с n входами, последовательную триггерную структуру 2, входы синхронизации 3, установки в начальное состояние 4, разрешения деления 5, являющиеся соответствующими входами последовательной триггерной структуры 2, n логических трехвходовых элементов И6, первые входы которых соединены с соответствующими разрядами шины управления 7, а выходы элементов И 6 подключены к соответствующим входам элемента ИЛИ 1, выход которого является информационным выходом 8 делителя частоты.

Кроме того, устройство содержит n–1 элементов ИЛИ 9 на два, четыре, …, 2n–1 входов, элемент ИЛИ-НЕ 10 на 2n–1 входов, а последовательная триггерная структура выполнена в виде сдвигового регистра 2 на 2n–1 разрядов, информационный D-вход которого подключен к выходу элемента ИЛИ-НЕ 10, соединённому по входам с соответствующими выходами разрядов регистра, которые объединены также со входами элементов ИЛИ 9 в следующем порядке: у двухвходового элемента ИЛИ 91 – выходы разрядов  регистра 2, у четырёхвходового элемента ИЛИ 92 – выходы разрядов

регистра 2, у четырёхвходового элемента ИЛИ 92 – выходы разрядов

регистра 2 и так далее до

регистра 2 и так далее до  -входового элемента ИЛИ 9n-1 – выходы разрядов

-входового элемента ИЛИ 9n-1 – выходы разрядов  регистра 2, причём выход

регистра 2, причём выход  регистра 2 подсоединён к второму входу первого элемента И61, а на вторые входы остальных элементов И 6– второго И 62, третьего И 63 и так далее до n-го элемента И6n подключены выходы элементов ИЛИ 9 соответственно первого ИЛИ 91, второго ИЛИ 92 и так далее до (n–1)-го элемента ИЛИ 9n–1, при этом третьи входы элементов И 6 объединены с входом синхронизации 3 устройства.

регистра 2 подсоединён к второму входу первого элемента И61, а на вторые входы остальных элементов И 6– второго И 62, третьего И 63 и так далее до n-го элемента И6n подключены выходы элементов ИЛИ 9 соответственно первого ИЛИ 91, второго ИЛИ 92 и так далее до (n–1)-го элемента ИЛИ 9n–1, при этом третьи входы элементов И 6 объединены с входом синхронизации 3 устройства.

Устройство работает следующим образом.

На вход синхронизации C3 устройства поступает импульсная (тактовая) последовательность с частотой F0. С помощью подачи сигнала на вход R4 устройства регистр 2 устанавливается в нулевое состояние. На вход ED5 устройства поступает разрешающий сигнал. После завершения сигналов на входах 4 (ось 1, фиг. 2) и входе 5 устройства, появление на входе 3 первого импульса тактовой частоты F0 обеспечивает появление «1» на выходах Q1 регистра 2 иP3 элемента ИЛИ 92(оси 2 – 3, фиг. 2). Импульс с выхода P3 подается на вход элемента И 63. В зависимости от значения соответствующего старшего разряда Tn кода шины управления N 7 этот импульс может появляться на выходе L3 и следом через элемент ИЛИ 1 на выходе Fy8 устройства.

Для примера:

при «1» в старшем третьем разряде N = 111в первом такте появляются импульсы (оси 2 – 3, L3, Fy, фиг 2);

при «0» в старшем третьем разряде N = 011 в первом такте импульсы отсутствуют (оси 2 – 3, L3, Fy, фиг 2).

На следующем такте произойдет сдвиг и единичный импульс сформируется на выходах Q2 регистра 2 и P2элемента ИЛИ 91 (оси 4 - 5, фиг 2). В зависимости от значения соответствующего разряда T2 кода шины управления N 7 этот импульс может появляться на выходе L2 и следом через элемент ИЛИ 1 на выходе Fy 8 устройства.

Для примера:

при «1» во втором разряде N = 111 во втором такте появляются импульсы (оси 4 – 5, L2, Fy, фиг 2);

при «1» во втором разряде N = 011 во втором такте импульсы появляются (оси 4–5, L2, Fy, фиг 2).

На третьем такте произойдет очередной сдвиг и единичный импульс сформируется на выходах Q3 регистра 2 иP3 элемента ИЛИ 92 (оси 6–7, фиг 2). В зависимости от значения соответствующего разряда T3 кода шины управления N 7 этот импульс может появляться на выходе L3 и следом через элемент ИЛИ 1 на выходе Fy 8 устройства.

Для примера:

при «1» в третьем разряде N = 111 в третьем такте появляются импульсы (оси 6–7, L3, Fy, фиг 2);

при «0» в третьем разряде N = 011 в третьем такте импульсы не появляются(оси 6–7, L3, Fy, фиг 2).

На четвертом такте вновь произойдет сдвиг и единичный импульс сформируется на выходе Q4 регистра 2 и в виде P1 подается непосредственно на вход элемента И 61 (оси 8 – 9, L1, Fy, фиг 2). В зависимости от значения соответствующего разряда T1 кода шины управления N 7 этот импульс может появляться на выходе L1 и следом через элемент ИЛИ 1 на выходе Fy 8 устройства.

Для примера:

при «1» в первом младшем разряде N = 111 в четвертом такте появляются импульсы (оси 8–9, L1, Fy, фиг 2);

при «0» в первом младшем разряде N = 011 в четвертом такте импульсы вновь появляются(оси 8–9, L1, Fy, фиг 2).

На пятом такте произойдет очередной сдвиг, и единичный импульс сформируется на выходах Q5 регистра 2 и P3 элемента ИЛИ 92 (оси 10 - 11, L3, Fy, фиг 2). В зависимости от значения соответствующего разряда T3 кода шины управления N 7 этот импульс может появляться на выходе L3 и следом через элемент ИЛИ 1 на выходе Fy 8 устройства.

Для примера:

при «1» в третьем разряде N = 111 в пятом такте появляются импульсы (оси 10 – 11, L3, Fy, фиг 2);

при «0» в третьем разряде N = 011 в пятом такте импульсы не появляются (оси 10 - 11, L3, Fy, фиг 2).

На шестом такте снова произойдет сдвиг и единичный импульс сформируется на выходах Q6 регистра 2 и P2элемента ИЛИ 92 (оси 12-13, L2, Fy, фиг. 2). В зависимости от значения соответствующего разряда T2 кода шины управления N 7 этот импульс может появляться на выходе L2 и следом через элемент ИЛИ 1 на выходе Fy 8 устройства.

Для примера:

при «1» во втором разряде N = 111 в шестом такте появляются импульсы (оси 12– 13, L2, Fy, фиг. 2);

при «1» во втором разряде N = 011 в шестом такте импульсы снова появляются (оси 12– 13, L2, Fy, фиг. 2).

На седьмом такте произойдет сдвиг и единичный импульс сформируется на выходах Q7 регистра 2 и P3 элемента ИЛИ 92 (оси 14 –15, L3, Fy, фиг. 2). В зависимости от значения соответствующего разряда T2 кода шины управления N 7 этот импульс может появляться на выходе L2 и следом через элемент ИЛИ 1 на выходе Fy 8 устройства.

Для примера:

при «1» в третьем разряде N = 111 в седьмом такте появляются импульсы (оси 14–15, L3, Fy, фиг. 2);

при «0» в третьем разряде N = 011 в седьмом такте импульсы не появляются (оси 14–15, L3, Fy, фиг. 2).

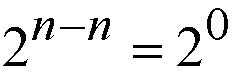

На следующем такте снова происходит сдвиг единичного импульса и формирование на выходе 8 частотного сигнала Fy аналогично описанным выше процессам до  . Далее с помощью элемента ИЛИ-НЕ 10 фиксируется завершение процесса сдвига по всем разрядам и формируется сигнал «1», поступающий на информационный вход D регистра 2 для организации нового цикла, то есть процесс повторяется.

. Далее с помощью элемента ИЛИ-НЕ 10 фиксируется завершение процесса сдвига по всем разрядам и формируется сигнал «1», поступающий на информационный вход D регистра 2 для организации нового цикла, то есть процесс повторяется.

Для примера, описанной выше, трехразрядной структуры:

n = 3;

На восьмом такте формируется импульс с помощью элемента ИЛИ-НЕ 10 и регистра 2, а на выходе регистра 2 импульсы не появляются (оси 16– 17, ИЛИ-НЕ, фиг. 2).

Новый цикл работы устройства начинается со следующего тактового импульса, по которому «1» появляется на выходе Q1 регистра 2 (оси 18-19, фиг. 2). Далее весь процесс повторяется циклически.

В результате формируются единичные импульсы, которые взвешенно распределяются по входам элементов ИЛИ 9. Таким образом формируются опорные частоты, поступающие на вторые входы элементов И 6 с выходов элементов ИЛИ 9 и выхода  регистра, подсоединенного непосредственно ко второму входу первого элемента И 61. На первые входы элементов И 6 поступают сигналы с соответствующих разрядов шины управления N 7. На третьи входы элементов И 6 поступают сигналы синхронизации со входа F0. На выходах элементов И 6 создаются опорные импульсные последовательности, которые в зависимости от значения разряда шины управления N 7 поступают на вход элемента ИЛИ 1. В результате, на выходе элемента ИЛИ 1 формируется выходной частотный информационный сигнал Fy.

регистра, подсоединенного непосредственно ко второму входу первого элемента И 61. На первые входы элементов И 6 поступают сигналы с соответствующих разрядов шины управления N 7. На третьи входы элементов И 6 поступают сигналы синхронизации со входа F0. На выходах элементов И 6 создаются опорные импульсные последовательности, которые в зависимости от значения разряда шины управления N 7 поступают на вход элемента ИЛИ 1. В результате, на выходе элемента ИЛИ 1 формируется выходной частотный информационный сигнал Fy.

В основу работы делителя частоты с переменным коэффициентом деления положен принцип взвешенного одноступенчатого распределения импульсов с выходов сдвигового регистра по опорным частотным последовательностям и автоматическим запуском циклической работы с разрешением прохождения сигналов на выход устройства при наличии единицы на соответствующем разряде шины управления.

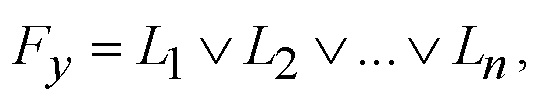

Логическое выражение для выхода устройства 8 имеет следующий вид:

Функция Lв общем случае для каждого i-го входа элемента ИЛИ 1 формируется на соответствующих элементах И 6:

Li = Ti⋅Pi⋅F0,

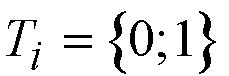

где  –логическое состояние i-го разряда кода управления;

–логическое состояние i-го разряда кода управления;

- взвешенно распределенный выход i-го множества разрядов Q регистра 2;

- взвешенно распределенный выход i-го множества разрядов Q регистра 2;

– логическое состояние тактового импульса.

– логическое состояние тактового импульса.

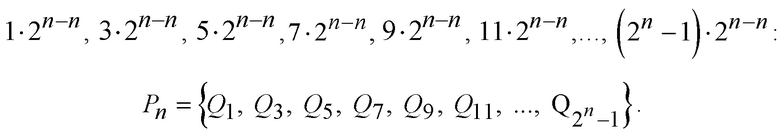

Первое множество  включает в себя один элемент Qс основанием

включает в себя один элемент Qс основанием  и номером

и номером  :

:

Второе множество  формируется из двух элементов Qс основанием

формируется из двух элементов Qс основанием  и номерами

и номерами  и

и  :

:

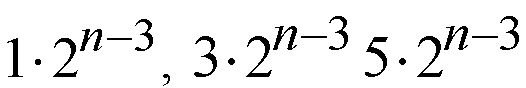

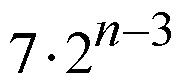

Третье множество  образуется из четырех элементов Qс основанием

образуется из четырех элементов Qс основанием  и номерами

и номерами  и

и  :

:

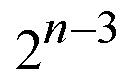

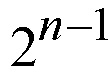

В следующем множестве число элементов Q удваивается, показатель степени основания уменьшается еще на единицу и номера назначаются также с соответствующим умножением чисел нечетного ряда.

Последнее множество  содержит

содержит  элементов Qс основанием

элементов Qс основанием  равным единице и номерами нечетного ряда до

равным единице и номерами нечетного ряда до

В результате в последовательностях L1, L2,…,Ln формируются импульсы, которые разнесены по времени, поэтому на выходе логического элемента ИЛИ 1 происходит формирование суммарной частоты с циклическим  повторением.

повторением.

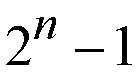

Значения частот на выходах L1, L2,L3,…,Ln описываются выражениями:

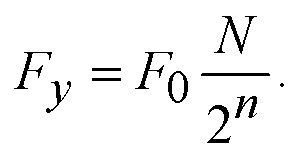

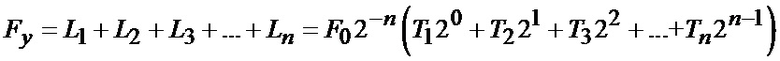

Суммарное значение выходной частоты устройства  определяется следующим образом:

определяется следующим образом:

.

.

В этом выражении сумма произведений значения текущего бита кода Tiна вес бита n-разрядной шины управления 7 представляет собой двоичный код N.

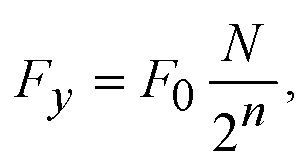

Таким образом, средняя частота Fy импульсного потока на выходе 8 устройства может быть записана следующим образом:

то есть, передаточная функция, заявляемого делителя частоты с переменным коэффициентом деления, соответствует передаточной функции прототипа.

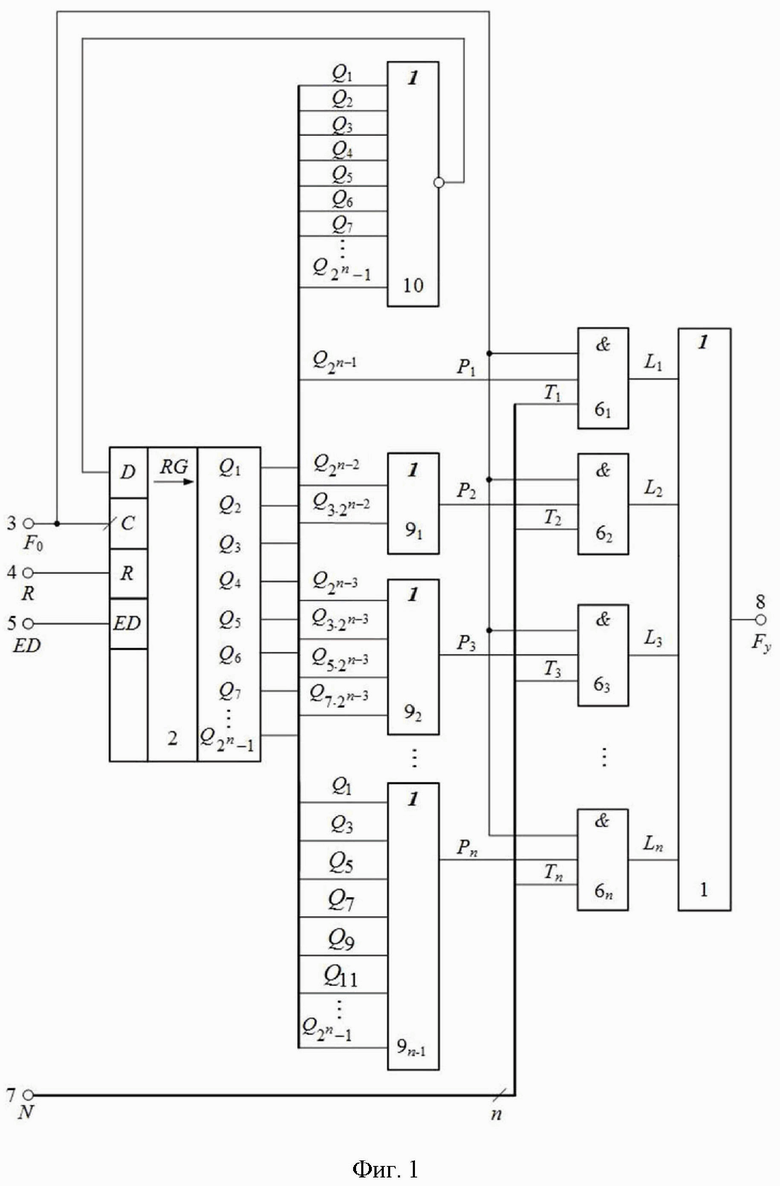

Быстродействие делителя частоты определяется временем срабатывания λ:

где  - время срабатывания сдвигового регистра;

- время срабатывания сдвигового регистра;

- время срабатывания логического элемента с функцией ИЛИ;

- время срабатывания логического элемента с функцией ИЛИ;

- время срабатывания логического элемента с функцией И;

- время срабатывания логического элемента с функцией И;

- время срабатывания логического элемента с функцией ИЛИ.

- время срабатывания логического элемента с функцией ИЛИ.

Времена  срабатывания логических элементов в первом приближении можно считать одинаковыми и равными

срабатывания логических элементов в первом приближении можно считать одинаковыми и равными

Время срабатывания сдвигового регистра  обычно не превышает

обычно не превышает

Таким образом, время срабатывания для заявляемого делителя частоты:

У прототипа задержка при изменении значения частоты  определяется выражением:

определяется выражением:

где  - время срабатывания счетчика;

- время срабатывания счетчика;

- время срабатывания логического элемента с функцией И;

- время срабатывания логического элемента с функцией И;

- время срабатывания логического элемента с функцией ИЛИ.

- время срабатывания логического элемента с функцией ИЛИ.

Время срабатывания счетчика  обычно не превышает

обычно не превышает

Таким образом, время срабатывания для прототипа составляет:

Следовательно, задержка λ при изменении значения частоты в заявляемом устройстве в первом приближении меньше в 2 раза, чем задержка  прототипа. То есть, быстродействие работы заявляемого устройства по сравнению с прототипом увеличено.

прототипа. То есть, быстродействие работы заявляемого устройства по сравнению с прототипом увеличено.

Кроме того, обеспечено схемотехническое упрощение устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 2020 |

|

RU2752485C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1990 |

|

RU2015539C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| Преобразователь отношения двух частот в код | 1976 |

|

SU660231A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| СПОСОБ ФОРМИРОВАНИЯ ПОСТОЯННЫХ РАЗМЕРОВ ИНФОРМАЦИОННОГО ПОЛЯ ЛАЗЕРНОЙ СИСТЕМЫ ТЕЛЕОРИЕНТАЦИИ В ПЛОСКОСТИ УПРАВЛЯЕМОГО ОБЪЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2093849C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Изобретение относится к автоматике и вычислительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, в измерительных и вычислительных устройствах, устройствах обработки аудио- и видеосигналов, а также при первичной обработке сигналов фазированных антенных решеток радаров. Техническим результатом является повышение быстродействия работы устройства при его схемотехническом упрощении. Устройство содержит элемент ИЛИ с n входами, сдвиговый регистр на 2n–1 разрядов, входы синхронизации, установки в начальное состояние, разрешения деления, являющиеся соответствующими входами регистра, n логических трехвходовых элементов И, n–1 элементов ИЛИ на два, четыре, …, 2n–1 входов, элемент ИЛИ-НЕ на 2n–1 входов. 2 ил.

Делитель частоты с переменным коэффициентом деления, содержащий элемент ИЛИ с n входами, последовательную триггерную структуру, входы синхронизации, установки в начальное состояние, разрешения деления, являющиеся соответствующими входами последовательной триггерной структуры, n логических трехвходовых элементов И, первые входы которых соединены с соответствующими разрядами шины управления, а выходы элементов И подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом делителя частоты, отличающийся тем, что в устройство введены n–1 элементов ИЛИ на два, четыре, …, 2n–1 входов, элемент ИЛИ-НЕ на 2n–1 входов, а последовательная триггерная структура выполнена в виде сдвигового регистра на 2n–1 разрядов, информационный D-вход которого подключен к выходу элемента ИЛИ-НЕ, соединённому по входам с соответствующими выходами разрядов регистра, которые объединены также со входами элементов ИЛИ в порядке: у двухвходового элемента ИЛИ1 – выходы разрядов

регистра, у четырёхвходового элемента ИЛИ2 – выходы разрядов

регистра, у четырёхвходового элемента ИЛИ2 – выходы разрядов  ,

,  ,

,

регистра и так далее до

регистра и так далее до  -входового элемента ИЛИn-1 – выходы разрядов Q1, Q3, Q5, Q7, Q9, Q11, …,

-входового элемента ИЛИn-1 – выходы разрядов Q1, Q3, Q5, Q7, Q9, Q11, …,  соответственно регистра, причём выход

соответственно регистра, причём выход  регистра подсоединён к второму входу первого элемента И1, а на вторые входы остальных элементов И – второго И2, третьего И3 и так далее до n-го элемента Иn подключены выходы элементов ИЛИ соответственно первого ИЛИ1, второго ИЛИ2 и так далее до (n–1)-го элемента ИЛИn–1, при этом третьи входы элементов И объединены с входом синхронизации устройства.

регистра подсоединён к второму входу первого элемента И1, а на вторые входы остальных элементов И – второго И2, третьего И3 и так далее до n-го элемента Иn подключены выходы элементов ИЛИ соответственно первого ИЛИ1, второго ИЛИ2 и так далее до (n–1)-го элемента ИЛИn–1, при этом третьи входы элементов И объединены с входом синхронизации устройства.

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2004 |

|

RU2273043C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1990 |

|

RU2015539C1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1986 |

|

SU1319275A1 |

| Делитель частоты с переменным коэффициентом деления | 1980 |

|

SU1075413A1 |

| Система автоматического регулирования прочности торфяных брикетов на прессе с охладительными лотками | 1982 |

|

SU1062021A1 |

| JP 2006196973 A, 27.07.2006. | |||

Авторы

Даты

2021-12-21—Публикация

2021-05-13—Подача