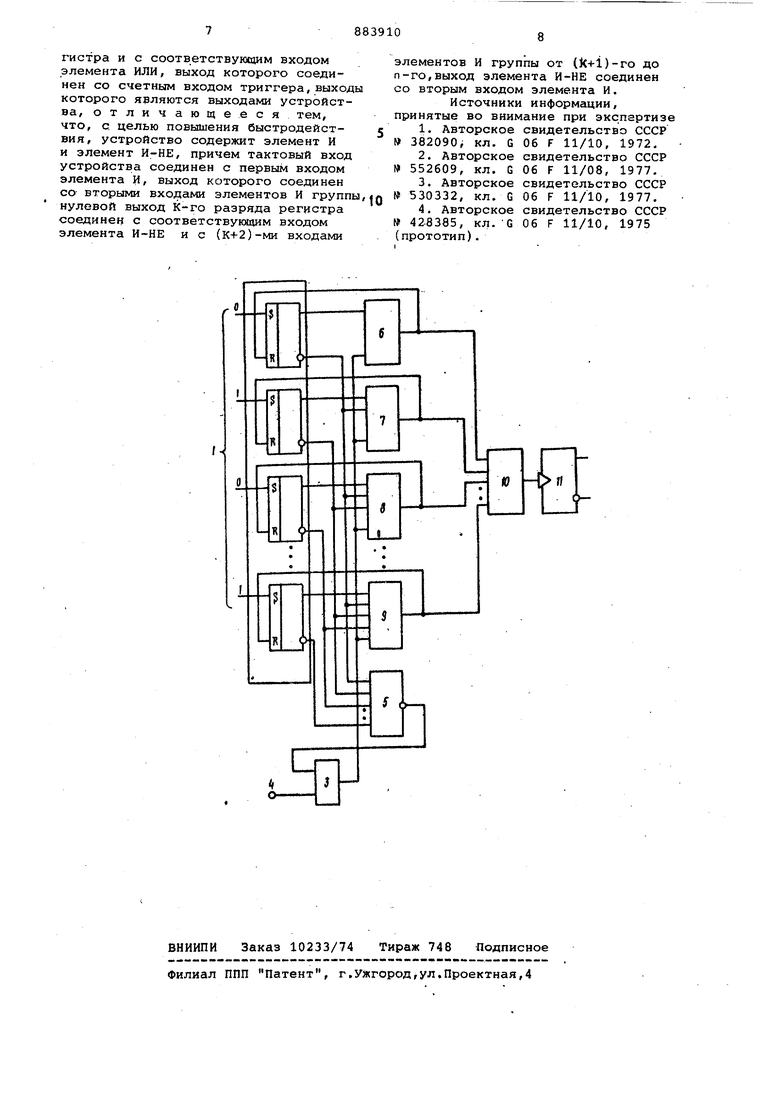

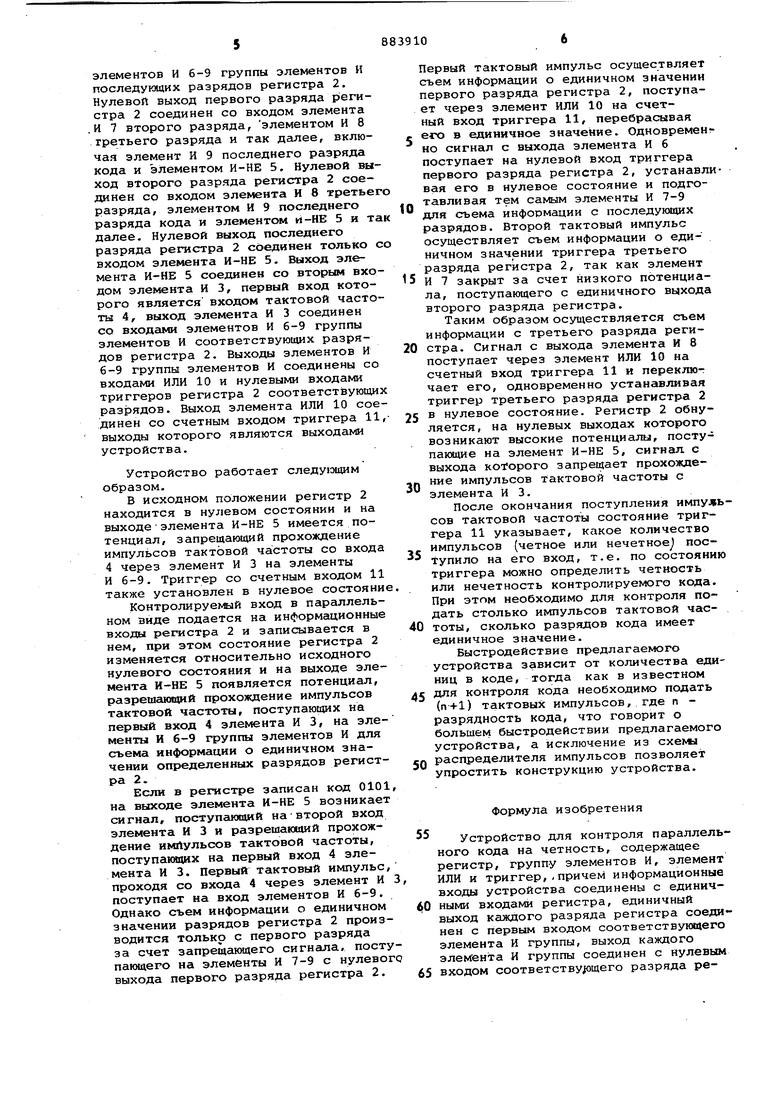

Недостатком известных устройств является их сложность. Известно также устройство для контроля параллельного двоичного кода на четность, содержащее два элемента И, регистры сдвига, причем информационными входами устройства :являются параллельные входы регистра сдвига, нулевые разрядные выходы кот рого соединены с входами первого эле мента И, выход которого соединен с первым входом второго элемента И, вт рой вход второго элемента И соединен с шиной тактовой частоты, а его выход - с входом сдвига регистра сдвига, выход KOTQporo соединен со счетным входом триггера, выход триггера является выходом устройства 3. Недостатком устройства является низкое быстродействие, обусловленное учетом положения единицы старшего разряда кода. Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому изобретению является устройство, для конт роля двоичного кода на четность, содержащее элемент И, первые входы которых соединены с выходами соответ ствующих контролируемых разрядов, элемент ИЛИ, входы которой подключе к Выходам элементов И, распределител импульсов и фиксирующий триггер, счетный вход которого соединен с вы ходом элемента ИЛИ, а его нулевой вход подключен к первому выходу рас пределителя импульсов, другие выходы которого соединены со вторыми вход1 ми соо1«ветствующих элементов И 4. Недостатком известного устройств является его сложность и низкое быс тродействие, обусловленное необходи мостью опроса всех разрядов, в том числе и тех, которые находятся в ну левом состоянии, а также необходимость специального обнуления соответствугощих разрядов после окончани процесса контроля кода на четностьi вследствие чего замедляется готовность к контролю следующей кодовой комбинации. Цель изобретения - повышение быстродействия устройства для контроля параллельного кода на четность Поставленная цель .достигается тем, что в устройство, содержащее регистр, группу элементов И, элемент ИЛИ, триггер, причем информационные эходы устройства соединены с единичными входами регистра, единичный выход каждого разряда регистра соединен с первым входом соответствующего элемента И группы, выход каждого элемента И группы соединен с нуле вым входом соответствующего разряда регистра и с соответствующим входом элемента ИЛИ, выход которого соединен со счетным входом триггера, выхо ды которого являются выходами устройства, в него введены элемент И и элемент И-НЕ, причем тактовый вход устройства соединен с первым входом элемента И, выход которого соединен со вторыми входс1ми элементов И группы, нулевой выход К-го разряда ре- гистра соединен с соответствующим входом элемента И-НЕ и с (К+2)-ми входами элементов И группы от (К+1)годо п-го, выход элемента И-НЕ соединен со вторым входом элемента И. Сущность изобретения состоит в упрощении устройства, что достигается исключением распределителя импульсов, съем информации осуществляется во время прихода импульсов тактовой частоты на первый вход элемента И. Кроме того, повышается быстродействие устройства за счет съема и подсчет информации о состоянии тех разрядов регистра, которые имеют единичное значение. Элементы И соответствующих разря- дов регистра предназначены для съема информации тех разрядов регистра, которые имеют единичные значения по приходу импульсов тактовой частоты с выхода вновь введенного элемента И, при этом за счет соединения нулевых выходов триггеров каждого предыдущего разряда регистра с входами элементов И группы последующих разрядов съем информации производится в порядке возрастания разрядов регистра, начиная с младшего. После снятия информации соответствующий разряд регистраобнуляется и осуществляется подготовка следующего элемента И группы для снятия информации со следующего более старшего разряда регистра. Элемент И-НЕ предназначен, для формирования разрешающего сигнала на вход элемента И, который обеспечивает прохождение импульсов тактовой частоты на входы всех элементов И группы. При обнулении регистра выдается сигнал о запрещении прохождения импульсов тактовой частоты и готовности регистра к принятию для контроля следующего кода. Элемент ИЛИ предназначен для приема информации о единичных значениях разрядов и их подсчета на триггере со счетным входом. На чертеже изо15рг1жена функциональная схема предлагаемого устройства контроля. Устройство содержит входы 1 кода, регистр 2, элемент ИЗ, тактовый вход 4, элемент И-НЕ 5, группу элементов И 6-9, элемент ИЛИ 10 и триггер 11 со счетным входом. Регистр 2 предназначен для хранения контролируемого кода, поступающего на входы 1. Единичные выходы ка)вдого разряда регистра 2 соединены, с первьши входами соответствукидих

элементов И 6-9 группы элементов И последующих разрядов регистра 2. Нулевой выход первого разряда р егистра 2 соединен со входом элемента .И 7 второго разряда, элементом И 8 третьего разряда и так далее, включая элемент И 9 последнего разряда кода и элементом И-НБ 5, Нулевой выход второго разряда регистра 2 соединен со входом элемента И 8 третьег разряда, элементом И 9 последнего разряда кода и элементом и-НЕ 5 и та далее. Нулевой выход последнего разряда регистра 2 соединен только с входом элемента И-НЕ 5. Выход элемента И-НЕ 5 соединен со вторым входом элемента ИЗ, первый вход которого является входом тактовой частоты 4, выход элемента И 3 соединен со входами элементов И 6-9 группы элементов И соответствующих разрядов регистра 2. Выходы элементов И 6-9 группы элементов И соединены со входами ИЛИ 10 и нулевыми входами триггеров регистра 2 соответствующих разрядов. Выход элемента ИЛИ 10 соединен со счетным входом триггера 11выходы которого являются выходами устройства.

Устройство работает следу1эщим образом.

В исходном положении регистр 2 находится в нулевом состоянии и на выходе элемента И-НЕ 5 имеется потенциал, запрещающий прохождение импульсов тактовой частоты со входа 4 через элемент И 3 на элементы И 6-9. Триггер со счетным входом 11 также установлен в нулевое состояние

Контролируемой вход в параллельном виде подается на информещионные входы регистра 2 и записывается в нем, при этом состояние регистра 2 изменяется относительно исходного нулевого состояния и на выходе элемента И-НЕ 5 появляется потенциал, разрешгиощкй прохождение импульсов тактовой частоты, поступающих на первый вход 4 элемента И 3, на элементы И 6-9 группы элементов И для съема информации о единичном значении определенных разрядов регистра 2.

Если в регистре записан код 0101 на выходе элемента И-НЕ 5 возникает сигнал, поступающий на второй вход элемента И 3 и разрешающий прохождение им1 ульсов тактовой частоты, поступаиицих на первый вход 4 элемента И 3. Первый тактовый импульс, проходя со входа 4 через элемент И поступает на вход элементов И 6-9. Однако съем информации о единичном значении разрядов регистра 2 производится только с первого разряда за счет запрещающего сигнала, поступающего на элементы И 7-9 с нулевог выхода первого разряда регистра 2.

Первый тактовый импульс осуществляет съем информации о единичном значении первого разряда регистра 2, поступает через элемент ИЛИ 10 на счетный вход триггера 11, перебрасывая его в единичное значение. Одновременг но сигнал с выхода элемента И 6 поступает на нулевой вход триггера первого разряда регистра 2, устанавливая его в нулевое состояние и подготавливая тем самым элементы И 7-9

0 для съема информации с последукяцих разрядов. Второй тактовый импульс осуществляет съем информации о единичном значении триггера третьего разряда регистра 2, так как элемент

5 И 7 закрыт за счет низкого потенциала, поступающего с единичного выхода второго разряда регистра.

Таким образом осуществляется съем информации с третьего разряда реги0стра. Сигнал с выхода элемента И 8 поступает через элемент ИЛИ 10 на счетный вход триггера 11 и переключает его, одновременно устанавливая триггер третьего разряда регистра 2 в нулевое состояние. Регистр 2 обну5ляется, на нулевых выходах которого возникают высокие потенциалы, поступакицие на элемент И-НЕ 5, сигнал, с выхода которого запрещает прохождение импульсов Тактовой частоты с

0 элемента ИЗ.

После окончания поступления импульсов тактовой частоты состояние триггера 11 указывает, какое количество импульсов (четное или нечетное пос5тупило на его вход, т.е. по состоянию триггера можно определить четность или нечетность контролируемого кода. При этом необходимо для контроля подать столько импульсов тактовой час0тоты, сколько разрядов кода имеет единичное значение.

Быстродействие предлагаемого устройства зависит от количества единиц в коде, тогда как в известном для контроля кода необходимо подать

5 (п-+1) тактовых импульсов, где п разрядность кода, что говорит о большем быстродействии предлагаемого устройства, а исключение из схемл распределителя импульсов позволяет

0 упростить конструкцию устройства.

Формула изобретения

55

Устройство для контроля параллельного кода на четность, содержащее регистр, группу элементов И, элемент ИЛИ и триггер,- причем информационные входы устройства соединены с единичными входами регистра, единичный

выход каждого разряда регистра соединен с первым входом соответствующего элемента И группы, выход каждого элемента И группы соединен с нулевым

65 входом cooTBeTCTsyjomero разряда регистра и с соответствующим входом элемента ИЛИ, выход которого соедикотопо., триггера, выхо которого являются выходами устройст ва, о т л и ч а ю щ е е с я тем что, с целью повьмения быстродействия УСТРОЙСТВО содержит элемент И vcTnor Р тактовый вход «Рвым входом элемента и, выход которого соединен со вторыми входами элементов И групп нулевой выход к-го разряда регистра соединен с соответствующим входом элемента И-НЕ и с (к+2)-ми входами 10 элементов И группы от (К+1)-го до п-го,выход элемента И-НЕ соединен со вторым входом элемента И. Источники информации, принятые во внимание при экспертизе U свидетельство СССР 382090, кл. G Об F 11/10. 1972. м свидетельство СССР 552609, кл. G 06 F 11/08, 1977. I t;o;-, свидетельство СССР № 530332, кл. G 06 F 11/10, 1977 свидетельство СССР № 42.8385, кл. С Об F 11/10, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичного кода на нечетность | 1981 |

|

SU1012261A1 |

| Устройство для контроля параллельного кода на четность | 1981 |

|

SU1015387A2 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля параллельного кода на четность | 1983 |

|

SU1100626A1 |

| Устройство для определения четности информации | 1978 |

|

SU767766A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1980 |

|

SU871166A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU962955A1 |

Ы

ю

Авторы

Даты

1981-11-23—Публикация

1979-10-17—Подача