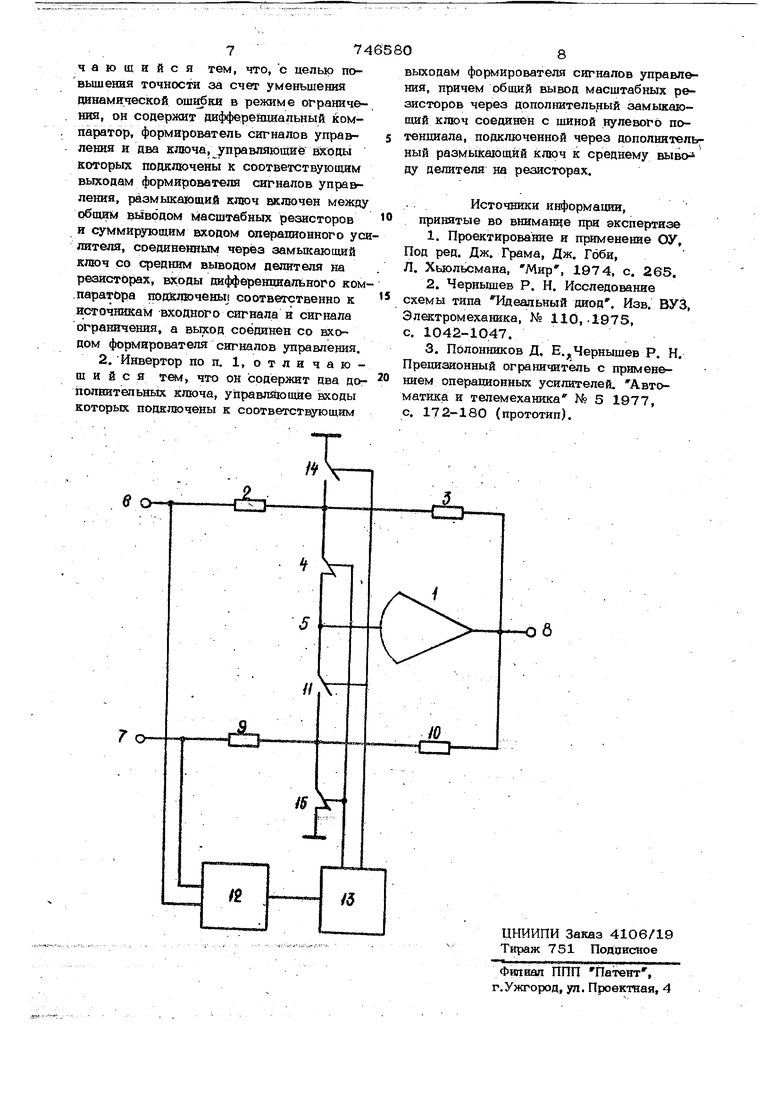

Изобретение относится к автоматике и вычислительной технике. Известны кшерторы с управляемым ограничением выходного сигнала, в состав которых входят основной операпионный усилитель и два вспомогательных уси лителя для реализации ограничения (один в положительной полуплоскости выходного диапазона, второй-в отрицательной). В структуре первого типа выход вспомогательного неинвертЕсрующего усилителя связан с суммирующей точкой основного операционного усилителя (ОУ). На вход вспомогательного усилителя подается разность выходного напряжения основног о усилителя и напряжения ограшшения. Пра превышении величины выходного сит нала уровня ограничения вспомЬгате;и.ный усилитель обеспечивает дополнительный тек к суммирующей точке основного ОУ такой величины, чтобы скомпенсиро вать изменение входного тока через входной резистор,которое обусловленоизменением напряжения входного сигнала. i Вспомогательный усилитель стремится обеспечить постоянную веяячйну разности входного тока н тока компенсации, вследствие чего тоК в цепи обратной связи остается неизменньш, и неизменным остается выходное напряжение ij. Б структуре второго , также состоящей из основного усилятеля, двух вспомогательных ин ртярующих ОУ и, кроме того, модуля для выделения минимума , поступающего с выходов ocHotrного и вспомогательного ОУ, при превыш&аш величины выходнсго напряжения уровня ограничения основной ОУ с помощью модуля выделения минимума отключается от цепи обратной связи, а О1ШН из вспомогательных усилителей (в зависимости от знака уровня ограничения) переводится в режим инвертора, на вход которого подключено напряжение ограничения, а выход инвертора соединен с выходом устройства 2. Недостатком известных структур являетсн значительная динамическая ошибЩ, возникающая при переходе схемы иэ линейного режима (режим инвертора)в режим ограничения, а 1акже принщпшапь ;йёй нёв6зМОжносгЬ бсущестшть нШрёрывную установку уровня ограшчения в положительной и отрицательной пбпуяпос.костях выходного диапазона. Наиболее близким техническим рёше шШк прШШГйёмШу Я1впя«тся инвёргтор с управляемым ограничешем выходного сигнала, содержащий операционный у С а:1штель, выход которого является вы ходом инвертора и соединен через два - пбе ейоватейьно включенных масштабных резистора с источником входного сигнала и через делитель на резисторах - с источником сигнала ограничения З. Недостатком этого инвертора с управгляёмым ограничением выходного сигнала является сравнительно большая динамическая ошибка при переходе из линейного режима в режим ограничения, невозможность непрерывной регулировки уровня ограничения в обеих пблуйлоскостях выхо диапазона. При переходе из линейного режима в режим ограниче шя требуется некоторое время для изменения напряжения на выходе вспомогательного усилителя с уровгвя огранйчёйия вспомот-ательного огранитщ ёля выходе основного усилителя. Только по прошествии, этого времени начинается переключе ние аналогового 1ерекпюча тёпя,до этого продолжается рост напряжения на выходе : устройства. Это приводит к появлению Ш ряжёШЯперерегулирования на выходе Ограничителя. Величина a-foro напряже1йиярастет с ростом скорости изменения нходного сигнала. Наличие этого напряжёния и приводит к пЬявлению дополнительной динамической погрешности.. Ilerib изобретения - йовьТОёшё точности за счёт уменьшения динамической ошибки в режиме ограничения. Поётавпенная целидсхзтигаёгся тем, что инвертор.с управляемым ограничением выходного сигнала содержит дифференциальный компаратор, формйрОваТель сигналов управления и-два ключа, управляющие входы которых подключены к сООт1ветствующим выходам формироват ля сигналов управления, размьпсающий ключ включен между общим вйвОдом ма штабных резисторов и суммирующим вхо дом ойераШОНногб усйш йЖ; соЖ|:шшнным через замыкающий ключ со средним .-s в 1водом делителя на резист6 х, 1вхрды ифференциального компаратора подклюены соотвё ствбйНО к источникам вход- : ого сигнала и сигнала ограничения, а ыход соединен со входом формирователя 11гналов управления. Кррмб того, инверор содержит Два дополнительных ключа, правляющие входы которьпс подключены соответствующим выходам формироваеля сигналов управления, причем общий вывод масштабных резисторов через дополнительный замыкающий кЬюч соединен с шиной нулевого потенциала, подключенной через дополнительный размыкающий кШУч к среднему выводу делителя на резисторах. На чертеже изображена структурная схема предлагаемого инвертора с управляемым ограничением выхбдного сигнала. Уст хОйсТВо состоит из операциовнот о усилителя (ОУ) 1, масштабных резисторов 2, 3, размыкающето ключа 4, который соединяет общий вывод масштабных резисторов с суммирующим входом 5 ОУ. В точку 6 подключен источник входного сигнала, а в точку 7 - иЪточник сигнала ограничения. Между точкой 7 и вькодом 8 устройства включен делитель на резисторах 9 и 10. Общая точка этих резисторов через замыкающий . ключ 11 связана с суммирующим входом 5 ОУ. К точкам 6 и 7 подключены входы дифференциального компаратора 12, выход которого соединен с формирователем 13 сигналов уп равления. Формирователь 13 имеет парафазный выход. К первому выходу подключен управляющий вход ключа 4, ко второму - управляющий вход ключа 11.Инвертор работает следующим обраКогда величина входного сигнала по абсолютной Ъёпнчине меньше, чем напряжение ограничения, ключ 4 замкнут, а ключ 11 раз(мкнут. Тогда устройство представляет инвертор (в случае, если сопротивления резисторов 2 и 3 равны). При превышении величиной входного сигнала урОвНя ограничения компаратор 12 йёреключаётся в результате чего ключ 4 размыкается, а ключ 11 замыкается. Поэтому масштабные резисторы отключаются от суммирующего входа 5 ОУ. Уст ройство п ёр ёХОдит в режим ограничения, где операционный усилитель 1 включен в рёжнй ййвёртЪра со входным сигналом, равным напряжению огра{шчения. При уменьшении -абсолютной величины входного сигнала, когда она сравня.ется с величиной сигнала ограничения (с точностью до величины петли гистерезиса компаратора) компаратор переключается, изменяются сигналы управления на вьпсодах формирователя, в резуль йЛйч 4 замыкается, а ключ 11 раз мыкается. Устройство переходит в режим инвертора. Чтобы исключить натекание тока чере разомкнутый ключ 11 (в линейном режиме) или через разомкнутый ключ 4 (в режиме ограничения) и тем самым исключить дойолнительные источники оши бок в линейном режиме и ренойме ограничения, в устройство введено два дополнительных ключа: замыкающий 14 и размыкающий 15. Ключ 15 соединяет средний вывод резисторов 9 и 10 с шиной нулевого потенциала. Ключ 15 управляется синхронно с ключом 4 от первого выхода формирователя сигнала управления. Ключ 14 соединяет общий вывод ре зисторов 2 и .3 с шиной нулевого потенциала. Необходимым условием tins, работы ин вертора с управляемым ограничением выходного сигнала является равенство коэф фициентов передачи по входу инвертора и по входу напряжения ограничения. При срабатывании компаратора, когда величина входного сигнала превышает уровень напряжения ограничения, происходит переключение ключей и схема переходит в режим ограничения. Так как при этом входной сигнал отключен от суммирующей точки ОУ, то рассматриваемая схема обеспечивает практически 1Я деальнбе ограничение. Поскольку при переходе иэлинейного режима в режим ограничения на выходе ОУ с точностью до разброса в коэффициентах передачи по иньертирующему входу и входу ограничения не изменяется, -.в предлагаемой структуре отсутствует источник динамической ошибки, который имеет место у известного устройства. Динамическая ошибка, возникающая при переключении ключей, значительно меньше, чем динамическая ошибка ранее известных структур. Так как срабатывание компаратора и . следовательно, переключение ключей определяется только разностью напряжений входного сигнала и сигнала ограничения, ограничение обеспечивается в обеих полуплоскостях выходного диапазона. В устрой стве отсутствуют вспомогательные ограничители j,4TO сокращает общее число элементов. В результате введения дополнительных ключей величина напряжения на разомкнутом ключе 4 или 11 снижается до величины падения напряжения на замкнутом ключе 14 или 15 тем значительно снижается ошибка, вызванная неиде альностью ключей. Предлагаемая структура обладает многофункциональностью. При фиксированном составе оборудования, только изменяя коммутацию входных соединений устройства, оказывается возможным реализовать такие функциональные свойства, как идеальный диод, электронный коммутатор, уп равляемый умножитель на постоянный коэффициент. Режим идеального диоаа можно расскгатривать как частный случай ограничителя с нулевым уровнем ограничения, т.е. точка 7 заземлена. Такая схема при прочих равных условиях обладает более высокой динамйчесжой точностью, так как в ней отсутствует сшшбка обусловленная конечной скоростью изменения выходного напряжения ОУ, которая имеет место в классической схеме идеального диода известного устройства. В режиме электронного коммутатора один вход компаратора соединен с шиной нулевого потешшала, а на второй подает ся сигнал управления. На вход 6 подается напряжение первого канала, на вход 7второго. Переключение каналов происходит при изменении полярности сигнала на входе компаратора. В режиме управ}юеиого умножителя на Постоянный коэффициент точки 6 и 7 объединяются. Один из входов компаратора заземляется, на второй подается сигнал правления. В этом случае величина Постоянного коэффициента умножителя определяется величиной относительного изменения коэффициентов передачи по входам 6 и 7. Формула изобретения Инвертор с управляемым ограничением ыходного сигнала, содержащий операцио ый усилитель, выход которого является ь:ходом инвертора и соединен через два оследовательно включенных масштабных езистора с источником входного сигнала через делитель на резисторах - с исочником сигнала ограничения, о т л й

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор с управляемым ограничением выходного сигнала | 1978 |

|

SU744631A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Регулируемый ограничитель | 1980 |

|

SU942055A1 |

| Функциональный частотный преобразователь | 1983 |

|

SU1120365A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Функциональный преобразователь | 1985 |

|

SU1267445A2 |

| Устройство для преобразования сигнала мостового датчика в частоту | 1978 |

|

SU782150A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЧАСТОТУ | 1989 |

|

RU2024195C1 |

| Устройство для моделирования двухстороннего ограничителя механических перемещений исполнительных механизмов | 1990 |

|

SU1742837A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-18—Подача