входом реверсивного счетчика, выход схемы вьиеления сигнала ошибки чере второй запоминающий элемент подключен к управляющему входу генератора импульсов, выход которого соединен с тактовыми входами реверсивного счетчика и дополнительного счетчика, выход дополнительного счетчика подключен к второму входу схемы вьделе ния сигнала ошибки,третий вход которой соединен с управляющим входом дополнительного счетчика и с соответствующим выходом блока синхронизации выход усилителя сигнала ошибки через третий запоминающий элемент подключен к управлякяцему входу элемента

2375

с регулируемым коэффициентом передачи, управляющие входы ключей,первого и третьего запоминающих элементов соединены с соответствующими выходами блока синхронизации,второй вход триггера знака и дополнительный управляющий вход реверсивного счетчика подключены к соответствующим выходам блока синхронизации, выход триггера знака и один из выходов реверсивного счетчика подключены к соответствующим входам блока синхронизации, выходы реверсивного счетчика подключены к входам сдвигающего регистра, выходы которого являются цифровым выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112374A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112373A1 |

| Устройство для логарифмирования отношения сигналов | 1985 |

|

SU1300506A1 |

| Дискретный интегратор | 1975 |

|

SU705468A1 |

| Инвертор с управляемым ограничением выходного сигнала | 1978 |

|

SU746580A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1988 |

|

SU1594692A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

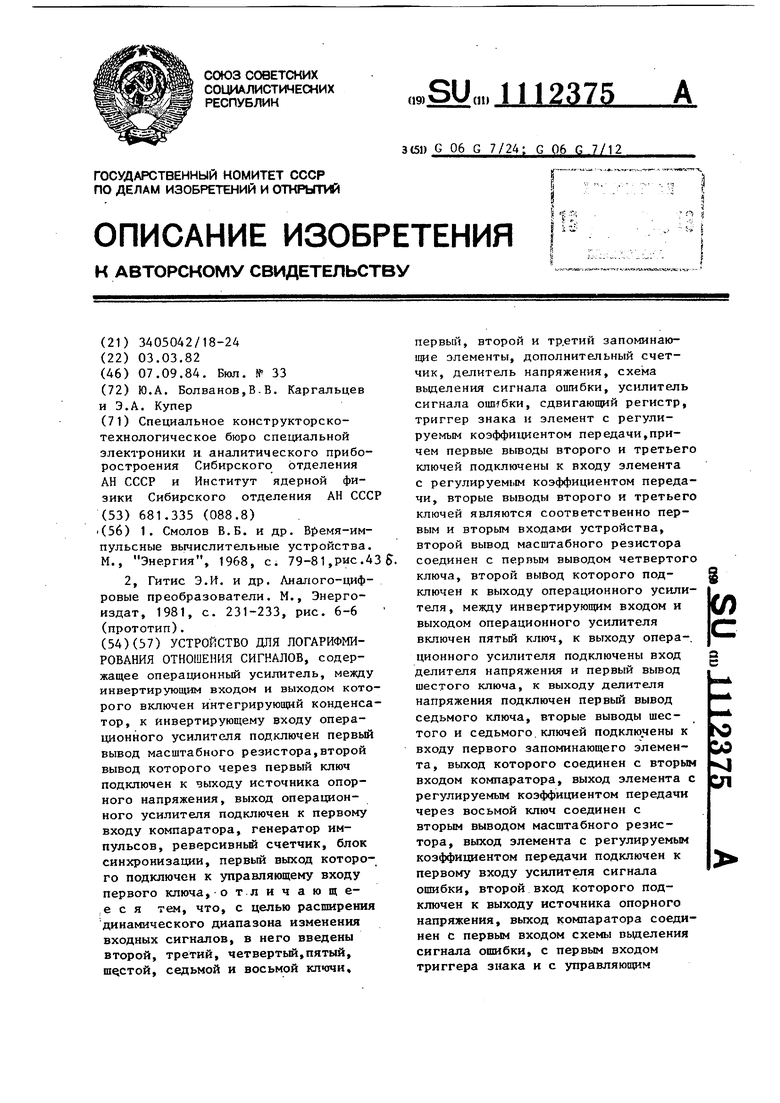

УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ОТНОШЕНИЯ СИГНАЛОВ, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод масщтабного резистора,второй вывод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор импульсов, реверсивный счетчик, блок синхронизации, первый выход которого подключен к управляющему входу первого ключа, о т л и ч а ю щ ее с я тем, что, с целью расширения динамического диапазона изменения входных сигналов, в него введены второй, третий, четвертьА,пятый, шестой, седьмой и восьмой клчгаи. первьй, второй и третий запоминающие элементы, дополнительный счетчик, делитель напряжения, схема выделения сигнала ошибки, усилитель сигнала ошибки, сдвигающий регистр, триггер знака и элемент с регулируемым коэффициентом передачи,причем первые выводы второго и третьего ключей подключены к входу элемента с регулируемым коэффициентом передачи, вторые выводы второго и третьего ключей являются соответственно первым и вторым входами устройства, второй вывод масштабного резистора соединен с первым выводом четвертого g ключа, второй вывод которого подключен к выходу операционного усилителя , между инвертирующим входом и выходом операционного усилителя включен пятый ключ, к выходу опера-, ё ционного усилителя подключены вход делителя напряжения и первый вывод шестого ключа, к выходу делителя напряжения подключен первый вывод седьмого ключа, вторые выводы шесND СО того и седьмого.ключей подключены к входу первого запоминающего элемента, выход которого соединен с вторым сл входом компаратора, выход элемента с регулируемым коэффициентом передачи через восьмой ключ соединен с вторым выводом масштабного резистора, выход элемента с регулируемым коэффициентом передачи подключен к первому входу усилителя сигнала опшбки, второй вход которого подключен к выходу источника опорного напряжения, выход компаратора соединен с первым входом схемы выделения сигнала ошибки, с первым входом триггера знака и с управляющим

Изобретение относится к устройствам преобразования отношения сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах.

Известно устройство для логарифмирования отношения сигналов, содержащее генераторы экспоненциальных напряжений, компаратор, запоминающее устройство, счетчик, генератор импульсов и блок управления l .

Однако устройство имеет низкую помехозащищенность, малый диапазон изменения входных сигналов и низкую точность работы.

Наиболее близким к предложенному является устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вьтод первого Масштабного резистора, второй вывод которого соединен с выходом ключа, вход которого подключен к выходу источника напряжения выход операционного усилителя подключен к входу компаратора, выход которого подключен к входу генератор импульсов, выход которого соединен через второй масштабный резистор с. инвертирующим входом операционного усилителя, выход блока синхронизации

подключен к управляющему входу ключа .и к первому входу элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И

подключен к входу счетчика, выходы которого являются цифровым выходом устройства, второй вход компаратора подключен к выходу источника опорного напряжения 2J .

Однако известное устройство характеризуется низкой помехозащищенностью, имеет малый диапазон отношения сигналов и обладает низкой точностью работы.

Целью изобретения является расширение динамического диапазона изменения входных сигналов.

Поставленная цель достигается

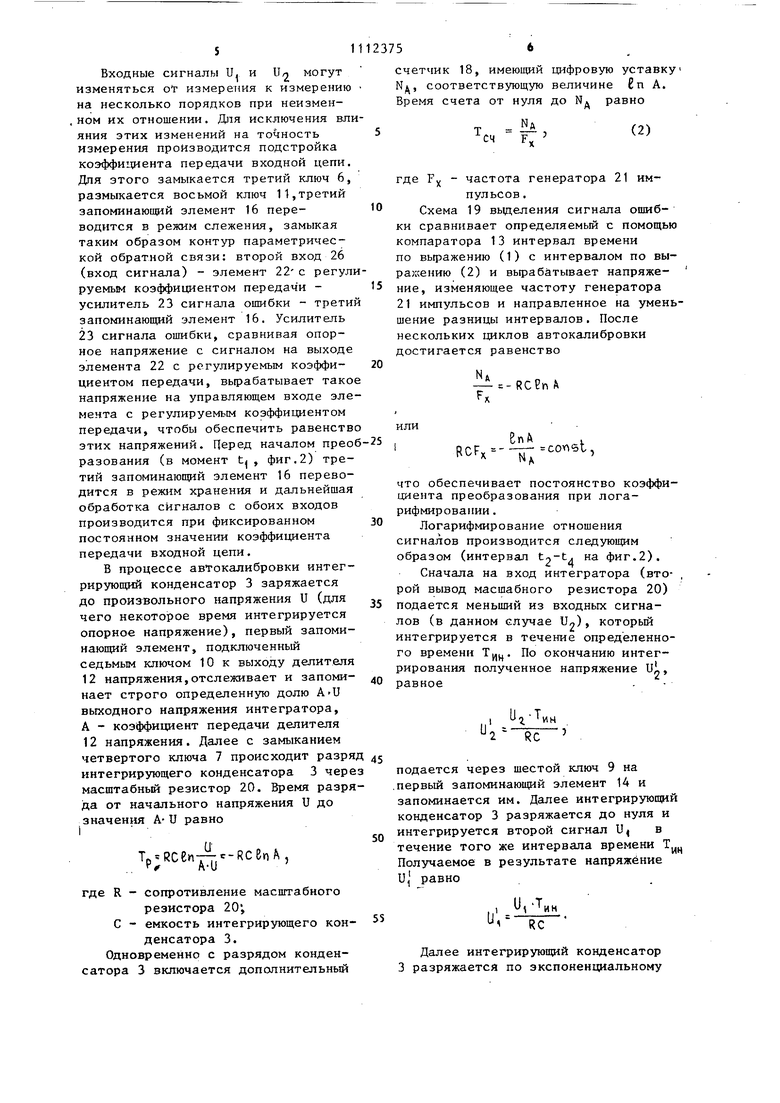

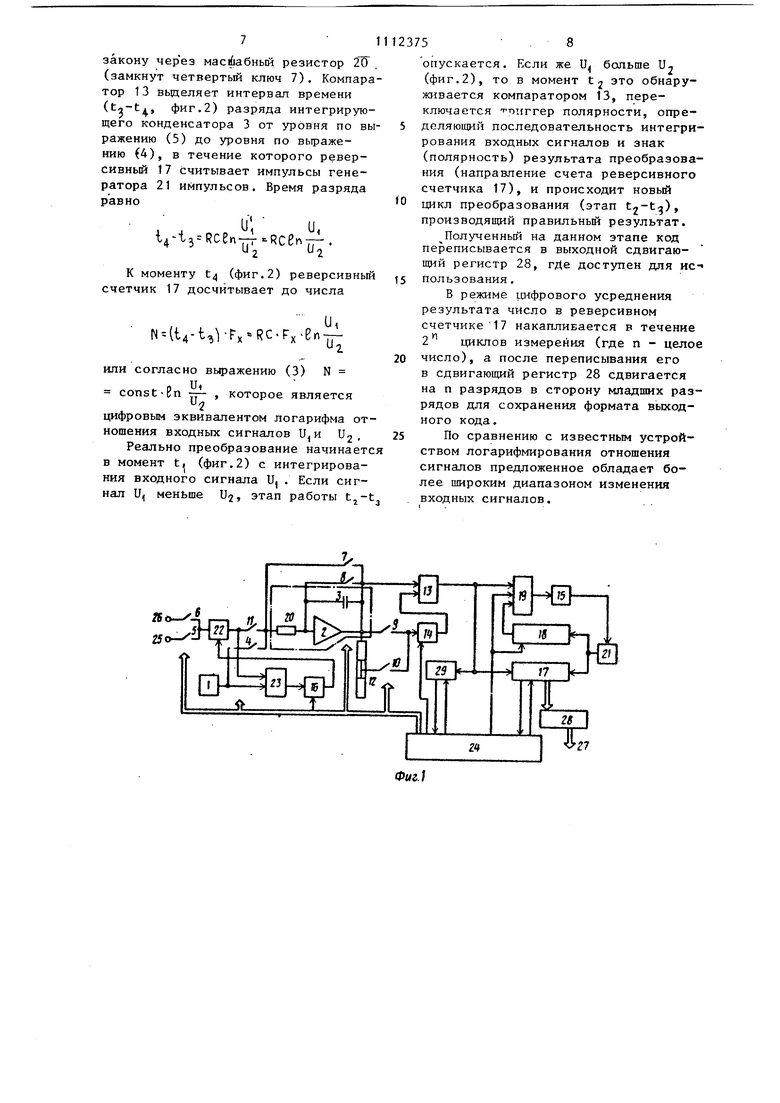

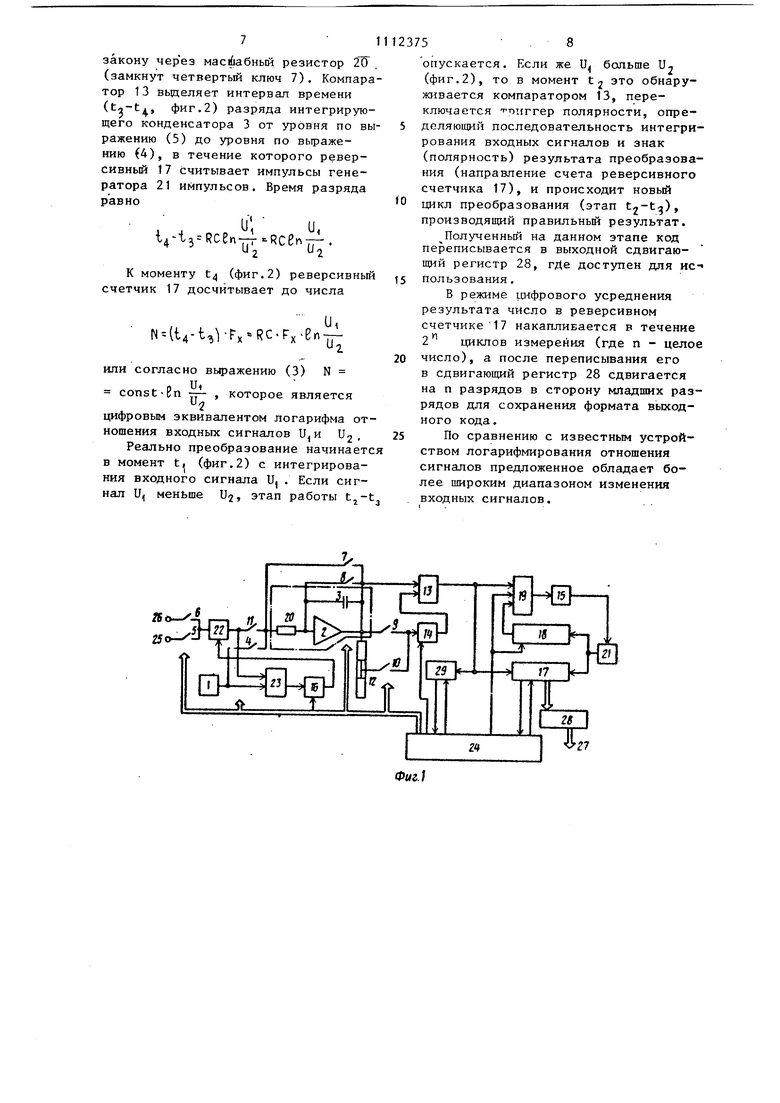

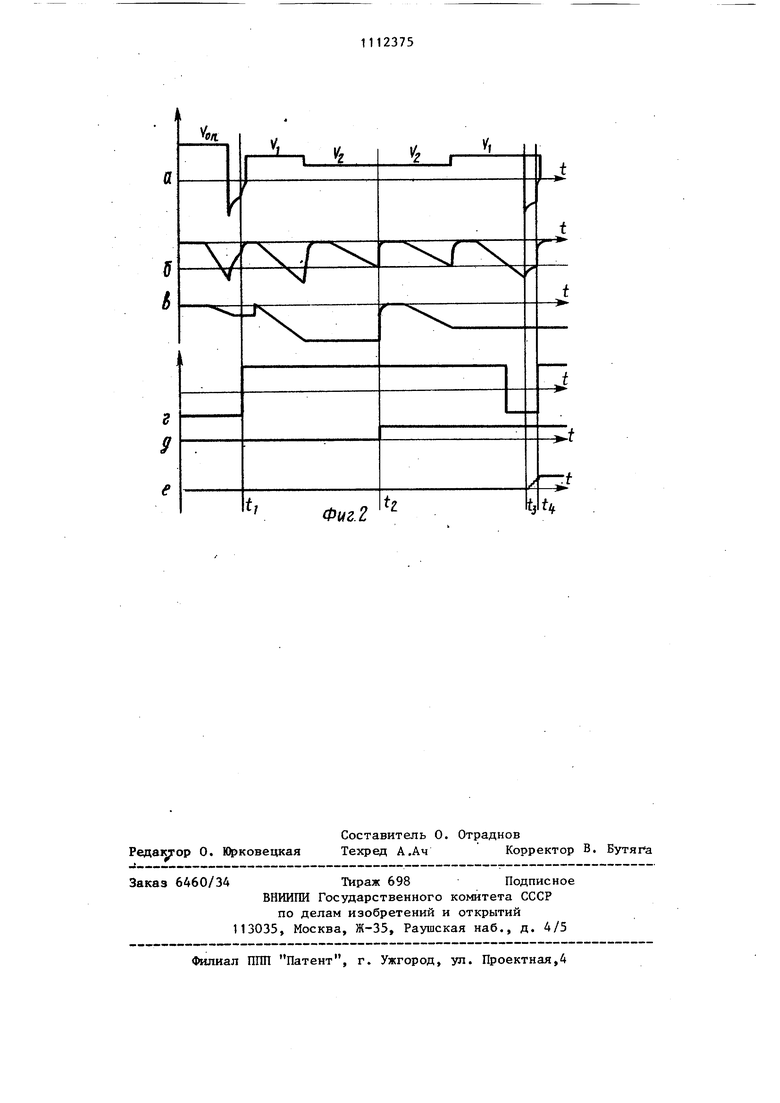

тем, что устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к

инвертирующему входу операционного усилителя подключен первый вывод масштабного резистора, второй вывод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор импульсов, реверсивный счетчик, блок синхронизации,первый выход которого подключен к управляющему входу первого ключа, введены второй, третий, четвертый, пятый, шестой, седьмой и восьмой ключи,пср вьш, второй и третий запоминающие эл менты, дополнительный счетчик, дели тель напряжения, схема вьделения сигнала ошибки, усилитель сигнала ошибки, сдвигающий регистр, триггер знака и элемент с регулируемым коэффициентом передачи,причем перйые выводы второго и третьего ключе подключены к входу элемента с регул руемым коэффициентом передачи,вторы выводы второго и третьего ключей являются соответственно первым и вторым входами устройства, второй вывод масштабного резистора соединен с первым выводом четвертого клю ча, второй вьгоод которого подключен к выходу операционного усилителя, между инвертируюш 1м входом и выходом операционного усилителя включен пятый ключ, к выходу операционного усилителя подключены вход делителя напряжения и первый вывод шестого ключа, к выходу делителя напряжения подключен первый вывод седьмого ключа, вторые выводы шестого и седьмого ключей подключены к входу первого запоминающего элемента, выход которого соединен с вторым входом компаратора, выход элемента с регулируемым коэффициентом передачи через восьмой ключ соединен с вторы выводом масштабного резистора, выход элемента с pei-улируемым коэффициентом передачи подключен к первому входу усилителя сигнала ошибки второй вход которого подключен к выходу источника опорного напряжения, выход компаратора соединен с первым входом схемы выделения сигна ла ошибки, с первым входом триггера знака и с управляющим ёходом реверсивного счетчика, выход схемы вьщел ния сигнала ошибки через второй запоминающий элемент подключен к управляющему входу генератора импульсов, выход которого соединен с тактовыми входами реверсивного счетчик и дополнительного счетчика,выход дополнительного счетчика подключен к второму входу схемы выделения сигнала ошибки, третий вход которой соединен с управляющим входом дополнительного счетчикл и с соответствующим выходом блока синхронизации, выход усилителя сигнала ошиб через третий запоминающий элемент подключен к управляющему входу элемента с регулируемым коэ({)(|эициентом передачи, управляю1ф1е пходы ключей, первого и третьего запоминающих элементов соединены с соответствующими выходами блока синхронизации, второй вход триггера знака и дополнительный управляющий вход реверсивного счетчика подключены к соответствующим выходам блока синхронизации, выход триггера знака и один из выходов реверсивного счетчика подключены к соответствующим входам блока синхронизации,выходы реверсивного счетчика подключены к входам сдвигающего регистра, выходы которого являются цифровым выходом устройства. На фиг.1 изображена функциональная схема устройства для логарифмирования отношения сигналов, на фиг. 2 - временные диаграммы сигналов. Устройство содержит источник 1 опорного напряжения, операционный усилитель 2, интегрирующий конденсатор 3, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой ключи 4-11, делитель 12 напряжения, компаратор 13, первый, второй и третий запоминающие элементы 14-16, реверсивный счетчик 17, дополнительный счетчик 18, схему 19 вьдепения сигнала ошибки, масштабный резистор 20, генератор 21 импульсов, элемент 22 с регулируемым коэффициентом передачи,усилитель 23 сигнала ошибки, блок 24 синхронизации, первьй и второй входы 25 и 26, выход 27 сдвигающий регистр 28 и триггер 29 знака. I На фиг.2 изображены временные диаграммы сигналов: cs - на втором масштабного резистора 20, 5 - на выходе операционного усилителя 2j Ь - на выходе первого запоминающего элемента 14, 1 - на выходе компаратора 13; q - на выходе триггера 29 знака, а также диаграмма е состояния реверсивного счетчика 17. Устройство работает следующим образом. До момента t (фиг.2) осущсствляются одновременно два процесса автокалибровка логарифмирующего преобразователя и автоподстромка коэффициента передачи входной цепи. Входные сигналы U, и U могут изменяться о измерения к измерению на несколько порядков при неизмен, ном их отношении. Для исключения вл яния этих изменений на точность измерения производится подстройка коэффициента передачи входной цепи. Дпя этого замыкается третий ключ 6, размыкается восьморТг ключ 11,третий запоминающий элемент 16 переводится в режим слежения, замыкая таким образом контур параметрической обратной связи: второй вход 26 (вход сигнала) - элемент 22 с регул руемым коэффициентом передачи усилитель 23 сигнала ошибки - трети запоминающий элемент 16. Усилитель 23 сигнала ошибки, сравнивая опорное напряжение с сигналом на выходе элемента 22 с регулируемым коэффициентом передачи, вырабатывает тако напряжение на управляющем входе эле мента с регулируемым коэффициентом передачи, чтобы обеспечить равенств этих напряжений. Перед началом прео разования (в момент t , фиг.2) третий запоминающий элемент 16 переводится в режим хранения и дальнейшая обработка сигналов с обоих входов производится при фиксированном постоянном значении коэффициента передачи входной цепи. В процессе автокалибровки интегрирующий конденсатор 3 заряжается до произвольного напряжения U (для чего некоторое время интегрируется опорное напряжение), первый запоминающий элемент, подключенный седьмым ключом 10 к выходу делителя 12 напряжения,отслеживает и запоминает строго определенную долю A-U выходного напряжения интегратора, А - коэффициент передачи делителя 12 напряжения. Далее с замыканием четвертого ключа 7 происходит разря интегрирующего конденсатора 3 чере масштабный резистор 20. Время разря да от начального напряжения U до значен 1я А-U равно ToRce«-7T,-RceoA, f А-и где R - сопротивление масштабного резистора 20; С - емкость интегрирующего конденсатора 3. Одновременно с разрядом конденсатора 3 включается дополнительный счетчик 18, имеющий цифровую уставку Мд, соответствующую величине п А. Время счета от нуля до N равно т сч г„ где ГУ - частота генератора 21 импульсов . Схема 19 выделения сигнала ошибки сравнивает определяемый с помощью компаратора 13 интервал времени по вьфажению (1) с интервалом по выражению (2) и вьфабатывает напряжение, изменяющее частоту генератора 21 импульсов и направленное на уменьшение разницы интервалов. После нескольких циклов автокалибровки достигается равенство - -RCEn А F Bnft , что обеспечивает постоянство коэффициента преобразования при логарифмировании . Логарифмирование отношения сигналов производится следующим образом (интервал , на фиг,2). Сначала на вход интегратора (второй вывод масшабного резистора 20) подается меньший из входных сигналов (в данном случае Uo), который интегрируется в течение определенного времени Ту|ц. По окончанию интегрирования полученное напряжение UL, равное. . подается через шестой ключ 9 на первый запоминаюш 1й элемент 14 и запоминается им. Далее интегрирующий конденсатор 3 разряжается до нуля и интегрируется второй сигнал U в течение того же интервала времени Т Получаемое в результате напряжение и, равно Далее интегрирующий конденсатор 3 разряжается по экспоненциальному

закону через масйабный резистор 20 (замкнут четвертьй ключ 7). Компаратор 13 вьделяет интервал времени (, фиг.2) разряда интегрирующего конденсатора 3 от уровня по выражению (5) до уровня по вьфажению (4), в течение которого реверсивный 17 считывает импульсы генератора 21 импульсов. Время разряда

равно

/ . 1 и, i4-t3 Rcen-r-Rcen-.

и:

и.

к моменту t4 (фиг.2) реверсивный счетчик 17 досчитывает до числа

и,

N a4-t3V RC.Fxenили согласно выражению (3) N

const-En тг которое является и

цифровым эквивалентом логарифма отношения входных сигналов U2 ,

Реально преобразование начинается в момент t. (фиг.2) с интегрирования входного сигнала U, . Если сигнал и меньше Uj, этап работы Я 6-х. 250Если же и. больше U.

опускается. IJI-JIM лс и 1 л1сшс uj

(фиг.2), то в момент t это обнаруживается компаратором 13, переключается f-nurrep полярности, определяющий последовательность интегрирования входных сигналов и знак (полярность) результата преобразования (направление счета реверсивного счетчика 17), и происходит новый цикл преобразования (этап t2-t), производящий правильный результат.

Полученный на данном этапе код переписывается в выходной сдвигающий регистр 28, гДе доступен для ис-« пользования.

В режиме цифрового усреднения результата число в реверсивном счетчике Ч 7 накапливается в течение 2 циклов измерения (где п - целое число), а после переписывания его в сдвигающий регистр 28 сдвигается на п разрядов в сторону младших разрядов для сохранения формата выходного кода.

По сравнению с известным устройством логарифмирования отношения сигналов предложенное обладает более широким диапазоном изменения входных сигналов.. . Z7

г 9

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Смолов В.Б | |||

| и др | |||

| Время-импульсные вычислительные устройства | |||

| М., Энергия, 1968, с | |||

| Цилиндрический сушильный шкаф с двойными стенками | 0 |

|

SU79A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| Аналого-цифровые преобразователи | |||

| М., Энергоиздат, 1981, с | |||

| Машина для удаления камней из почвы | 1922 |

|

SU231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-07—Публикация

1982-03-03—Подача