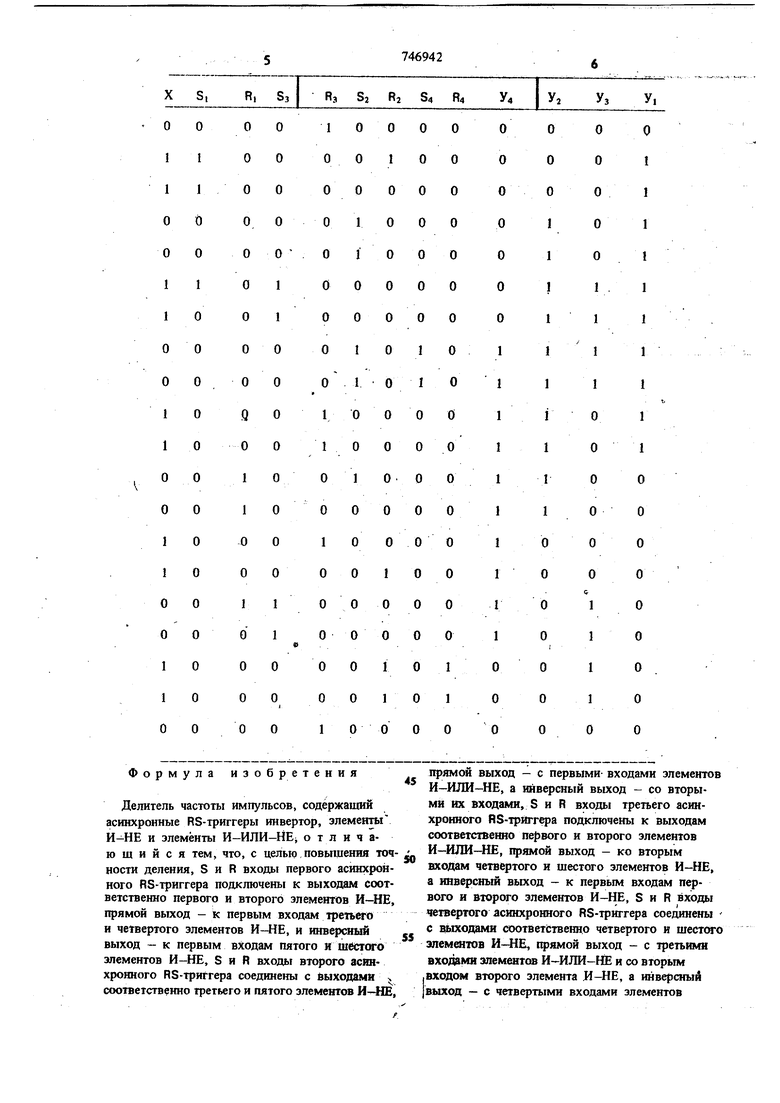

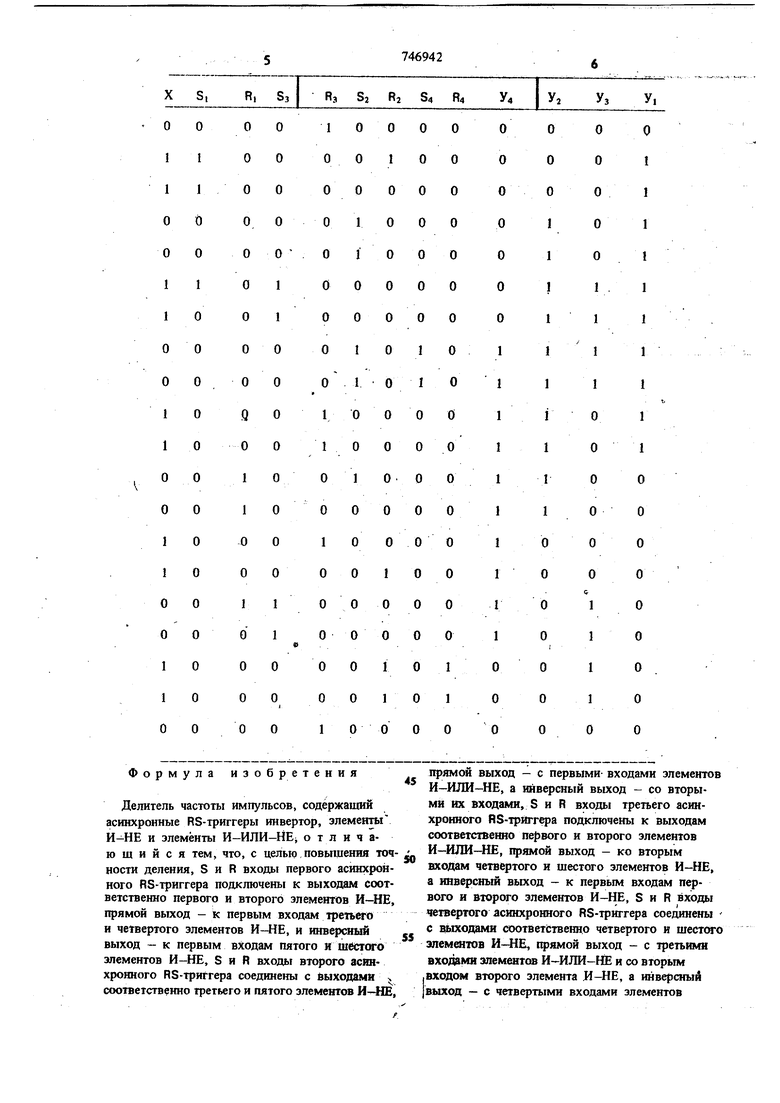

Изобретение относится к импульсной технике, оно может быть использрвано в автоt матике, измерительной и вычислительной техни ке для построения пересчетных схем с дробным коэффициентом деления. Известно пересчетное устройство, состоящее из пересчетной схемы, дискретных и логических схем 11. В ЭТИМ устройстве реализу ется дробный коэффициент пересчета с ошибкой положения выходных импульсов по отношению к импульсам требуемой выходной последовательности, не превосходящей половинь периода входной частоты, для чего прец лагается из входной последовательности импул сов на выход устройства пропускать тoльko те, которые близко отстоят от импульсов требуемой выходной последовательности. Ъднако такое устройство не обеспечивает точного деления частоты. Кроме того, структура пересчетного устройства зависит от вьиодной частоты. Наиболее близкий по технической сущности к изобретению делитель частоты с дробным переменным коэффициентом деления. содержащий декадные счетчики, схемы совпадения, построенные на элементах И-НЕ и инверторах, элементы ИЛИ, трштеры н делитель, составленный из трех декад с переменным коэффициентом деления 12. Однако и это устройство не обеспечивает точного деления частоты, которое может быть получено при подключении к устройству филь- . тра, выделяющего первую гармсдаиКу выходной частоты. Цель изобретения - повышение точности делення. Цель достигается тем, это в делителе частоты импульсов, содержащем асинхронные RSтриггеры, инвертор, эле1у1енть1 И-НЕ и элементы И-ИЛИ-НЕ, S и R входы первого асинхронного RS-триггера подключены к выходам соответст1венно первого и второго элементов И-НЕ, прямой выход - к первым входам третьего и четвертого Элементов И-НЕ, а инверсный выход - к первым входам пятого и шестого элементов И-НЕ, S и R входы второго асинхронного RS-триггера соединены с выходами соот:ветственно третьего и пятого элементов И-НЕ, 37 прямой выход - с первыми входами элементов И-ИЛИ-НЕ, а инверсный выход - со вторыми их входами, S и R входы третьего асинхронкого RS-TpHrrepa подключены к выходам соответственно первого и второго элементов И-ИЛИ-НЕ, прямой выход -, ко вторым входам четвертого и шестого элементов И-НЕ, а инверсный выход - к первым входам первого и второго элементов И-НЕ, S и R входы четвертого асинхронного RS-триггера соединены с выходами соответственно четвертого и шестого элементов И-НЕ, прямой выход - с третьими входами элементов И-ИЛИ-НЕ и со вторым входом второго элемента И-НЕ, а инверсный выход - с четвертыми входами элементов И-ИЛИ-НЕ и со вторьхм входом первого элемента И-НЕ, при этом третьи входы первого и шестого элементов И-НЕ, второй вход пятого элемента И-НЕ и пятые входы элементов И-ИЛИ-НЕ подключены к входной шине непосредственно, а второй вход третьего элемента И-НЕ, третьи входы второго и четвертого элементов И-НЕ и шестые входы элементов И-ИЛИ-НЕ - через инвертор. На чертеже представлена структурная электрическая схема делителя частоты. Делитель частоты содержит асинхр01шные RS триггеры 1-4, инвертор 5, элементы И-НЕ 6-11, элементы И-ИЛИ-НЕ 12 и 13. Входная шина 14 делителя частоты соединена со входом инвертора 5, с третьим входом первого элемента И-НЕ 6, выход которого соединен с S-входом первого триггера 1; с входом первого элемента И-ИЛИ-НЕ 12, выход которого соединен с S входом третьего триггера 3; с входом второго элемента И-ИЛИ-НЕ 13, выход которого соединен с R-входом третьего триггера 3; с третьим входом шестого элемента И-НЕ11, выход которого соединен с R-входом четвертого триггера 4; и вторым входом пятого элемента И-НЕ 10, выход кото рого соединен с R-входом второго триггера 2. Выход инвертора 5 соединен с третьим входом второго элемента И-НЕ 7, выход которого соединен с R-входоМ первого триггера 1, со входами первого элемента И-ИЛИ-НЕ 12 и второго элемента И-РШИ-НЕ 13, с входами вторым третьего 8 и третьи четвертого 9 , элементов И-НЕ 13, с Входами вторым третье го 8 и третьим четвертого 9 элементов И-НЕ, выходы которых соединены с S-входами соответственно четвёртого 4 и второго 2 триггеров Прямой вход первого триггера 1 соединен с первыми входами третьего 8 и четвертого 9 элементов И-НЕ, инверсный выход Первого триггера 1 соединен с первыми входами пятог 10 и шестого 11 элементов И-НЕ, прямой выход третьего триггера 3 соединен с вторыми входами четвертого 9 и шестого II элементов И-НЕ, инверсный выход третьего триггера 3 соединен с первыми входами первого 6 и второго 7 элементов И-НЕ, прямой выход второго триггера 2 соединен с входами первого элемента И-ИЛИ-НЕ 12 и второго элемента И-ИЛИ-НЕ 13, инверсный выход второго триггера 2 соединен со входами первого элемента И-ИЛИ-НЕ 12 и второго элемента И-ИЛИ-НЕ 13, прямой выход четвертого триггера 4 соединен со вторым входом второго элемента И-НЕ 7, с входами первого 12 и второго 13 элементов И-ИЛИ-НЕ, инверсный выход четвертого триггера 4 соединен с вторым входом первого элемента И-НЕ 6, со входами первого 12 и второго 13 элементов И-ИЛИ-НЕ. Устройство работает следуюшим образом. Пусть первоначально все RS-триггеры находятся в нулевом состоянии и на входной шине 14 делителя частоты входной сигнал . Учитывая, что S, У4УзХ R, У4 УЗ X SB У4 + У4 YZ X RS X + У4 Уг X Sz У1 X RZ У, X R4 y3yiX 84 УЗ У X где Si,Rj-логические переменные, описываюшие сигналы на входах {-ого триггера; У - логическая переменная, описываюшая сигнал на выходе |-ого триггера; X - логическая переменная, описываюшая входной сигнал. Получаем Si Ri О, Sa О, Ra 1, Sa RZ 84 R4 0. В соответствии с принципом работы RS-триггера все выходные сигналы не изменят своих уровней, т.е. У Уг УЗ У4 - О С приходом X 1 на входах RS-трштербв устанавливаются сигналы Si 1, Rj О, Sa R3 О, 8з О, Ra 1, S4 rR4 0 и RS-трштер 1 изменяет свое состояние, т.е. У 1,а У УЗ У4 0. Изменение состояния RS-триггера 1 приводит при неизменном к изменению сигнала на R-входе RS-триггера 2 (Ra 1), которое не изменит состояние триггеров. Дальнейшее изменение состояний триггеров при изменении входных сигналов отражено в таблице переключений триггеров. Формула изобретения Делитель частоты импульсов, содержащий асинхронные RS-триггеры инвертор, элементы И-НЕ и элементы И-ИЛИ-НЕ отличающийся тем, что, с целью повышения точности деления, S и R входы первого асинхронного RS-триггера подключены к выходам соответственно первого и второго элементов И-НЕ, прямой выход - к первым входам третьего и четвертого элементов И-НЕ, и инверсный выход к первым входам пятого и шестото элементов И-НЕ, S и R входы второго асинхронного RS-триггера соединены с выходами ч соответственно третьего и пятого элементов И-НЕ, 1ФЯМОЙ выход - с первыми- входами элементов И-ИЛИ-НЕ, а инверсный выход - со вторыми их входами, S и В входы третьего асинхронного RS-трйггера подключены к выходам соответственно первого и второго элементов И-ИЛИ-НЕ, прямой выход - ко вторым входам четвертого и щестого элементов И-НЕ, а инверсный выход - к первьпи входам первого и второго элементов И-НЕ, S и R входы четвертого асинхронного RS-триггера соединены с цькодами соответственно четвертого и шестого элементов И-НЕ, прямой выход - с третьими входами элементов И-ИЛИ-НЕ и со вторым входом второго элемента .И-НЕ, а инверсный выход - с четвертыми входами элемет-ов |И-ШТИ-НЕ и со нюрШ вхййом пёрёго элемента И-НЕ, эдш tfietKit мвда и шестого элементов И-НЕ, второй вход пятого элемента Й-НЁ и пятые входы элементов Й-ЙЛИ-НЕ подключены к входной ишне непосредственно, а второй вход третьего элемента И-НЕ,третьн входы второго и четвертого элементов И-НЕ и шестое входы элементов И-ИЛИ-НЕ - через инвертор. Источники информаини, принятые во внимание при экспертизе i. Авторское свидетельство СССР N 4253586, - Н 03 К 23/00, 1972. 2. Авторское свидетельство СССР № 506130, кл. Н 03 К 23/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления инвертором напряжения в электроприводе переменного тока | 1990 |

|

SU1737678A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

| СПОСОБ УПРАВЛЕНИЯ ЧАСТОТНЫМ АСИНХРОННЫМ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2081503C1 |

| Программируемый преобразователь код-фаза | 1984 |

|

SU1236389A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1987 |

|

SU1422356A1 |

| Многофункциональное счетное устройство | 1985 |

|

SU1298911A2 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

Авторы

Даты

1980-07-23—Публикация

1977-12-19—Подача