Изобретение относится к радиотехнике и может быть использовано в системах радиосвязи и измерения дальности.

Современное состояние техники в указанной области и тенденции ее развития, а также вопросы теории рассмотрены в [1].

Однако в научно-технической литературе отсутствуют сведения, касающиеся способов и устройств, реализующих как децимацию, так и редецимацию M-последовательностей с помощью одного устройства.

Данное предложение направлено на решение этой задачи.

Наиболее близким по технической сущности к решаемой задаче является устройство для формирования M-последовательностей [2], содержащее: генератор тактовых импульсов, делитель с переменным коэффициентом деления, счетный вход которого подключен к выходу генератора тактовых импульсов, а вход установки коэффициента деления является входом устройства, генератор псевдослучайных последовательностей (ПСП), тактовый вход которого подключен к выходу генератора тактовых импульсов, регистр хранения, тактовый вход которого подключен к выходу делителя с переменным коэффициентом деления, а информационные входы - к соответствующим выходам генератора псевдослучайных последовательностей, параллельный выход регистра хранения является выходом устройства.

Известное устройство позволяет получать различные M-последовательности путем децимации циклических сдвигов исходной M-последовательности, формируемой с помощью регистра сдвига с обратной связью

Известное устройство позволяет осуществлять децимацию исходной M-последовательности и получать на выходе циклические сдвиги децимированной ПСП.

Однако известное устройство не позволяет осуществлять редецимацию исходной M-последовательности и также имеет существенный недостаток: различные ПСП на выходе будут иметь другую тактовую частоту, которая в q раз меньше тактовой частоты исходной ПСП.

Цель изобретения - расширение функциональных возможностей за счет реализации с помощью одного устройства операций децимации и редецимации исходной M-последовательности с одинаковой выходной тактовой частотой, не зависящей от индексов как децимации, так и редецимации.

Поставленная цель достигается тем, что в устройство преобразования, содержащее генератор тактовых импульсов, вход запуска которого соединен с входом "Пуск" устройства, делитель с переменным коэффициентом деления, состоящий из задатчика коэффициента деления и собственно делителя, тактовый вход которого подключен к выходу генератора тактовых импульсов, входы установки коэффициента деления - к соответствующим выходам задатчика коэффициента деления, входные шины записи коэффициентов деления n и q - к соответствующим входам задатчика коэффициента деления, вход, синхронизирующий момент записи числа n к входу "Пуск" устройства, а вход, синхронизирующий момент записи числа q, - к выходу делителя, генератор M-последовательностей, состоящий из задатчика номеров циклических сдвигов и собственно генератора M-последовательностей, входная шина записи номера X циклического сдвига которого подключена к соответствующим входам задатчика номеров циклических сдвигов, входы загрузки начального состояния генератора M-последовательностей - к соответствующим выходам задатчика номеров циклических сдвигов, входная шина z изменения образующего полинома подключена к соответствующим входам генератора M-последовательностей, вход, синхронизирующий момент загрузки начального состояния в генератор M-последовательностей, к входу "Пуск" устройства, введены задатчик номера циклического сдвига, выходы которого подключены к входам установки начального состояния генератора M-последовательностей, первый элемент задержки, вход которого подключен к выходу генератора тактовых импульсов, первый элемент И, первый RS-триггер, второй элемент И, первый управляемый ключ, первый элемент ИЛИ, второй элемент задержки, второй RS-триггер, второй управляемый ключ, третий элемент И, счетчик адресов, входы установки модуля счета которого подключены к выходам задатчика модуля счета, счетчик циклов, установочные входы которого соединены с выходами задатчика модуля счета счетчика циклов, третий управляемый ключ, третий RS-триггер, четвертый элемент И, пятый элемент И, шестой элемент И, третий элемент задержки, группа из n элементов И, второй элемент ИЛИ, формирователь импульсов выборки, группа из n формирователей импульсов, группа из n оперативных запоминающих устройств, группа из n D-триггеров, при этом вход задатчика номеров циклических сдвигов соединен с третьей входной шиной X, вход задатчика модуля счета подключен к четвертой входной шине N, выход первого элемента задержки подключен к первому входу первого элемента И, второй вход которого подключен к инверсному выходу первого RS-триггера, R-вход которого подключен к шине "Пуск", S-вход первого RS-триггера подключен к выходу делителя с переменным коэффициентом деления и к входу второго элемента задержки, выход которого соединен с входом второго RS-триггера, прямой выход первого RS-триггера соединен с входом второго элемента И, второй вход которого подключен к выходу первого элемента задержки, вход второго элемента И соединен с входом первого управляемого ключа, второй вход которого подключен к выходу делителя с переменным коэффициентом деления, выход первого управляемого ключа подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу первого элемента И, а выход которого подключен к тактирующему входу генератора M-последоваптельностей, R-вход второго RS-триггера подключен к выходу генератора тактовых импульсов, входу второго управляемого ключа и к входу третьего элемента задержки, второй вход второго управляемого ключа подключен к выходу делителя с переменным коэффициентом деления, выход второго управляемого ключа подсоединен к входу третьего элемента И, второй вход которого подключен к прямому выходу первого RS-триггера, а выход третьего элемента И подключен к счетному входу счетчика адресов, вход задатчика модуля счета соединен с выходом счетчика адресов, вход задатчика модуля счета соединен с четвертой входной шиной N, второй вход задатчика модуля счета соединен с выходом счетчика адресов, со счетным входом счетчика циклов и с первым входом третьего управляемого ключа, второй вход которого соединен с выходом счетчика циклов и с входом переноса задатчика модуля счетчика циклов, установочные входы которого соединены с шиной индекса редецимации q, выход третьего управляемого ключа соединен с S-входом третьего RS-триггера, инверсный вход которого подключен к входу четвертого элемента И, выход которого соединен с управляющим входом второго управляемого ключа, прямой выход третьего RS-триггера подключен к входу пятого элемента И, второй вход которого подключен к второму входу шестого элемента И и к выходу третьего элемента задержки, первый вход шестого элемента И и первые входы элементов И группы из n элементов И подключены к инверсному выходу третьего RS-триггера, третий вход шестого элемента И соединен с вторыми входами элементов И группы из n элементов И и подключен к прямому выходу второго RS-триггера, третьи входы элементов И группы из n элементов И подключены к соответствующим n выходам генератора M-последовательностей, выходы пятого и шестого элементов И подключены к входам второго элемента ИЛИ, выход которого соединен с входом формирователя импульсов выборки, выход которого подключен к входам выборки оперативных запоминающих устройств группы из n оперативных запоминающих устройств, выходы элементов И группы из n элементов И подключены к входам соответствующих формирователей импульсов группы из n формирователей импульсов, выходы которых подключены к соответствующим информационным входам оперативных запоминающих устройств группы из n оперативных запоминающих устройств, адресные входы которых подключены к соответствующим параллельным выходам счетчика адресов, входы управления записью оперативных запоминающих устройств соединены вместе и подключены к инверсному выходу третьего RS-триггера, выходы оперативных запоминающих устройств группы из n оперативных запоминающих устройств подключены к входам соответствующих D-триггеров группы из n D-триггеров, входы синхронизации которых соединены вместе и подключены к выходу формирователя импульсов выборки, выходы D-триггеров группы из n D-триггеров являются выходами устройства для преобразования M-последовательностей, установочный вход задатчика номеров циклических сдвигов, установочный вход задатчика модуля счета, синхронизирующий вход задатчика модуля счета счетчика циклов, R-вход первого RS-триггера и R-вход третьего RS-триггера соединены с шиной "Пуск" устройства для преобразования M-последовательностей, управляющий вход первого управляемого ключа соединен с управляющим входом третьего управляемого ключа и с входом четвертого элемента И и является входом управления режимом децимации или редецимации устройства преобразования M-последовательностей.

Анализ перечисленных выше признаков предложенного технического решения показывает, что для решения поставленной задачи - выполнения своего назначения и создания положительного эффекта - их совокупность не требует добавления других признаков, т.е. является достаточной. Следовательно, все эти признаки являются существенными, а их совокупность характеризует завершенное техническое решение.

Сравнение предложения с прототипом показывает, что оно имеет отличия. Введенные признаки доказывают новизну предложения.

В прототипе реализуется только децимация исходной M-последовательности, а тактовая частота результирующей M-последовательности будет различной в зависимости от коэффициента деления делителя с переменным коэффициентом деления (ДПКД).

По сравнению с известным устройством в предложенном устройстве осуществляется как децимация, так и редецимация исходной M-последовательности и ее циклических сдвигов. При этом тактовая частота как децимированной, так и редецимированной M-последовательностей постоянна и не зависит от индекса как децимации, так и редецимации. Таким образом, положительный эффект, создаваемый предложенным устройством, заключается в расширении функциональных возможностей.

Исследование роли указанных выше отличий в динамике показывает, что исключение любого из них делает невозможным получение положительного эффекта при использовании предложения. Это свидетельствует о существовании непосредственной причинно-следственной связи между этими отличиями и положительным эффектом, указанным в цели изобретения.

Все эти отличия могут быть разделены на абсолютные (блоки, узлы, элементы) и относительные, или взаимные, характеризующие взаимодействие между абсолютными отличиями (соединения между ними и со "старыми" блоками, узлами, элементами).

В данном предложении отличия абсолютного типа (RS-триггер, элементы И, ИЛИ, управляемые ключи, ОЗУ, формирователи импульсов, триггеры, элементы задержки) известны из технической литературы. Однако в известных решениях они не направлены на решение задачи децимации и редецимации исходной M-последовательности в рамках одного устройства, т.е. на создание такого же положительного эффекта, как в предложении. Следовательно, указанные выше абсолютные отличительные признаки являются существенными.

Что же касается отличий взаимного типа, новых связей, то они либо отсутствуют в литературе, либо известны, но при этом обеспечивают создание другого положительного эффекта так, что и они должны быть также отнесены к категории существенных. Следовательно, все перечисленные отличия являются существенными.

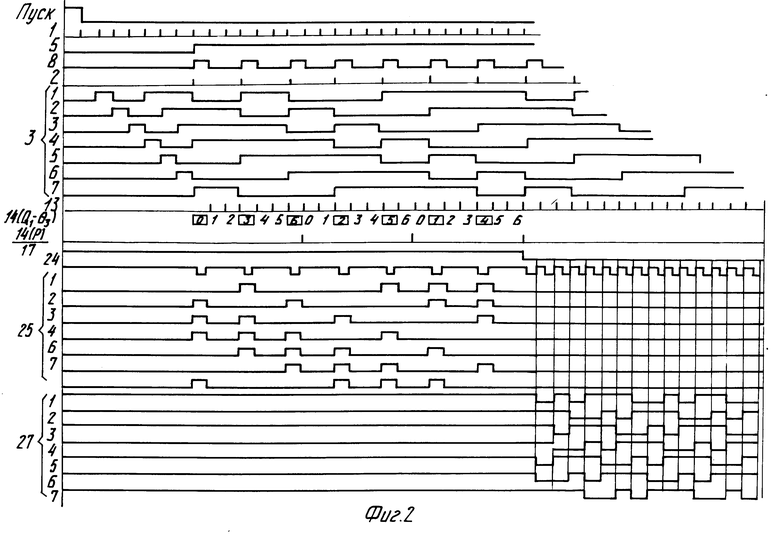

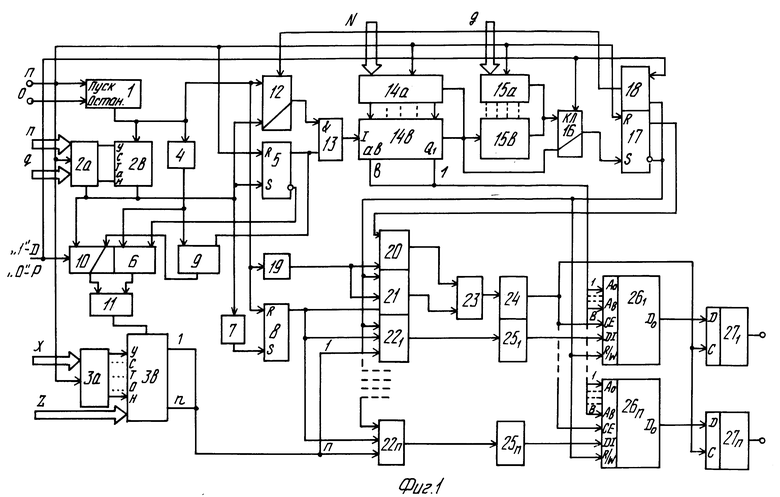

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства в режиме децимации.

Слева от диаграмм написаны номера устройств фиг. 1, на выходах которых они наблюдаются.

Адреса на выходе счетчика адресов 14b представлены в десятичной форме записи.

Задержки, обеспечивающие работоспособность устройства, на временных диаграммах условно не показаны.

На временных диаграммах проиллюстрирована работа устройства для частного случая, тогда период исходной M-последовательности равен n-7, а индекс редецимации и децимации q=3.

На фиг. 1 положения управляемых ключей Кл. 10, 12, 16 соответствуют режиму децимации.

Устройство преобразования M-последовательностей содержит: генератор 1 тактовых импульсов, делитель 2 с переменным коэффициентом деления, состоящий из задатчика 2a коэффициента деления и собственно делителя 2b, генератор 3 M-последовательностей, состоящий из задатчика номеров циклических сдвигов 3a и собственно генератора M-последовательностей 3b, первого элемента задержки 4, первого RS-триггера 5, первого элемента И 6, второго элемента задержки 7, второго RS-триггера 8, второго элемента И 9, первого управляемого ключа 10, первого элемента ИЛИ 11, второго управляемого ключа 12, третьего элемента И 13, счетчика адресов 14, состоящего из задатчика модуля счета 14a и собственно счетчика 14b, счетчика циклов 15, состоящего из задатчика модуля счета 15a и собственно счетчика 15b, третьего управляемого ключа 16, третьего RS-триггера 17, четвертого элемента И 18, третьего элемента задержки 19, пятого и шестого элементов И 20, 21, n седьмых элементов И 221 - 22n, второй элемент ИЛИ 23, формирователь импульсов выборки ячеек ОЗУ 24, n формирователей импульсов 251 - 25n, n оперативных запоминающих устройств 261 - 26n, n D-триггеров 271 - 27n.

К числу нестандартных признаков относятся:

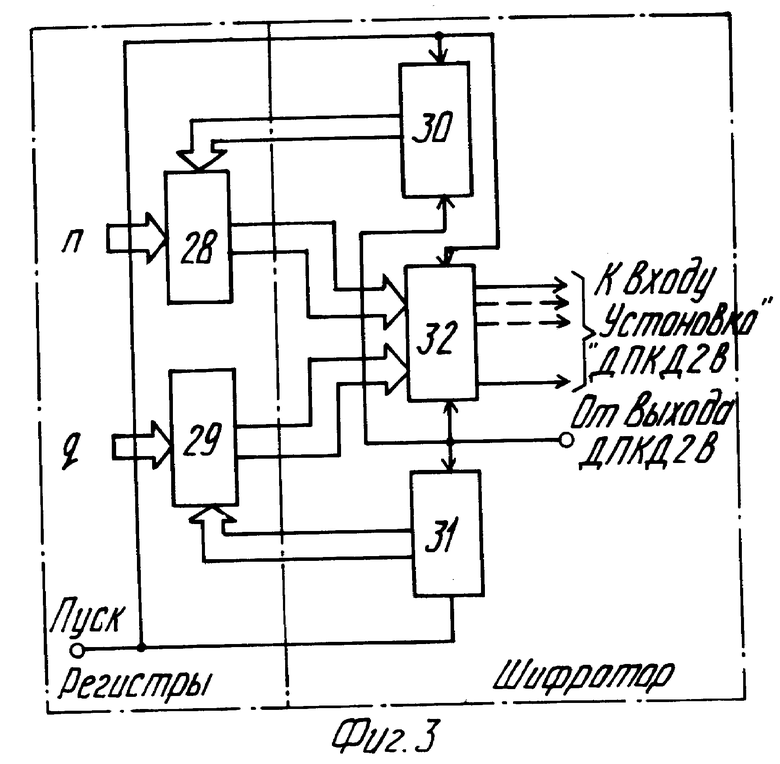

- задатчик коэффициента деления 2a содержит два параллельных регистра для записи в них чисел n и q и шифратор, преобразующий записанные в регистрах числа в код управления коэффициентом деления делителя 2b, причем по сигналу "Пуск" в делитель вводится код, соответствующий числу n и устанавливающий коэффициент деления делителя 2b, равный n, а по импульсу с выхода делителя 2b в него вводится код, соответствующий числу q и устанавливающий коэффициент деления делителя 2b, равный q;

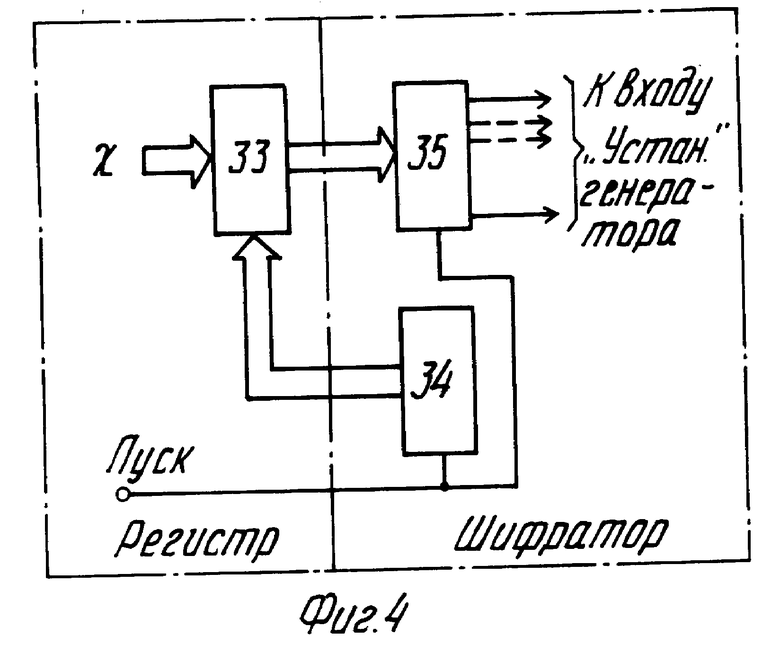

- задатчик модуля циклического сдвига 3a содержит параллельный регистр хранения номера сдвига X и шифратор, преобразующий этот номер в код, загружаемый в генератор M-последовательностей 3b по сигналу "Пуск" и определяющий начальное состояние генератора 3b, соответствующее номеру циклического сдвига;

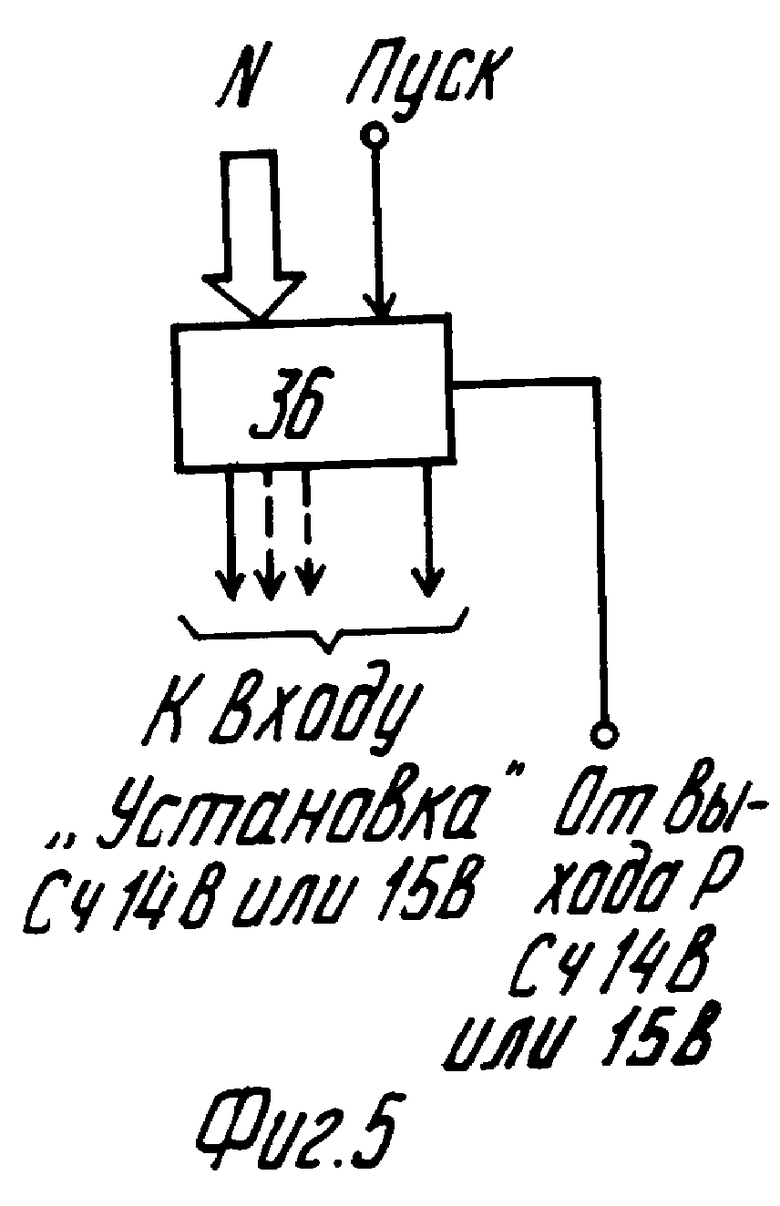

- генератор M-последовательностей содержит сдвиговый регистр, сумматоры по модулю 2 и управляемые ключи. Изменение образующего полинома осуществляется путем изменения характера обратных связей в генераторе путем управления ключами по шине Z;

- задатчик модуля счета 15a устроен аналогичным образом с той лишь разницей, что имеет один параллельный регистр, в который записывается число q, и шифратор, с выхода которого код, соответствующий числу q, записывается в счетчик 15b либо по сигналу "Пуск", либо по сигналу переноса с выхода счетчика;

- задатчик модуля счета 14a устроен аналогично 15a с той лишь разницей, что отсутствует шифратор и число N загружается в счетчик 14b либо по сигналу "Пуск", либо по сигналу "Перенос" с выхода счетчика 14b.

Функциональная схема задатчика коэффициента деления 2a приведена на фиг. 4 и содержит: регистр 28 хранения числа n, регистр 29 хранения числа q и шифратор, содержащий преобразователи 30, 31 сигналов управления задатчика 2a в коды управления регистрами 28, 29 и преобразователи 32 чисел n и q в коды управления делителя 2b.

Задатчик работает следующим образом.

По сигналу "Пуск" преобразователи 3 и 4 разрешают загрузку чисел n и q в регистры 28 и 29. Соответственно число n с параллельного выхода регистра 28 преобразуется преобразователем 32 в код управления делителя 2b, который с выхода преобразователя 32 устанавливает коэффициент деления делителя 2b равным n. Импульс с выхода делителя 2b разрешает выдачу чисел q из регистра 29 и преобразование его преобразователем 32 в код управления делителя 2b, а также через преобразователь 30 запрещает выдачу числа n из регистра 1, при этом коэффициент деления делителя 2b становится равным q.

Функциональная схема задатчика номеров циклических сдвигов представлена на фиг. 4 и содержит: регистр 33 хранения числа X - номера циклического сдвига и шифратор, содержащий преобразователь 34 сигналов управления задатчиков в коды управления регистром 33 и преобразователь 35 числа X в код начальной установки генератора 3b.

Задатчик работает следующим образом.

По сигналу "Пуск" преобразователь 34 разрешает загрузку числа X в регистр 33 и преобразование его преобразователем 35 в код начальной установки генератора 3b.

С выхода преобразователя 35 код начальной установки загружается в генератор 3b.

Функциональная схема задатчика модуля счета 14a и 15a одинакова и представлена на фиг. 5 и содержит регистр хранения числа N или q соответственно.

Задатчик работает следующим образом.

По сигналу "Пуск" разрешается запись числа N и q в регистр 36 и загрузка его в счетчики 14b и 15b по входам "Установка". По сигналу "Перенос" "P" от счетчиков 14b и 15b разрешается загрузка числа N и q из регистра 36 в счетчики 14b и 15b.

Устройство преобразования M-последовательностей работает следующим образом.

Сначала осуществляется инициализация устройства путем асинхронной записи чисел N, n, q, x и z в соответствующие задатчики. На вход выбора режима подается уровень лог. "1" при децимации и уровень лог."0" при редецимации.

Рассмотрим работу устройства в режиме децимации.

По переднему фронту сигнала "Пуск" происходит установка в "0" RS-триггеров 5 и 17, запись в делитель 2 модуля коэффициента деления, равного n, запись в счетчик адресов 14 числа, равного

N = c - n,

где

n - период исходной M-последовательности;

c - модуль счета счетчика адресов, зависящий от числа его разрядов и определяемый выражением

C = 2k - 1,

где

k - число разрядов в счетчике адресов,

запись в счетчик циклов 15 индекса децимации или редецимации, запись в генератор начальной комбинации, определяющей начальный циклический сдвиг M-последовательностей.

По заднему фронту сигнала "Пуск" происходит запуск генератора 1. Импульсы с выхода генератора через элемент задержки 4 и элемент И 6, прохождение через который разрешено уровнем лог."1" с инверсного выхода RS-триггера 5, а также через элемент ИЛИ 11 тактируют генератор 3. Время задержки элемента задержки 4 выбирается равным

τЭ34= τСРДПКД2+τсрR-S5

На выходах генераторов 1, ... n постепенно (см. диаграмму 31-3n фиг. 2) начинают появляться последовательные циклические сдвиги исходной M-последовательности. После n тактовых импульсов от генератора 1 на выходе делителя 2 появляется импульс, который устанавливает RS-триггер 5 в "1", а через время задержки, равное длительности тактового импульса и задаваемое элементом задержки 7, устанавливает RS-триггер 8 в "1", начиная формирование на его прямом выходе интервала выборки из такта исходной M-последовательности. Этот же импульс с выхода делителя 2 через датчик модуля коэффициента деления задатчика 2a устанавливает коэффициент деления делителя 2 равным выбранному индексу децимации или редецимации q.

Уровень лог. "1" с прямого выхода RS-триггера 5 разрешает прохождение импульсов с выхода генератора 1 через элемент задержки 4 и элемент И 9 и далее через ключ 10 и элемент ИЛИ 11 на вход генератора 3, а также разрешает прохождение импульсов с выхода делителя 2 через ключ 12, элемент И 13 на счетный вход 1 счетчика адресов 14.

Следующий тактовый импульс с выхода генератора 1 устанавливает RS-триггер 8 в "0", заканчивая формирование на его прямой выход интервала выборки.

Предшествующий тактовый импульс, задержанный элементом задержки 19 на время, равное

τЭ319= τЭ37+τсрТг8,

где

τЭ37 - время задержки элемента задержки 7;

τсрТг8 - время срабатывания RS-триггера 8,

проходит через элемент И 21, на первом входе которого действует разрешающий потенциал (ур. лог."1") с выхода RS-триггера 17, а на третьем входе - разрешающий элемент в виде интервала выборки с выхода RS-триггера 8. С выхода элемента И 21 импульс через элемент ИЛИ 23 поступает на формирователь 24, который формирует импульс выборки ячейки ОЗУ. На выходах элементов И 221 - 22n импульс интервала выборки с выхода RS-триггера 8 формирует значения выборки из такта n циклических сдвигов исходной M-последовательности, которые через формирователь 251 - 25n записываются в оперативные запоминающие устройства 261 - 26n по адресу, сформированному к этому моменту времени счетчиков адресов 14.

Далее устройство работает аналогичным образом до момента появления импульса переноса на выходе P счетчика адресов 14 после n импульсов с выхода делителя 2, прошедших через ключ 12, элемент И 13 на вход 1 счетчика 14 и подсчитанных этим счетчиком. Импульс переноса с выхода P счетчика 14 через ключ 16 устанавливает RS-триггер 17 в "1", а также через задатчик числа N 14a записывает число N в счетчик 14, осуществляя таким образом его предустановку.

Уровень лог. "0" с инверсного выхода RS-триггера 17 запрещает прохождение сигналов через элементы И 21, 221 - 22n и переключает ОЗУ 261 - 26n в режим считывания, а через элемент И 18 подключает выход ключа 12 к выходу генератора 1, т.е. в режиме считывания адреса ОЗУ будет переключаться в частотой генератора 1.

Уровень лог. "1" с прямого выхода RS-триггера 17 разрешает прохождение тактовых импульсов генератора 1 с выхода элемента задержки 19 через элемент И 20 и далее через элемент ИЛИ 23 на формирователь 24 для формирования импульсов выборки ячеек ОЗУ с частотой генератора 1.

Последовательным перебором адресов ОЗУ 261 - 26n счетчиком 14 с частотой генератора 1 осуществляется считывание из ОЗУ 261 - 26n записанной ранее информации, которая появляется на выходах D0 в виде импульсов с длительностью, равной длительности импульсов выборки ячеек ОЗУ. Для того, чтобы длительность импульсов выходной последовательности устройства равнялась длительности такта генератора 1, импульсы с выходов ОЗУ 261 - 26n записываются в соответствующие D-триггеры 271 - 27n задним фронтом импульсов выборки ячеек ОЗУ с выхода формирователя 24.

В режиме редeцимации устройство работает аналогичным образом с той лишь разницей, что уровень лог."0" с входа управлением режимом децимации/редецимации переключает ключ 10 на выход делителя, ключ 12 через элемент И 18 - на выход генератора 1, а ключ 16 - на выход P счетчика циклов 15 по модулю q.

При этом генератор 3 после N тактовых импульсов генератора 1 с момента появления импульса "Пуск", т.е. после установки в "1" RS-триггера 5, работает с частотой в q раз ниже частоты генератора 1, т.е. с выхода делителя 2, в котором происходит переустановка коэффициента деления первым импульсом с выхода делителя 2.

Счетчик адресов 14 работает как при записи в ОЗУ, так и при считывании с тактовой частотой генератора 1 за счет того, что на первом выходе элемента И 18 в режиме редецимации присутствует уровень лог. "0", который запрещает прохождение уровня лог. "1" через элемент И 18 с инверсного выхода RS-триггера 17.

Переключение RS-триггера 17 в "1" происходит после переполнений счетчика адресов 14, т. е. когда на выходе счетчика циклов 15 появляется импульс, который через ключ 16 устанавливает RS-триггер 17 в "1".

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| Устройство для регулирования массовых расходов смешиваемых продуктов | 1988 |

|

SU1695273A1 |

| УСТРОЙСТВО ОПТИМАЛЬНОЙ ОБРАБОТКИ СЛОЖНЫХ СИГНАЛОВ | 2003 |

|

RU2230426C1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2002 |

|

RU2223593C1 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1984 |

|

SU1841016A1 |

| Многоканальный программируемый генератор импульсов | 1982 |

|

SU1270879A1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| Система для программного управления | 1985 |

|

SU1251033A1 |

Устройство для преобразования М-последовательностей относится к области радиотехники и может быть использовано в системах радиосвязи и измерения дальности. Решают задачу формирования децимированных и редецимированных М-последовательностей с помощью одного устройства. Устройство содержит генератор тактовых импульсов, делитель с переменным коэффициентом деления, генератор М-последовательностей, элементы задержки, R, S-триггеры, элементы И, ИЛИ, счетчик адресов, счетчик циклов, оперативные запоминающие устройства (ОЗУ), управляемые ключи, D -триггеры, формирователь выборок ячеек ОЗУ, формирователи импульсов. 5 ил.

Устройство для преобразования М-последовательностей, содержащее генератор тактовых импульсов, выход которого соединен с тактовым входом делителя с переменным коэффициентом деления, входы установки которого соединены с выходом задатчика коэффициента деления, и генератор М-последовательностей, при этом первая n входная шина и вторая q входная шина подключены к соответствующим входам задатчика коэффициента деления, вход генератора М-последовательностей соединен с пятой входной z шиной, а вход генератора тактовых импульсов и установочный вход задатчика коэффициента деления подключены к шине "Пуск" устройства для преобразования М-последовательностей, выход делителя с переменным коэффициентом деления подключен к входу задатчика коэффициента деления, отличающееся тем, что дополнительно введены задатчик номеров циклических сдвигов, выходы которого подключены к входам установки начального состояния генератора М-последовательностей. первый элемент задержки, вход которого подключен к выходу генератора тактовых импульсов, первый элемент И, первый R-S-триггер, второй элемент И, первый управляемый ключ, первый элемент ИЛИ, второй элемент задержки, второй R-S-триггер, второй управляемый ключ, третий элемент И, счетчик адресов, входы установки модуля счета которого подключены к выходам задатчика модуля счета, счетчик циклов, установочные входы которого соединены с выходами задатчика модуля счета циклов, третий управляемый ключ, третий R-S-триггер, четвертый элемент И, пятый элемент И, шестой элемент И, третий элемент задержки, группа из n элементов И, второй элемент ИЛИ, формирователь импульсов выборки, группа из n формирователей импульсов, группа из n оперативных запоминающих устройств, группа из n D-триггеров, при этом вход задатчика номеров циклических сдвигов соединен с третьей входной шиной Х, вход задатчика модуля счета подключен к четвертой входной шине N, выход первого элемента задержки подключен к первому входу первого элемента И, второй вход которого подключен к инверсному выходу первого R-S-триггера, R-вход которого подключен к шине "Пуск", S-вход первого R-S-триггера подключен к выходу делителя с переменным коэффициентом деления и к входу второго элемента задержки, выход которого соединен с входом второго R-S-триггера, прямой выход первого R-S-триггера соединен с входом второго элемента И, второй вход которого подключен к выходу первого элемента задержки, вход второго элемента И соединен с входом первого управляемого ключа, второй вход которого подключен к выходу делителя с переменным коэффициентом деления, выход первого управляемого ключа подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу первого элемента И, а выход которого подключен к тактирующему входу генератора М-последовательностей, R-вход второго R-S-триггера подключен к выходу генератора тактовых импульсов, входу второго управляемого ключа и к входу третьего элемента задержки, второй вход второго управляемого ключа подключен к выходу делителя с переменным коэффициентом деления, выход второго управляемого ключа подсоединен к входу третьего элемента И, второй вход которого подключен к прямому выходу первого R-S-триггера, а выход третьего элемента И подключен к счетному входу счетчика адресов, вход задатчика модуля счета соединен с четвертой входной шиной N, второй вход задатчика модуля счета соединен с выходом счетчика адресов, с счетным входом счетчика циклов и с первым входом третьего управляемого ключа, второй вход которого соединен с выходом счетчика циклов и с входом переноса задатчика модуля счета счетчика циклов, установочные входы которого соединены с шиной индекса редецимации q, выход третьего управляемого ключа соединен с S-входом третьего R-S-триггера, инверсный выход которого подключен к входу четвертого элемента И, выход которого соединен с управляющим входом второго управляемого ключа, прямой выход третьего R-S-триггера подключен к входу пятого элемента И, второй вход которого подключен к второму входу шестого элемента И и к выходу третьего элемента задержки, первый вход шестого элемента И и первые входы элементов И группы из n элементов И подключены к инверсному выходу третьего R-S-триггера, третий вход шестого элемента И соединен с вторыми входами элементов И группы из n элементов И и подключен к прямому выходу второго R-S-триггера, третьи входы элементов И группы из n элементов И подключены к соответствующим n выходам генератора М-последовательностей, выходы пятого и шестого элементов И подключены к входам второго элемента ИЛИ, выход которого соединен с входом формирователя импульсов выборки, выход которого подключен к входам выборки оперативных запоминающих устройств группы из n оперативных запоминающих устройств, выходы элементов И группы из n элементов И подключены к входам соответствующих формирователей импульсов группы из n формирователей импульсов, выходы которых подключены к соответствующим информационным входам оперативных запоминающих устройств группы из n оперативных запоминающих устройств, адресные входы которых подключены к соответствующим параллельным выходам счетчика адресов, входы управления записью оперативных запоминающих устройств соединены вместе и подключены к инверсному выходу третьего R-S-триггера, выходы оперативных запоминающих устройств группы из n оперативных запоминающих устройств подключены к входам соответствующих D-триггеров группы из n D-триггеров, входы синхронизации которых соединены вместе и подключены к выходу формирователя импульсов выборки, выходы D-триггеров группы из n D-триггеров являются выходами устройства для преобразования М-последовательностей, установочный вход задатчика номеров циклических сдвигов, установочный вход задатчика модуля счета, синхронизирующий вход задатчика модуля счета счетчика циклов, R-вход первого R-S-триггера и R-вход третьего R-S-триггера соединены с шиной "Пуск" устройства для преобразования М-последовательностей, управляющий вход первого управляемого ключа соединен с управляющим входом третьего управляемого ключа и с входом четвертого элемента И и является входом управления режимом децимации или редецимации устройства преобразования М-последовательностей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сарвате Д.В., Персли М.Б | |||

| Взаимно-корреляционные свойства псевдослучайных и родственных последовательностей, - ТИИЭ Р, т.68 N 5, 1980, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Бессарабова А.А | |||

| Использование свойств М-последовательностей для повышения эффективности устройств их формирования, Техника средств связи, серия "Техника радиосвязи", N 7, 1985, с | |||

| Счетный сектор | 1919 |

|

SU107A1 |

Авторы

Даты

1998-05-27—Публикация

1994-08-01—Подача