первого и второго элементов НЕ соеди нены с первыми входами соответственно первого и второго элементов И, выходы которых соединены с единичными входами соответственно первого и второго триггеров, единичные выходы которых соединены соответственно с первьми и вторыми входами формирователей импульсов, вторые входы устано ки в О первого и второго триггеров соединены с выходом первого формирователя импульсов, вторые входы первого и второго элементов И каждого 5 узла контроля объединены с входами второго и первого элементов НЕ со- у ответственно, вторые входы первого и второго элементов И всех узлов контроля соединены попарно со всеми возможными парами выходов контролируемого блока, выходы первых и вторых формирователей импульсов узлов контроля соединены соответственно с входами шифратора и с входами второго элемента ИЛИ блока управления, выходы регистра соединены с входами блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

| Устройство для контроля интегральных схем | 1983 |

|

SU1182520A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для моделирования маршрутов сообщений и управления процессом коммутации в сети связи | 1980 |

|

SU922757A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕСТОВ ДИАГНОСТИКИ ДИСКРЕТНЫХ БЛОКОВ, содержащее блок индикации, блок формирования входных последовательностей и блок управления, причем входы блока формирования входных последовательностей соединены с входами контролируемого блока, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены шифратор, блок регистровой памяти, элемент 1 чг- n(h-1) И-НЕ, регистр и группа из узлов контроля (п - число выходов контролируемого блока), каждый из которых содержит два элемента НЕ, два элемента И, два триггера и два формирователя импульсов, блок управления содержит переключатель Режим работы, триггер, четьдзе элемента И и два элемента ИЛИ, причем нулевой и единичный входы триггера блока управления через переключатель Режим работы соединены с шиной нулевого потенциала, единичный выход триггера блока управления соединен с первьми входами первого, второго и третьего элементов И блока управления, выходы которых соединены соответственно с первым входом первого элемента ИЛИ блока управления, счетньм входом счетчика и входом сброса блока регистровой памяти, информационные входы и выходы которого соединены.соответственно с выходами и информационньд и входами счетчика, нулевой выход триггера блока управления соединен с первьм входом четвертого элемента И, выход § которого соединен с вторьм входом первого .элемента ИЛИ блока управле(Л ния, выход которого соединен с входом обращения блока регистровой памяти, второй и третий входы первого элемента И блока управления соединены соответственно с выходом второго элемента ИЛИ блока управления и выходом элемента И-НЕ, входы которого соединены с соответствующими выходами регистра, информационные входы которого соединены с выходами шифратора, вторые входы второго и четвертого элементов И блока управления объединены и являются входом синхронизации устройства, третьи входы второго и четвертого элементов И блока управления объединены и являются входом запуска устройства, второй вход третьего элемента И блока управления, установочные входы счетчика и регистра, первые входы установки в О первого и второго триггеров всех узлов контроля объединены и являются входом сброса устройства, в каадом узле контроля выходы

Изобретение относится к вычислительной технике и устройствам автоматики и может быть использовано для построения диагностических тестов дискретных схем и их диагностики.

Известны устройства, применимые для достаточно широкого класса дискретных схем (комбинационных и последовательностных), вьтолненных на базе больших ЭВМ, в которых используют алгоритмический метод построения диагностических тестов lj .

Эти устройства ориентированы на проверку схемной платы как целого и могут найти лишь ограниченное применение в производственных условиях Трудности практической реализации таких устройств вызваны высокими требованиями к уровню квалификации программистов, слишком большим объемом исходной и промежуточной информации, а также необходимостью выполнения громадного числа операций даже для сравнитеаьно небольших диск ретных схем.

Наиболее близким к предлагаемому по технической сущности является устройство для формирования тестов дискретных автоматов, содержащее индикатор тестовых наборов и блок управления, соединенный с входом коммутатора переменных логических функций, выходы которого соединены с входами коммутатора переменных элементарных конъюнкций, а также дешифратор, причем выходы коммутатора переменных элементарных конъюнкций

соединены с входами дешифратора, выходы которого соединены с индикатором тестовых наборов zl.

Недостатком известного устройства является то, что оно применимо только для комбинационных схем, а также трудоемкость получения контрольной дизъюнктивной нормальной формы (КДНФ) и ее инверсии по логической функции, реализуемой диагностируемой схемой, поскольку электронные схемы, применяемые в настоящее врется в промышленности, имеют разветвленную логическую структзгру с болыю числом входов и выходов. Не менее трудоемка механическая коммутация переменных, входящих в эти КДНФ, что приводит к большим затратш времени на формирование тестов.

Целью изобретения является повьшние быстродействия устройства.

Поставпенная цель достигается тем, что в устройство для формирования тестов диагностики дискретных блоков, содержащее блок индикации, блок формирования входных последовательностей и блок управления, причем выходы блока формирования входных последовательностей соединены со входами контролируемого блока введены шифратор, блок регистровой памяти, элемент И-НЕ, регистр и

п(п-1) группа из -г| узлов контроля

(п - число выходов контролируемого блока), каждьй из которых содержит

ва элемента НЕ, два элемента И, ва триггера и два формирователя импульсов, блок управления содержит переключатель Режим работы, триггер, четьфе элемента И и два элемен- 5 та ИЛИ, причем нулевой и единичный входы триггера блока управления через переключатель Режим работы соединен с шиной нулевого потенциала, единичный выход блока управления со- fO единен с первыми входами первого, второго и третьего элементов И блока управления, выходы которых соединены соответственно с первым входом первого элемента ИЛИ блока управления, 15 счетньм входом счетчика и входом сброса блока регистровой памяти, информационные входы и выходы которого соединены соответственно с выхоами и информационными входами счет- 20 чика, нулевой выход триггера блока управления соединен с первьм входом четвертого элемента И, выход которого соединен со вторьм входом первого элемента ИЛИ блока управления, 25 выход которого соединен со входом обращения блока регистровой памяти, второй и третий входы первого элемента И блока управления соединены соответственно с выходом второго ЗО элемента ИЛИ блока управления и выходом элемента И-НЕ, входы которого соединены с соответствующими выходами регистра, информационные входы которого соединены с вьвсодами шифра- , тора, вторые входы второго и четвертого элементов И блока управления объединены и являются входом синхронизации устройства, третьи входы второго и четвертого элементов И 0 блока управления объединены и являются входом запуска устройства, второй вход третьего элемента И блока управления, установочные входы счетчика и регистра, первые входы установки j в О первого и второго триггеров всех узлов контроля объединены и являются входом сброса устройства, в каясцом узле контроля выходы первого и второго элементов НЕ соединены с jo первьми входами сЬответственно первого и второго элементов И, выходы которых соединены с единичными входами соответственно первого и второго триггеров, единичные выходы js которых соединены соответственно с первыми и вторьв4и входами двух формирователей импульсов, вторые вхрды

установки в О первого и второго триггеров соединены с выходом первого формирователя импульсов, вторые входы первого и второго элементов И каждого узла контроля объединены со входами второго и первого элементов НЕ соответственно, вторые входы первого и второго элементов И всех узлов контроля соединены попарно со всеми возможными парами выходов контролируемого блока, выход первых и вторых формирователей импульсов узлов контроля соединены соответственно со входами шифратора и со входами второго элемента ИЛИ блока управления, выходы регистра соединены со входами блока индикации.

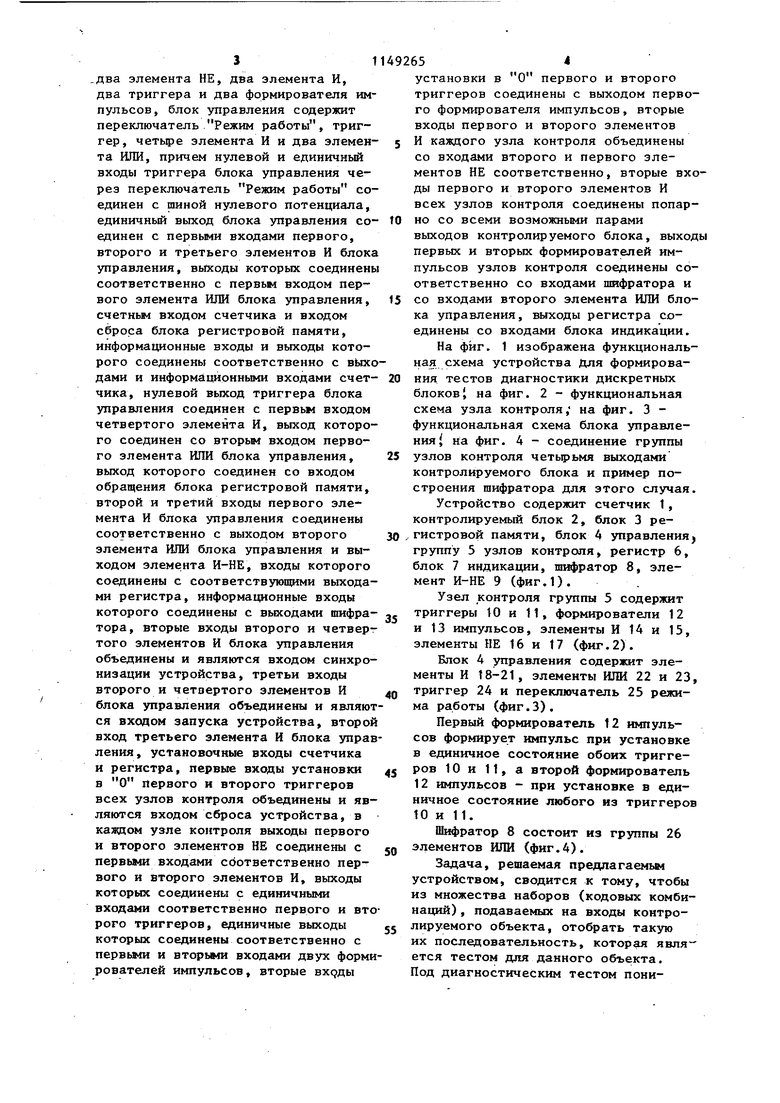

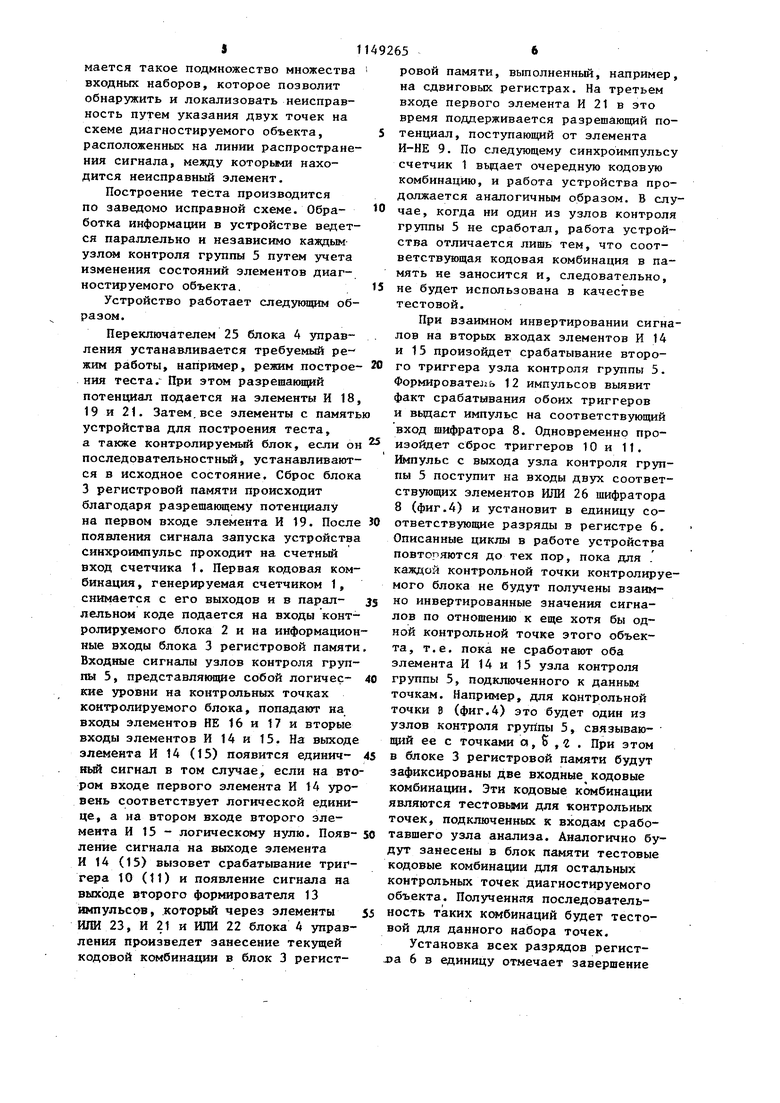

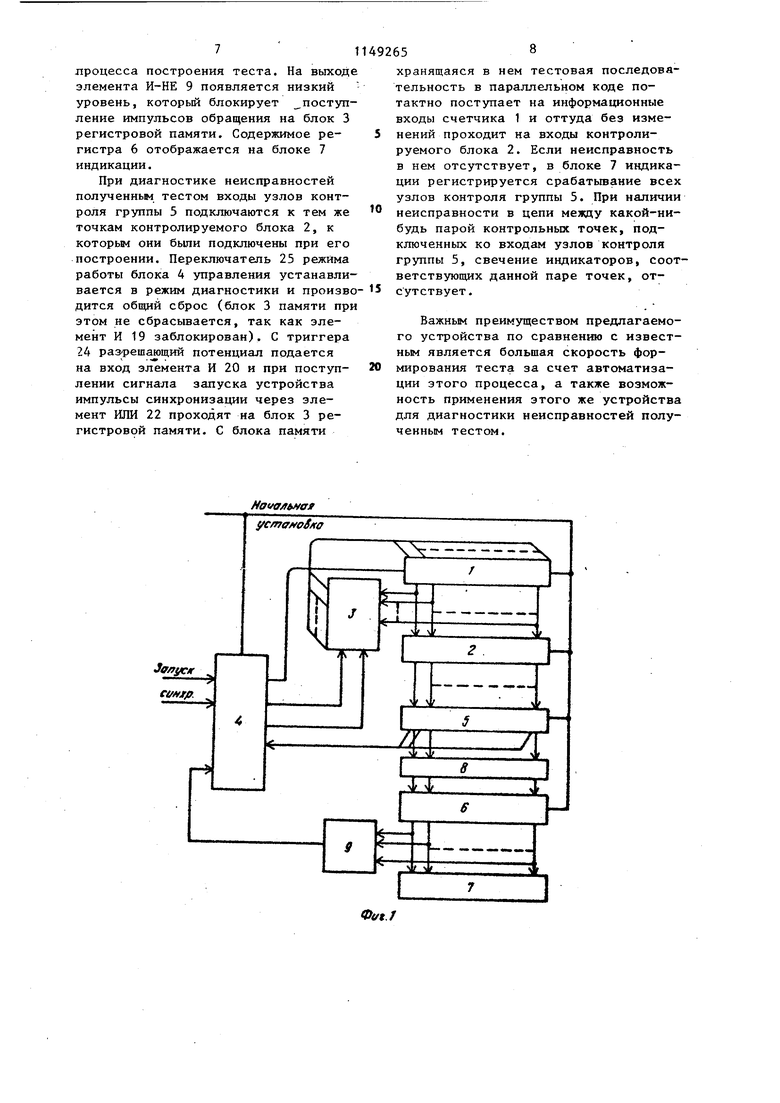

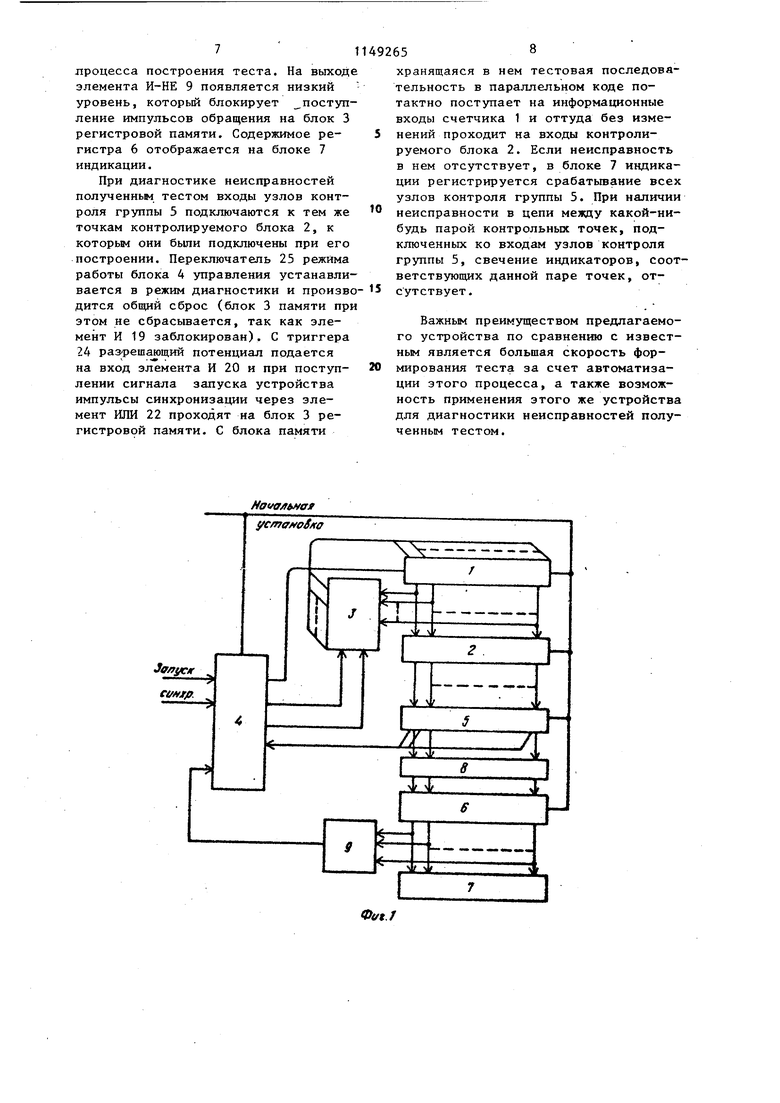

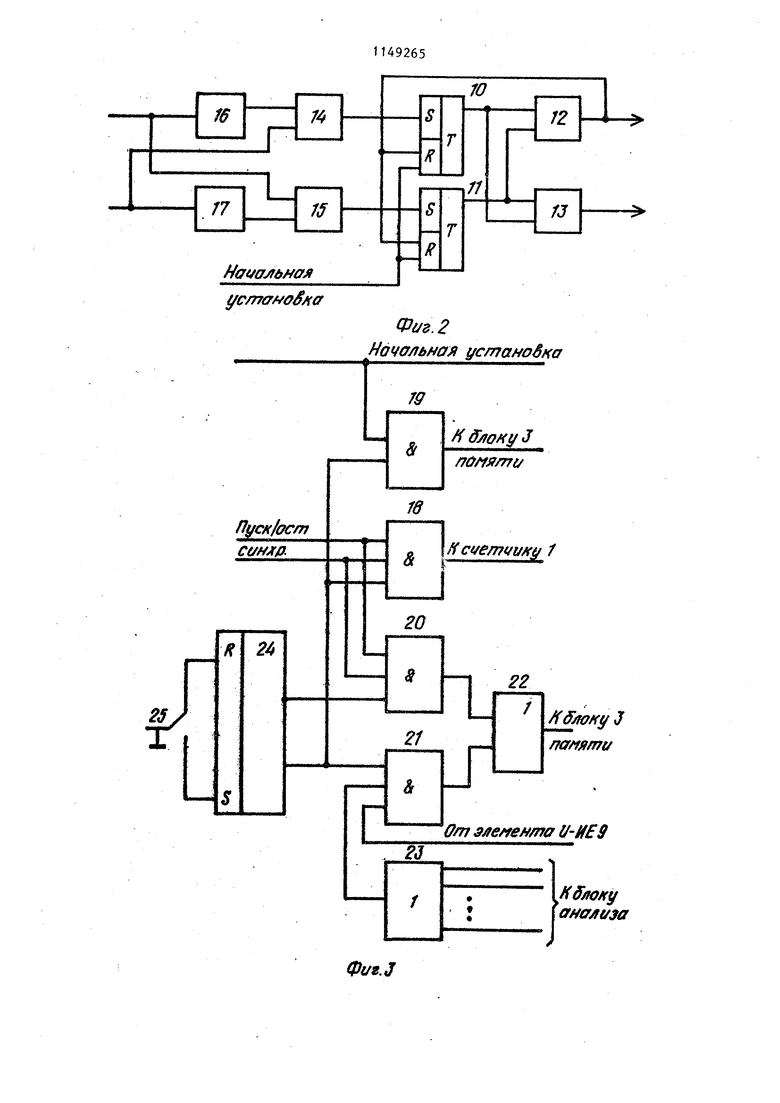

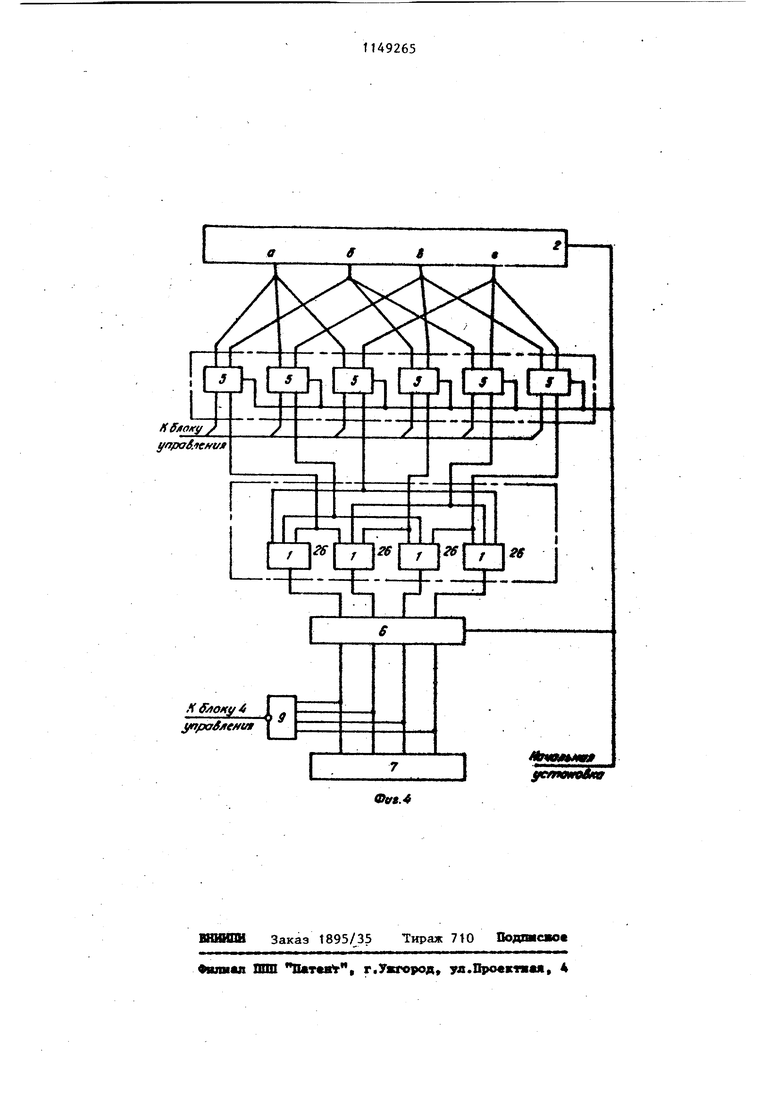

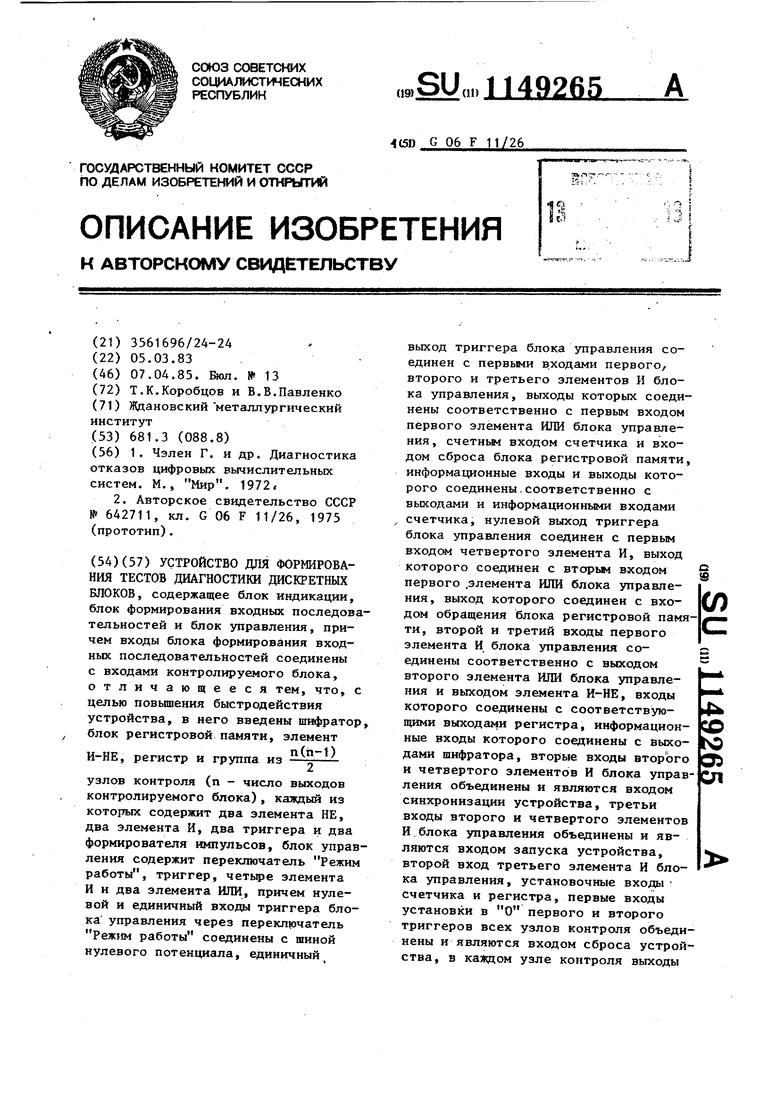

На фиг, 1 изображена функциональная схема устройства для формирования тестов диагностики дискретных блоковi на фиг. 2 - функциональная схема узла контроля, на фиг. 3 функциональная схема блока управления i на фиг. 4 - соединение группы узлов контроля четьфьмя выходами контролируемого блока и пример построения шифратора для этого случая

Устройство содержит счетчик 1, контролируемый блок 2, блок 3 регистровой памяти, блок 4 управления группу 5 узлов контроля, регистр 6, блок 7 индикации, шифратор 8, элемент И-НЕ 9 (фиг.1). .

Узел контроля группы 5 содержит триггеры 10 и 11, формирователи 12 и 13 импульсов, элементы И 14 и 15, элементы НЕ 16 и 17 (фиг.2).

Клок 4 управления содержит элементы И 18-21, элементы ИЛИ 22 и 23 триггер 24 и переключатель 25 режима работы (фиг.З).

Первый формирователь 12 импульсов формирует импульс при установке в единичное состояние обоих триггеров 10 и 11, а второй формирователь 12 импульсов - при установке в единичное состояние любого из триггеров 10 и 11.

Шифратор В состоит из группы 26 элементов ИЛИ (фиг.4).

Задача, решаемая предлагаемьв4 устройством, сводится к тому, чтобы из множества наборов (кодовых комбинаций) , подаваемых на входы контролируемого объекта, отобрать такую их последовательность, которая явля ется тестом для данного объекта. Под диагностическим тестом понимается такое подмножество множества входных наборов, которое позволит обнаружить и локализовать неисправность путем указания двух точек на схеме диагностируемого объекта, расположенных на линии распространения сигнала, между которьми находится неисправный элемент. Построение теста производится по заведомо исправной схеме. Обработка информации в устройстве ведется параллельно и независимо каждым узле контроля группы 5 путем учета изменения состояний элементов диагностируемого объекта. Устройство работает следующим образом. Переключателем 25 блока 4 управления устанавливается требуемый ре- жим работы, например, режим построения теста. При этом разрешающий потенциал подается на элементы И 18 19 и 21. Затем.все элементы с память устройства для построения теста, а также контролируемый блок, если он последовательностный, устанавливаются в исходное состояние. Сброс блока 3 регистровой памяти происходит благодаря разрешакицему потенциалу на первом входе элемента И 19. После появления сигнала запуска устройства синхроимпульс проходит на счетный вход счетчика 1. Первая кодовая комбинация, генерируемая счетчиком 1, снимается с его выходов и в параллельном коде подается на входы контролируемого блока 2 и на информацион ные входы блока 3 регистровой памяти Входные сигналы узлов контроля группы 5, представляющие собой логические уровни на контрольных точках контролируемого блока, попадают на входы элементов НЕ 16 и 17 и вторые входы элементов И 14 и 15. На: выходе элемента И 14 (15) появится единицный сигнал в том случае, если на вто ром входе первого элемента И 14 уровень соответствует логической единице, а на втором входе второго элемента И 15 - логическому нулю. Появление сигнала на выходе элемента И 14 (15) вызовет срабатьюание триггера 10 (11) и появление сигнала на выходе второго формирователя 13 импульсов, .который через элементы ИЛИ 23, И 21 и ИЛИ 22 блока 4 управления произведет занесение текущей кодовой комбинации в блок 3 регист156 ровой памяти, выполненньй, например, на сдвиговых регистрах. На третьем входе первого элемента И 21 в это время поддерживается разрешающий потенциал, поступающий от элемента И-НЕ 9. По следующему синхроимпульсу счетчик 1 вьдает очередную кодовую комбинацию, и работа устройства продолжается аналогичным образом. В случае, когда ни один из узлов контроля группы 5 не сработал, работа устройства отличается лишь тем, что соответствующая кодовая комбинация в память не заносится и, следовательно, не будет использована в качестве тестовой. При взаимном инвертировании сигналов на вторых входах элементов И 14 и 15 произойдет срабатывание второго триггера узла контроля группы 5. Формирователь 12 импульсов выявит факт срабатывания обоих триггеров и вьдает импульс на соответствующий вход шифратора 8. Одновременно произойдет сброс триггеров 10 и 11. №1пульс с выхода узла контроля группы 5 поступит на входы двух соответствующих элементов ИЛИ 26 шифратора 8 (фиг.4) и установит в единицу соответствующие разряды в регистре 6. Описанные циклы в работе устройства повторяются до тех пор, пока для . каждой контрольной точки контролируемого блока не будут получены взаимно инвертированные значения сигналов по отношению к еще хотя бы одной контрольной точке этого объекта, т.е. пока не сработают оба элемента И 14 и 15 узла контроля группы 5, подключенного к данным точкам. Например, для контрольной точки 8 (фиг.4) это будет один из узлов контроля группы 5, связывающий ее с точками а, S ,2 . При этом в блоке 3 регистровой памяти будут зафиксированы две входные кодовые комбинации. Эти кодовые комбинации являются тестовыми для контрольных точек, подключенных к входам сработавшего узла анализа. Аналогично будут занесены в блок памяти тестовые кодовые комбинации для остальных контрольных точек диагностируемого объекта. Полученная последовательность таких ксжбинаций будет тестовой для данного набора точек. Установка всех разрядов регист)а 6 в единицу отмечает завершение 71 лроцесса построения теста. На выходе элемента И-НЕ 9 появляется низкий уровень, который блокирует поступление импульсов обращения на блок 3 регистровой памяти. Содержимое регистра 6 отображается на блоке 7 индикации. При диагностике неисправностей полученньм тестом входы узлов контроля группы 5 подключаются к тем же точкам контролируемого блока 2, к KOTOpbW они были подключены при его построении. Переключатель 25 режима работы блока 4 управления устанавливается в режим диагностики и произво дится общий сброс (блок 3 памяти при этом не сбрасывается, так как элемент И 19 заблокирован). С триггера 24 раз-решающий потенциал подается на вход элемента И 20 и при поступлении сигнала запуска устройства импульсы синхронизации через элемент ИЛИ 22 проходят на блок 3 регистровой памяти. С блока памяти

Houa/fbwrf

ycmffffoi/fo

X

JffffyCJT

г

7 t

/

J 5 хранящаяся в нем тестовая последовательность в параллельном коде потактно поступает на информационные входы счетчика 1 и оттуда без изменений проходит на входы контролируемого блока 2. Если неисправность в нем отсутствует, в блоке 7 индикации регистрируется срабатывание всех узлов контроля группы 5. При наличии неисправности в цепи между какой-нибудь парой контрольньк точек, подключенных ко входам узлов контроля группы 5, свечение индикаторов, соответствующих данной паре точек, отсутствует. Важньм преимуществом предлагаемого устройства по сравнению с известным является большая скорость формирования теста за счет автоматизации этого процесса, а также возможность применения этого же устройства для диагностики неисправностей полученным тестом.

w

/

17

15

HatfajibHaJi

ycmarf oS/fff

Пуск/ост

Ct/W(0

24

К

25

г

12

/J

Фаг. 2 Иоча/1ьная усшанодка

Н ffjioHt/ J

&

/7UfiSffrft/

W

/(сг/е/ттт/1

&

гь

22

/fff/roffy 3

/rcfftamt/

От э/ге/ ен/па

/(ff/ro/fy

Фи9.3

Т I Нгг Н 1:тг

н ™ « . I л а -.1 ЖИР М I 1 мм «ММ

L L- pJ .J

in rr

yCfUWHOeftff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чэлен Г | |||

| и др | |||

| Диагностика отказов цифровых вычислительных систем | |||

| М., Мир | |||

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Устройство для формирования тестов дискретных автоматов | 1975 |

|

SU642711A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-03-05—Подача