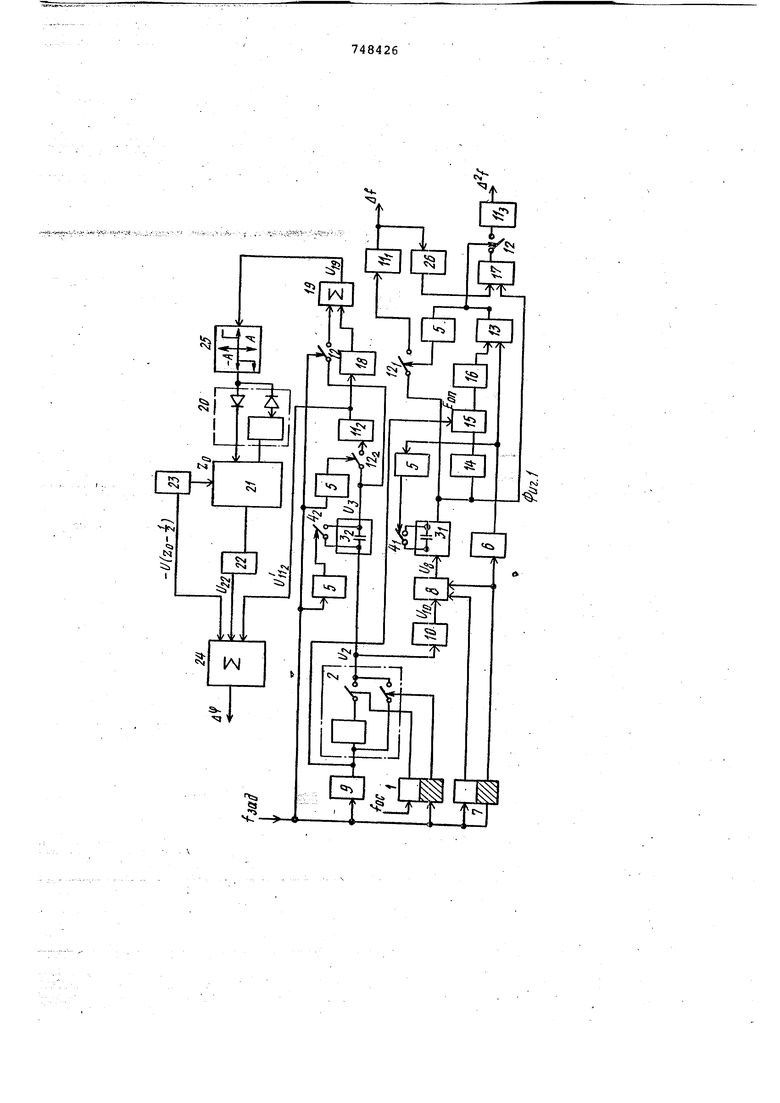

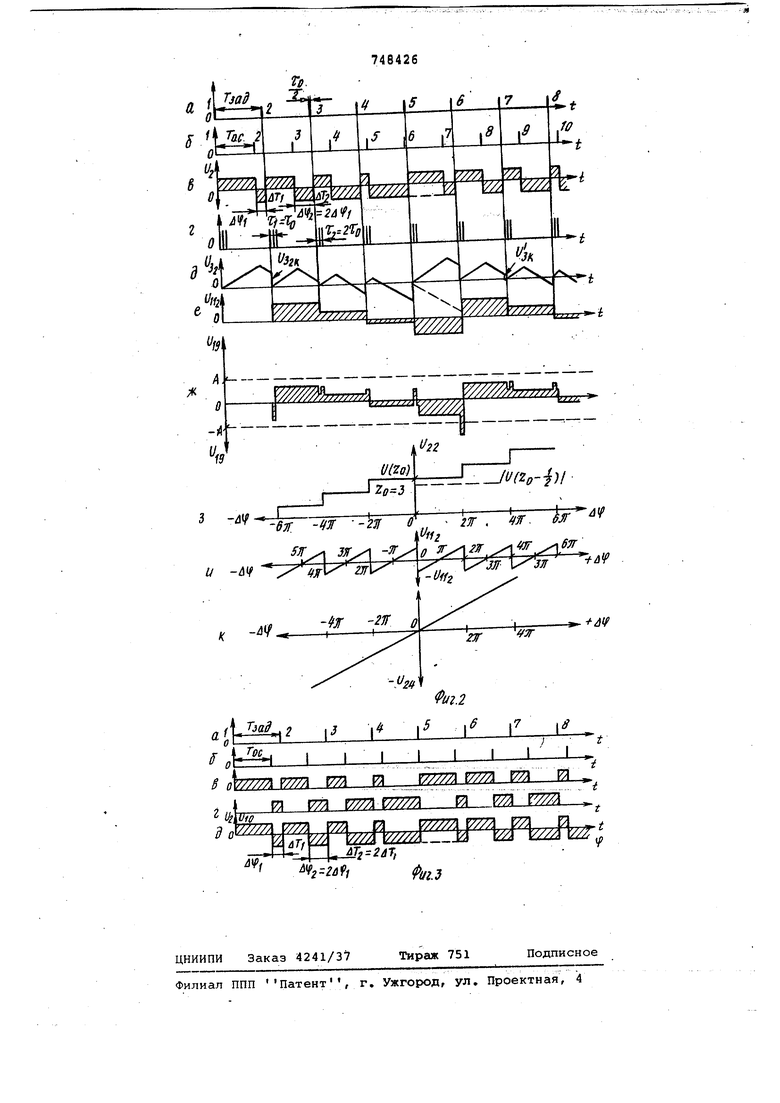

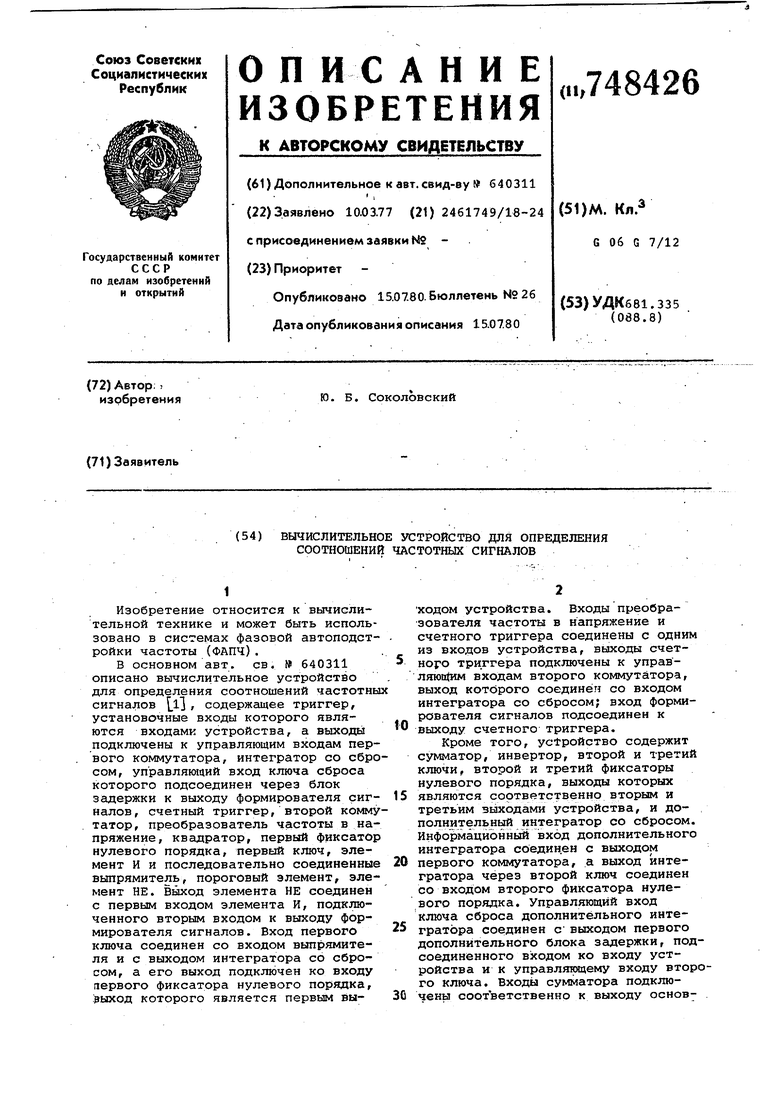

(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СООТНОШЕНИЙ ЧАСТОТНЫХ СИГНАЛОВ Изобретение относится к вычислительной технике и может быть использовано в системах фазовой автоподстройки частоты (ФАПЧ). В основном авт. св. № 640311 описано вычислительное устройство для определения соотношений частотны сигна.пов i , содержащее триггер, установочные входы которого являются входами устройства, а выходы подк.лючены к управляющим входам первого коммутатора, интегратор со сбро сом, управляющий вход к.шоча сброса которого подсоединен через блок задержки к выходу формирователя сигналов, счетный триггер, второй комму татор, преобразователь частоты в напряжение, квадратор, первый фиксатор нулевого порядка, первый ключ, элемент И и последовательно соединенные выпрямитель, пороговый элемент, элемент НЕ. Выход элемента НЕ соединен с первым входом элемента И, подключенного вторым входом к выходу формирователя сигналов. Вход первого ключа соединен со входом выпрямителя и с выходом интегратора со сбросом, а его выход подключен ко входу первого фиксатора нулевого порядка, .ыход которого является первым выХОДОМ устройства. Входы преобразователя частоты в напряжение и счетного триггера соединены с одним из входов устройства, выходы счетного триггера подключены к управляю11{им входам второго коммутатора, выход которого соединён со входом интегратора со сбросом; вход формирователя сигналов подсоединен к выходу счетного триггера. Кроме того, ус±ройство содержит cyNMaTOp, инвертор, второй и третий ключи, второй и третий фиксаторы нулевого порядка, выходы которых являются соответственно вторым и третьим выходами устройства, и дополнительный интегратор со сбросом. Информационный вход дополнительного интегратора соединен с выходом первого коммутатора, а выход интегратора через второй к.люч соединен со входом второго фиксатора нулевого порядка. Управляющий вход ключа сброса дополнительного интегратора соединен с выходом первого дополнительного блока задержки, подсоединенного входом ко входу устройства и к управляющему входу второго ключа. Входы сумматора подключены соответственно к выходу основHorb интегратора со .сбросом и через инвертор - к выходу первого фиксатора нулевого порядка, а его выход подсоединен через третий ключ ко входу третьего фиксатора нулевого порядка. Управляющий вход третьего ключа подключен к вцходу элемента И, который через второй дополнительный блок задержки подсоединен к управляющему входу первого ключа . Информационный вход и заход первого коммутатора соединены соответст венно с выходом преобразоват еЯя частоты в напряжение и со входом квадра тора, выход которого подключен к информационному входу второго коммутатора.. Недостатком прототипа является относительно низкая точность вычисле ния интегральной составляющей ошие5ки; . - Цель изобретения - повышение точности работы- устройства. . Поставленная цель достигается тем, что устройство дополнит;ёльно содержитблок выбора начальных условий и последовательно включенные первый дополнительный- сумматор, до.полнительный пороговый элемент, реле направления, реверсивный счетчик, цифроаналоговый преобразователь и второй дополнительный сумматор, выхо которого является выходом интегральной составляющей ошибки устройства, два входа первого дополнит1ельного сумматора подключены соответственно через дополнительные инвертор и ключ к выходу второго фиксатора нулевого порядка и к выходу дополнительного интегратора, цифровой выход блока выбора начальных условий подсоединен к шине установки начальных условий реверсивного счетчика, а его аналоговый выход подключен ко втором входу второго дополнительного сумматора, третий вход которого соединен с выходом второго фиксатора нулевого порядка. ..,..,.,,... -. .........--- - ----- - На фиг. 1 изображена схема устрой ства; на фиг. 2,3- временные диаграммы, поясняющие работу устройства Устройство содержит основной триггер 1, установочные входы которого является входами устройства, а выходы подключены к управляющим вХой первого коммутатора 2, основной и до полнительный интеграторы 3 , , со сбросом ключи сброса 4ц, 4, блоки зауцержки 5, формирователь сигналов б, счетный триггер 7, второй коммута тор 8, преобразователь 9 частоты в напряжение, подсоединенный к Квадратору 10 через первый коммутатор 2, фиксаторы 11 и 11/J нулевого порядк основной и дополнительный, ключи 12 12, элемент И 13 и последовательно соединенные выпрямитель 14, пороговый элемент 15 и элемент НЕ 16. Кром tofo, в состав устройства входят сум

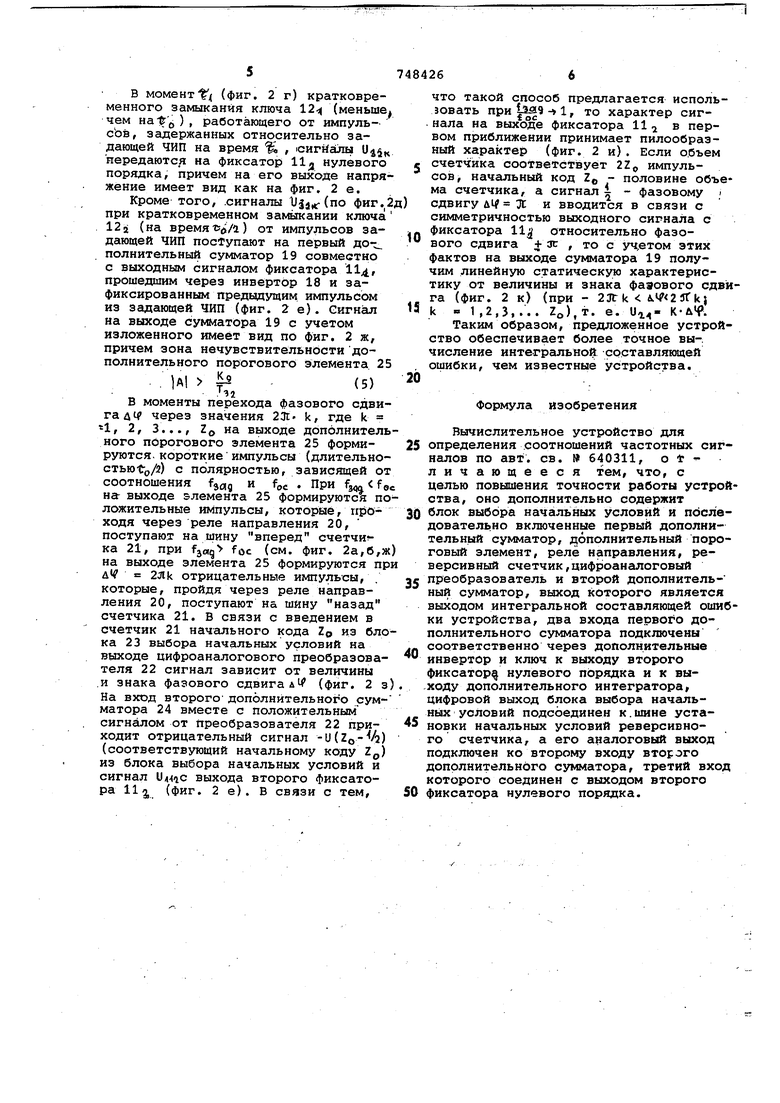

748426 матор 17, дополнительный инвертор 18, первый допблнительный сумматор 19, реле направления 20, выходы которо- . го подключены к шинам вперед и назад реверсивйргр счетчика 21, цифроайалогОвьй пре6б разоватёль 22, блок 23 выбора на чальных условий, цифровой выход которого подключен к шине установки начальных условий реверсивного счетчика, а а.налоговый выход к одному из входов второго дополнительного сумматора. 2 4. Меж,цу блоками 19 и 20 включен дополнительный пороговый элемент 25, а выход одного фиксатора 11 нулевого порядка соединен со входом суммасора 17 через инвертор 26. Устройство работает следующим образом. На преобразователь 9, один из входов триггера 1, на вход счетного триггера 7, на входы соответствующих блоков задержки 5 и управляющий вход ключа 12 поступают короткие импульсы задающей частотно-импульсной последовательности (ЧИП) с частотой fjoQ (фиг. 2 а, 3 а), на другой вход триггера 1 подается, например, ЧИП обратной связи с частотой foe |(фиг. 2 б, 3 б). При этом на выходах основного триггера получают сигналы, показанные на фиг. 3 в, г. Эти сигналы поступают к управляющим входам первого коммутатора 2. Выходной сигнал преобразователя 9 Ug (kg - коэффициент передачи преобразователя) поступает через коммутатор 2 на входы квадратора 10 и интегратора З. При этом сигнал выходе коммутатора 2 имеет вид, показаншай фиг.- 2 в, 3 Д. На выходе дополнительного интегратора Зз сигнал имеет вид как на фиг 2 д в связи с периОд:нческ1 1 замыканием ключа дброса 4 от -ттулъсбз, задержанных относительно з;адающёй ЧИП fgaqHa время 2tp, причем конечное значение интервала в конце каждого периода ч; .,f)-(v4w где Tjj -„постоянная интегрирования дополнительного интегратора. На фиг. 2 в, 3 д начальный сдвиг по фазе меаду входными ЧИП где д Т(. - начальный сдвиг между ЧИП во времени. С учетом выражения (3) Ujj npuHHMaeT в общем случае 3,к- . jf() где д f - наблюдаемая часть фазового сдвига.

В момент (фиг. 2 г) кратковременного замыкания ключа 12 (меньше чем ) , работающего от импульсЪв, задержанных относительно задающей ЧИП на время , сигйалы передаются на фиксатор нулевого порядка, причем на его выходе напряжение имеет вид как на фиг. 2 е.

Кроме того, .сигналы IJjaitr (по фиг.2д при кратковременном замыкании ключа 122 (на времяг /) от импульсов задающей ЧИП поступают на первый до-. полнительный сумматор 19 совместно с выходным сигнёшом фиксатора Ид, прошедшим через инвертор 18 и зафиксированным предьщущим импульсом из задающей ЧИП (фиг. 2 е). Сигнал на выходе сумматора 19 с учетом изложенного имеет вид по фиг. 2 ж, причем зона нечувствительности дополнительного порогового элемента 25

. |А1 - (5)

Э2.

В моменты перехода фазового сдвига дч через значения 2Л1 k, где k «1, 2, 3..., ZQ на выходе дополнительного порогового элемента 25 формируются,короткие импульсы (длительностьюСо/з) с полярностью, зависящей от соотношения fjag и . При f на- выходе злемента 25 формируются положительные импульсы, которые, проходя через реле направления 20, поступают на шину вперед счетчи ка 21, при fjotg foe (см. фиг. 2а,б,ж) на выходе элемента 25 формируются при д 2Jlk отрицательные импульсы, . которые, пройдя через реле направления 20, поступают на шину назад счетчика 21. В связи с введением в счетчик 21 начального кода Zp из блока 23 выбора начальных условий на выходе цифроаналогового преобразователя 22 сигнал зависит от величины .и знака фазового сдвига (фиг. 2 з) На вход второго дополнительного сумматора 24 вместе с положительным сигналом от преобразователя 22 приходит отрицательный сигнал -Ll() (соответствующий начальному коду 2) из блока выбора начальных условий и сигнал выхода второго фиксатора 113, (фиг. 2 е). В связи с тем,

что такой способ предлагается использовать , то характер сигнала на выходе фиксатора 11 . в первом приближении принимает пилообразный характер (фиг. 2 и). Если объем счетчика соответствует ZZ импульсов, начальный код Z,, - половине объема счетчика, а сигнал i - фазовому ; сдвигу и вводится в связи с симметричностью выходного сигнала с фиксатора 11 относительно фазового сдвига + зс , то с уч,етом этих фактов на выходе сумматора 19 получим линейную статическую характеристику от величины и знака фазового сдвига (фиг. 2 к) (при - 23tk iV 23tkj k 1 ,2,3,... ZO),T. е. К-лЧ.

Таким образом, предложенное устройство обеспечивает более точное вы-, числение интегрально составляющей ошибки, чем известные устройства.

Формула изобретения

Вычислительное устройство для определения соотношений частотных сигналов по авт. св. 640311, о t личающееся тем, что, с целью повышения точности работы устройства, оно дополнительно содержит блок выбора начальных условий и последовательно включенные первый дополнительный сумматор, дополнительный пороговый элемент, реле направления, реверсивный счетчик,цифроаналоговый преобразователь и второй дополнительный сумматор, выход которого является выходом интегральной составляющей ошибки устройства, два входа первого дополнительного сумматора подключены соответственно через дополнительные инвертор и ключ к выходу второго фиксатор нулевого порядка и к выходу дополнительного интегратора, цифровой выход блока выбора начгшьных условий подсоединен к.шине установки начальных условий реверсивного счетчика, а его аналоговый выход подключен ко второму входу второго дополнительного сумматора, третий вход которого соединен с выходом второго фиксатора нулевого порядка.

5

О

И

.

% f(.

- в

-4V

-67Г. -П --23}

-f .SW

5И -4V

(if гп

77777Л иТТЛ V/ П U7777X

ё 0

itM.

,f,

()

.-Jl fZff-i)/

ZTT . ЗГ

-.XI/T .xiP//

f

Й

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для определения соотношений между частотными сигналами | 1976 |

|

SU640311A1 |

| Устройство для определения разности частотных сигналов | 1975 |

|

SU610127A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Адаптивный регулятор тока для управляемых вентильных преобразователей | 1990 |

|

SU1786627A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для вибрационного контроля изделий | 1982 |

|

SU1073593A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ РАССЕЯНИЯ ЭНЕРГИИ И СОБСТВЕННОЙ ЧАСТОТЫ МЕХАНИЧЕСКОЙ КОЛЕБАТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2025685C1 |

| Электропривод переменного тока | 1989 |

|

SU1757041A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

Авторы

Даты

1980-07-15—Публикация

1977-03-10—Подача