(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РАЗНОСТИ ЧАСТОТНЫХ СИГНАЛОВ

Вход формирователя сигналов подсоединен к выходу счетного триггера, вход квадратора - к информационному вхолу первого коммутатора

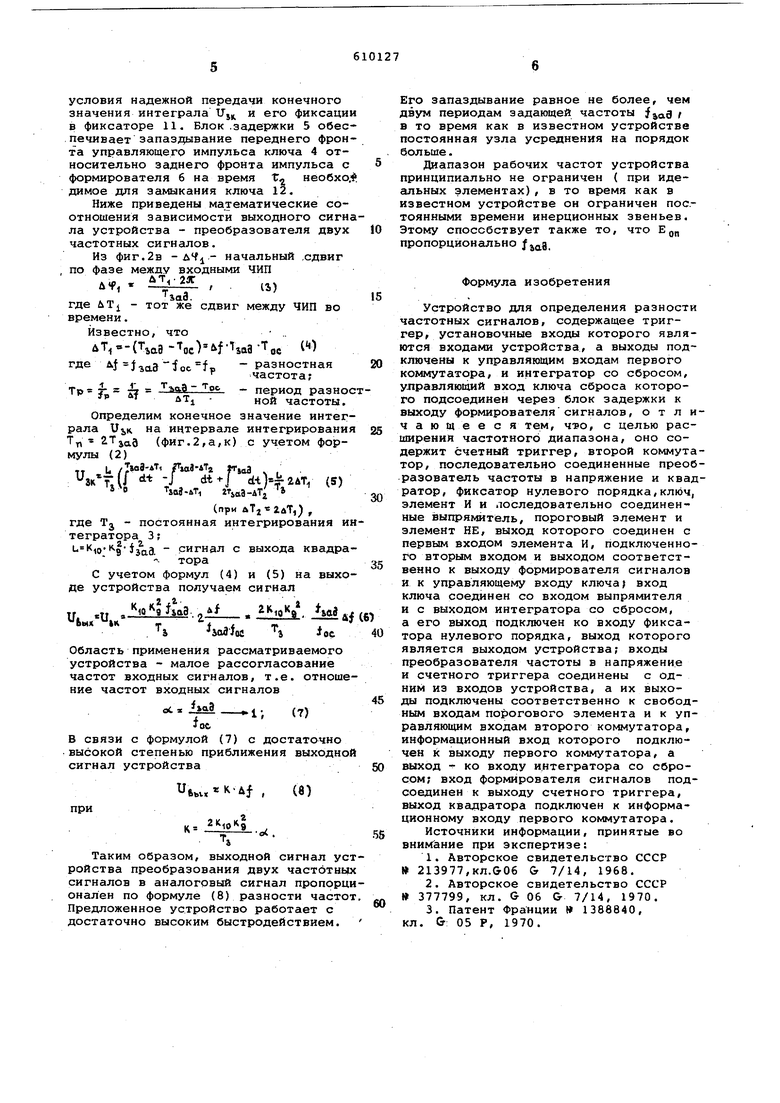

На фиг. 1 изображена принципиальная схема устройства на фиг.2 - временные диаграммы его работы„

Устройство содержит триггер 1, установочные входы которого являются .входами устройства, а выходы а , 6 подключены к управляющим входам первого коммутатора 2, интегратор со сбросом 3 управляющий вход ключа сброса 4 которого подсоединен через блок задержки 5 к выходу формирователя сигналов 6, счетный триггер 7, второй коммутатор 8, последовательно соединенные преоб«разователь.частоты в напряжение 9 и квадратор 10, фиксатор нулевого порядка 11, ключ 12, элемент И 13 и последовательно соединенные выпряг штель 14 пороговый элемент 15 и элемент НЕ 16. Выход последнего соединен с первыгл входом элемента И 13, подключенного вторым входом и выходом соответственно к выходу формирователя сигналов б и к управляющему , входу ключа 12, Вход ключа соединен со входом выпрямителя 14 и с выходом интегратора 3, а выходсо входом фиксатора .нулевого порядка 11, выход которого является выходом устройства. Входы преобразователя частоты в напряжение 9 и счетного триггера 7 соединены с одним из входов устройства, а выходы подключены соответственно к свободным ёходам порогового элемента 15 и к управляющим входам второго коммутатора 8,информационный вход которого подключен к выходу первО го коммутатора 2,а выход-ко входу интегратора со сбросом ЗоВход формирователя сигналов 6 подсоединен к выходу триггера .7,а выход квадратора 10-к информационному входу коммутатора 2.

Коммутатор 8 состоит, например, из двух цепей, работающих поочередно Причем, если первая цепь-инвертор 17 и ключ перемены знака 18, то вторая. - ключ перемены знака 19.

Устройство работает следующим образом.

На преобразователь 9, один из входов триггера 1 и триггер 7 подается задающая частотная импульсная последовательность (ЧИП) JjQ3 (фиг.2а) . На другой вход триггера 1 подается ЧИП обратной связи (фиг.26).При этом на выходах а и триггера 1 получаем сигналы (фиг,2,в,г), которые поступают к управляющим входам коммутатора 2 (аналогично коммутатору 8). Выходной сигнал преобразователя 9

9 K9-fjaB ()

поступает на квадратор 10, с выхода которого снимается сигнал

,„-кд{ д (г)

Пройдя через коммутатор 2, сигнал с квадратора 10 имеет вид, показанный на фиг,2, д (с амплитудой 1Г,о )

Одновременно на выходах аи У триггера 7 формируются послбдователь5 нести прямоугольных импульсов со

скважностью 2 (фиг,2, е,ж). Эти импульсы дают команды на поочередное замыкание ключей 18, 19 коммутатора 8. Сигнал и проходя, через коммутатор 8, преобразуется в сигнал Ug (фиг.2,з) и поступает на вход интегратора 3.

Прямоугольные импульсы с выхода i S триггера 7 (фиг.2, ж) поступают через формирователь 6 ( укорачивающий их 5 до малой длительности Г $, - , напри-, мер, на фиг.2,а по передне1 у фронту) к первому входу элем.ента И 13 и блок задержки 5 на время T.j (фиг.2,и) к цепи управления ключа сброса 4 интегратора 3, обеспечивая его периодическое кратковременное замыкание от каждого, например, нечетного импульса из задающей ЧИП . , задержанного на время Т.

в результате на выходе интегратора 3 в процессе работы устройства получаем сигнал1Г5(фиг.2к. В.;-слтучаях, когда напряжение Uj по модулюнепревышает Едп , на выходе элемента И 13. формируется импульс длительностью Гд, обеспечивающий краТ:Ковременное замыкание ключа 12.При этом проводятся замер (фиг.2 л) и фиксация конечного значения интеграла и,,,, в фиксаторе 11 (фиг. 2, м) .

Однако Б зоне фазового сдвига между ВХОДНЫМИ ЧИП

( r-gs К-0,1,2,... -п) (2) возможен кратковременный всплеск проiC

изводной

получаемой в виде конечного значения интеграла

1Г

(на4Кпример, на фиг,2, к).

Сигнал Ецп пропорционален текуще.му значению частоты fjQ.a. При этом конечное значение интеграла интегратора Ujn пропорционально разностной частоте входных ЧИП Af поэтому выбором коэффициента Х (Ео„ K.f g) определяем предельную величину ошибки if устройства независимо от текущего значения .g , меньшую всплеска производной .

В этом случае в момент прихода импульса с формирователя б сигнал с выхода выпрямителя 14 t ЕОП пороговый элемент 15 срабатывает,на его выходе появляетсй оигнал 1 , а на выходе элемента НЕ- 1-& -сигнал О , который поступает на второй вход элемента И 13. вэтом .случае на выходе элемента И 13 не формируется импульс, ключ 12 не замыкается, а на фиксаторе 11 остается ранее зафиксированный сигнал (пунктирная линия на фиг.2, м),

Необходимо отметить, что Т «i L-г:/ liпричем время Т, выбрано из условия надежной передачи конечного значения интеграла Uj и его фиксаци в фиксаторе 11. Блок .задержки 5 обес печивает запаздывание переднего фрон та управляющего импульса ключа 4 относительно заднего фронта импульса с формирователя 6 на время Т аёобхо димое для замыкания ключа 12. Ниже приведены математические соотношения зависимости выходного сигн ла устройства - преобразователя двух частотных сигналов. Из фиг.2в - начальный .сдвиг по фазе между входными ЧИП ,,, . Ill , с.) iafl. где ЛТ - тот же сдвиг между ЧИП во времени. Известно, что .. (Tjaa-V) fVa-Toc где .,-разностная частота; Тр 7- Т У период разно - ной частоты. Определим конечное значение интег рала Uj,K. на интервале интегрировани Т,, S 2Tja3 (фиг.2,а,к) с учетом формулы (2) тт Ь Twi-ATj г, . , USK-f/ dt -/ di).24T, (S) Tsaj-iT, гЧазХ (при uTj« 1лТ,) , где Tj - постоянная интегрирования и тегратора 3; ,,.. - сигнал с выхода квадра - тора С учетом формул (4) и (5) на выхо де устройства получаем сигнал и,„..и.-- billLa. ,iL. W. Ла . аiaSIoc j ioc Область применения рассматриваемого устройства - малое рассогласование частот входных сигналов, т.е. отноше ние частот входных сигналов (7) В связи с формулой (7) с достаточно высокой степенью приближения выходно сигнал устройства Uftbvxl -if , (8) Таким образом, выходной сигнал ус ройства преобразования двух частотны сигналов в аналоговый сигнал пропорц онален по формуле (8) разности часто Предложенное устройство работает с достаточно высоким быстродействием. Его запаздывание равное не более, чем двум периодам задающей частоты fjaS t в то время как в известном устройстве постоянная узла усреднения на порядок больше. Диапазон рабочих частот устройства принципиально не ограничен ( при идеальных элементах), в то время как в известном устройстве он ограничен постоянными времени инерционных звеньев. Этому способствует также то, что Ед пропорционально f . Формула изобретения Устройство для определения разности частотных сигналов, содержащее триггер, установочные входы которого являются входами устройства, а выходы подключены к управляющим входам первого коммутатора, и интегратор со сбросом, улравляющий вход ключа сброса которого подсоединен через блок задержки к выходу формирователясигналов, отличающееся тем, что, с целью расширений частотного диапазона, оно содержит счетный триггер, второй коммутатор, последовательно соединенные преобразователь частоты в напряжение и квадратор, фиксатор нулевого порядка,ключ, элемент И и лоследовательно соединенные выпрямитель, пороговый элемент и элемент НЕ, выход которого соединен с первым входом элемента И, подключенного вторым входом и выходом соответственно к выходу формирователя сигналов и к управляющему входу ключа) вход ключа соединен со входом выпрямителя и с выходом интегратора со сбросом, а его выход подключен ко входу фиксатора нулевого порядка, выход которого является выходом устройства; входы преобразователя частоты в напряжение и счетного триггера соединены с одним из входов устройства, а их выходы подключены соответственно к свободным входам порогового элемента и к управляющим входам второго коммутатора, информационный вход которого подключен к выходу первого коммутатора, а выход ко входу и.нтегратора со сбросом; вход формирователя сигналов подсоединен к выходу счетного триггера, выход квадратора подключен к информационному входу первого коммутатора. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР 213977,кЛ.&Об & 7/14, 1968. 2.Авторское свидетельство СССР 377799, кл. & 06 & 7/14, 1970. 3.Патент Франции 1388840, кл. & 05 Р, 1970.

fjod

.

и to

to

г и,

, V

ntx

//

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для определения соотношений между частотными сигналами | 1976 |

|

SU640311A1 |

| Вычислительное устройство для определения соотношений между частотными сигналами | 1977 |

|

SU748426A2 |

| Частотно-импульсное вычиттающее устройство | 1975 |

|

SU604002A1 |

| Устройство для измерения разности частот | 1980 |

|

SU997046A1 |

| Частотно-импульсное вычитающее устройство | 1977 |

|

SU646347A1 |

| Устройство для передачи и приема дискретных сигналов | 1990 |

|

SU1758894A1 |

| Частотно-импульсное вычитающее устройство | 1985 |

|

SU1309046A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для измерения температуры | 1978 |

|

SU771485A1 |

0

5

8 г

Авторы

Даты

1978-06-05—Публикация

1975-08-19—Подача