масштабный резистор - с выходом пе реключателя, соединенного входами соответственно с входом интегратора и шиной нулевого потенциала, вспомогательный усилитель, вход которого подключен к выходу операционного усилителя, а выход через ключ к корректирующему входу операционного усилителя, и блок синхронизации, соединенный с управляющими входами переключателя и ключа, введены ждущий генератор одиночных импульсов и дополнительный ключ и запоминающий конденсатор, соединенные последоватльно и включенные между корретирую цим входом операционного усилителя и шиной нулевого потенциала, причем управляющий вход дЬполнитёльного ключа через ждущий генератор одиночных импульсов соединен с выходом блока синхронизации.

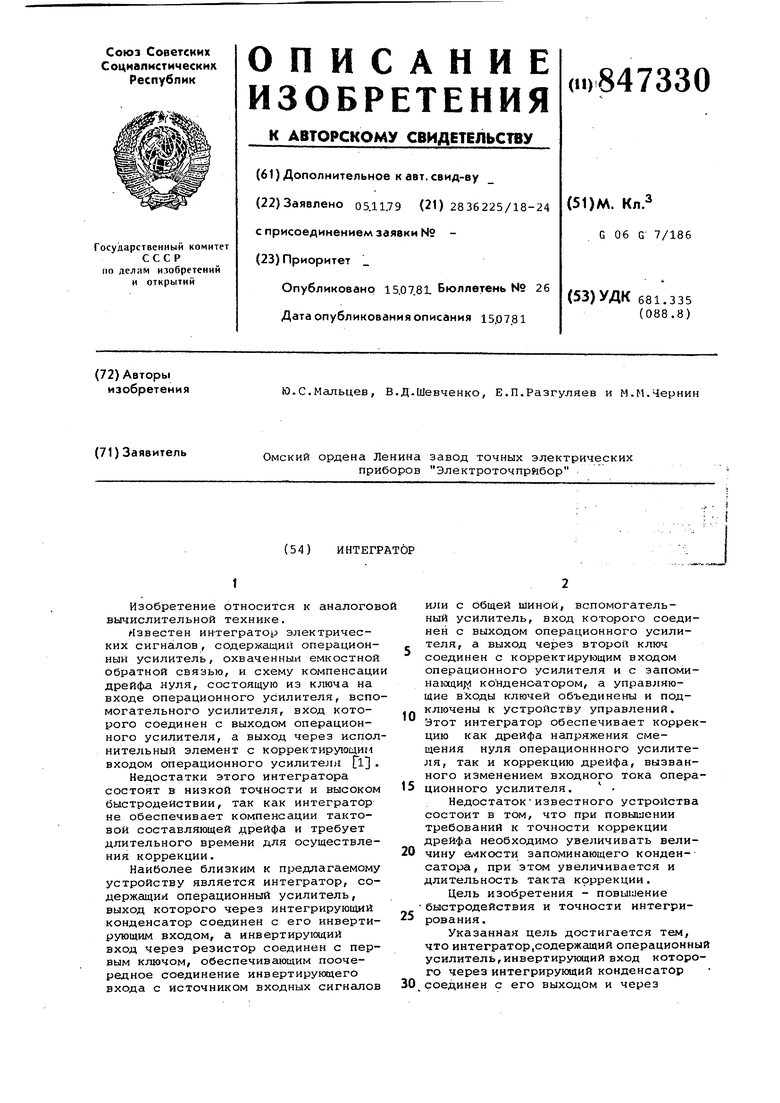

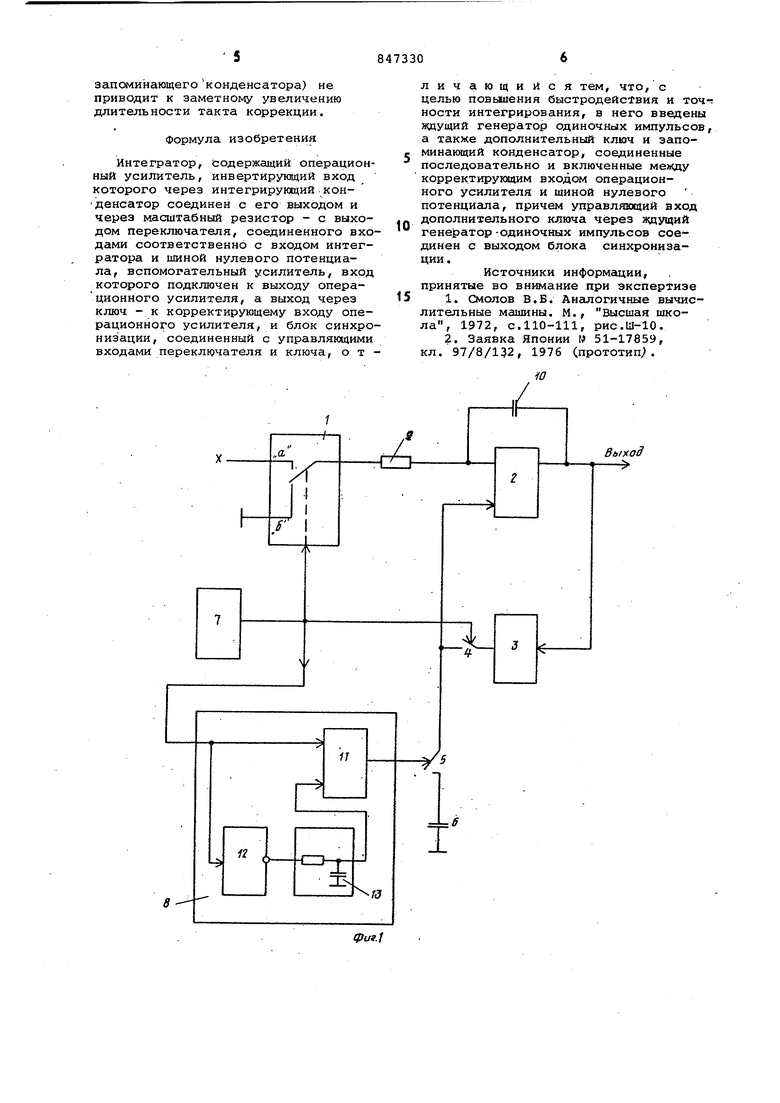

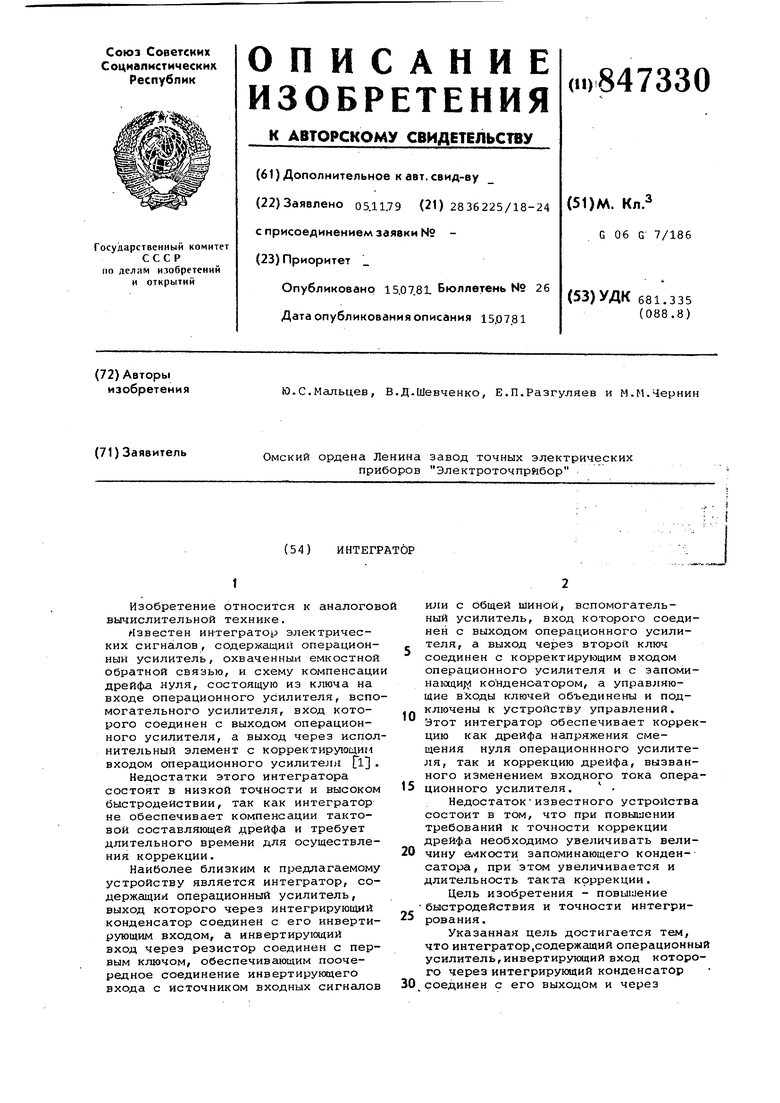

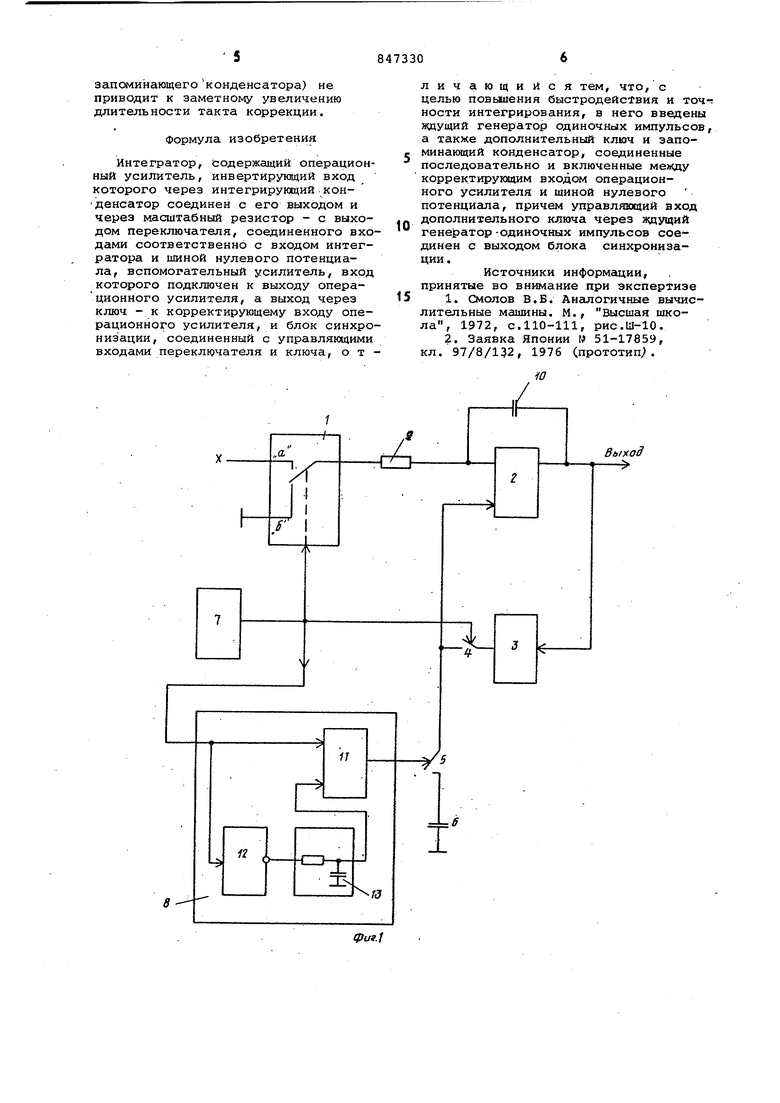

На фиг.1 показана схема предложенного интегратора на фиг.2 временная диаграмма его работы.

Интегратор содержит переключатель 1, операционный усилитель 2, вспомогательный усилитель 3, ключи 4 и 5, запоминающий конденсатор 6, блок 7 синхронизации, ждущий генератор 8 одиночных импульсов, масштабный резистор 9 и интегрирующий конденсатор 10 в цепи отрицательной обратной связи операционного усилителя 2 Выходы переключателя 1 соединены с входом интегратора и с шиной нулевого потенциала, а его выход соединен с масштабным резистором 9 операционного усилителя 2. Выход операционного усилителя 2 соединен со входом вспомогательного усилителя 3, выход которого через ключ 4 соединен с неинвертирующим входом операционного усилителя 2 и с ключом 5. Ключ 5 соединен с запоминающим конденсатором 6, вторая обкладка которого связана с шииой нулевого потенциала. Управляющие входы переклчателя 1 и ключа 4 п.сдключены к блоку 7 управления и входу ищущего генератора 8 одиночных импульсов. Выхо ждущего генератора 8 одиночных импульсов соединен с управляющим входом ключа 5.

Ждущий генератрр 8 одиночных импульсов может быть выполнен в виде элемента И 11, инвертора 12 и RCцепочки 13. Первый вход элемента И 11 является входом зедущего генератора одиночных импульсов, а выход элемента И 11 - его выходом. Вход инвертора 12 соединен с первым входом элемента И 11, а его выход со входом RC -цепочки 13, выход которой соединен со вторым входом элемента И 11.

Интегратор работает следующим образом.

В такте интегрирования переключатель 1 находится в положении

а, ключ 4 разомкнут, ключ 5 замкнут Входной сигнал поступает на операционный усилитель 2 и интегрируется. В такте коррекции блок 7 управления переводит переключатель 1 в положение б, замокает ключ 4 и одновременно через ждущий генератор 8 одиночных импульсов размыкает ключ. Выходной сигнаЛоперацио ного усилителя 2 через вспомогательнуй усилитель 3 и ключ 4 поступает на неинвертивный вход операционного усилителя 2, в результате чего на выходе вспомогательного усилител 3 устанавливается, сигнал, который отличается от нуля на величину нап.ряжения смещения нуля операционного усилителя 2 и на величину смещения этого усилителя, вызванного протеканием его входного тока через резистор 9. После этого выходным сигналом адущего генератора 8 одиночных импульсов замыкается ключ 5, напряжение на запоминающем конденсаторе 6 устанавливается равным напряжению дрейфа и это напряжение поступает на входоперационного усилителя 2, корректируя его дреИф по току и напряжению.

Преимуй1ества предложенного интегратора в сравнении с известным состоят в следующем.

В предложенном интеграторе режим коррекции разбит на два такта (введением дополнительного ключа и ждущего генератора одиночных импульсов . В течение первого такта коррекции запоминающий конденсатор отключен, поэтому длительность переходного процесса в этом такте прямо пропорциональна постоянной времени интегратора и обратно пропорциональна .коэффициенту усиления вспомогательного усилителя. После окончания переходных процессов, связанных с перезарядом интегрирующего конденсатора, начинается второй такт коррекции, в котором к выходу вспомогательного усилителя подключается запоминакнций конденсатор. Поскольку переходные процессы ужа закончились i;o, в момент включения дополнительйого ключа напряжения на выходе вспомогательного усилителя и на запоминающем конденсаторе отличаются друг от друга на весьма малую величину, обусловленную разрядом запоминающего конденсатора за время такта интегрирования, его зарядом входным током операционного усилителя в такте интегрирован и дрейфом напряжения смещения операционного усилителя. Малая разност указанных напряжений и определяет малую длительность второго такта коррекции несмотря на значительную величину емкости запоминакицего кондане атйра. Поэтому увеличение точноти коррекции (увеличение емкости запоминающегоконденсатора) не приводит к заметному увеличению длительности такта коррекции. Формула изобретения Интегратор, содержащий операционный усилитель, инвертирующий вход которого через интегрирующий конденсатор соединен с его выходом и через масштабный резистор - с выходом переключателя, соединенного вхо дами соответственно с входом интегратора и шиной нулевого потенциала, вспомогательный усилитель, вход которого подключен к выходу операционного усилителя, а выход через ключ - к корректирующему входу операционного усилителя, и блок синхро низации, соединенный с управляющими входами переключателя и ключа, о т личающийся тем, что, с целью повыиения быстродействия и точг ности интегрирования, в него введены яддущий генератор одиночных импульсов, а также дополнительный ключ и запоминающий конденсатор, соединенные последовательно и включенные между корректирующим входом операционного усилителя и шиной нулевого потенциала, причем управляющий вход дополнительного ключа через звдущий генератор-одиночных импульсов соединен с выходом блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Смолов В.Б. Аналогичные вычислительные машины. М., Высшая школа , 1972, с.110-111, рис.Ш-10. 2.Заявка Японии W 51-17859, кл. 97/8/132, 1976 (прототип;.

НлнгчЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Функциональный аналого-цифровой преобразователь | 1986 |

|

SU1310855A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

| Интегратор | 1978 |

|

SU748439A1 |

| Интегратор | 1980 |

|

SU928369A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Интегратор | 1985 |

|

SU1298775A1 |

| Интегратор с запоминанием | 1984 |

|

SU1228122A1 |

| Устройство для интегрирования сигнала | 1984 |

|

SU1201853A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

Вжо ге/fepy mofra t/x UMny/iti cof

Boixod ждуuffgff генера /пора ofuftot

/Vfr/y Uf ny/fi

cof

Ключ 5

азомкнугп фиг. г

Авторы

Даты

1981-07-15—Публикация

1979-11-05—Подача