из-за рассогласования напряжения эмит- тербаза пары транзисторов 13 и 19, 25 и 26 ДУЗ. При поступлении напряжения на селектор 7 оно сравнивается , с порогом, при превышении которого

на выходе селектора 7 появляется отрицательный импульс большой амплитуды, что соответствует единичному состоянию ячейки памяти накопителя.1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство считывания информации для доменной памяти | 1990 |

|

SU1751813A1 |

| РАДИОПЕРЕДАЮЩАЯ СИСТЕМА ВРЕМЕННОЙ ОБЛАСТИ И РАДИОПЕРЕДАТЧИК | 1989 |

|

RU2105415C1 |

| Устройство выделения -зубцов экг | 1975 |

|

SU659145A1 |

| Источник питания электрофильтра | 1983 |

|

SU1201807A1 |

| Устройство для автоматического регулирования напряжения на электрофильтре | 1976 |

|

SU752274A1 |

| Усилитель считывания | 1977 |

|

SU748505A1 |

| Устройство для считывания графической информации | 1985 |

|

SU1372343A1 |

| Импульсный вихретоковый металлоискатель | 1981 |

|

SU949600A1 |

| Устройство для электроразведки в движении | 1985 |

|

SU1242884A1 |

| Усилитель считывания | 1980 |

|

SU942136A1 |

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в магнитных ОЗУ и ПЗУ в качестве блока считывания. Цель изобретения - повышение помехоустойчивости-достигается введением компенсирующего элемента, ограничителя и интегрирующего конденсатора, а также выполнением элемента задержки регулируемым. В режиме считывания на входе 9 присутствует высокий потенциал, а на входе 10 - низкий, элемент 2 задержки работает с малым временем задержки и устройство быстро отрабатывает изменения потенциала входа 8. После окончания переходных процессов появляется низкий потенциал на входе 9 и происходит переключение времени задержки, которое приблизительно равно длительности входного сигнала. После окончания переключения времени задержки на вход 8 поступает входной сигнал отрицательной полярности малой амплитуды. Дифференциальный усилитель (ДУ) 3 усиливает разность незадержанного и задержанного сигналов. Усиленный сигнал поступает на входы элемента 5 восстановления постоянной составляющей и ограничителя 4, уровень ограничения которого выбран таким образом, чтобы полезный сигнал не ограничивался. Элемент 5 обеспечивает подавление потенциала, появляющегося из-за рассогласования напряжения эмиттербаза пары транзисторов 13 и 19, 25 и 26 ДУЗ. При поступлении напряжения на селектор 7 оно сравнивается с порогом, при превышении которого на выходе селектора 7 появляется отрицательный импульс большой амплитуды, что соответствует единичному состоянию ячейки памяти накопителя. 1 з.п. ф-лы, 2 ил.

Изобретение относится к вычисли- тельной технике, а именно к запоминающим устройствам, и может быть использовано в оперативных и постояных магнитных запоминающих устройствах в качестве блока считывания ин- формации.

Цель изобретения - повышение помехоустойчивости устройства.

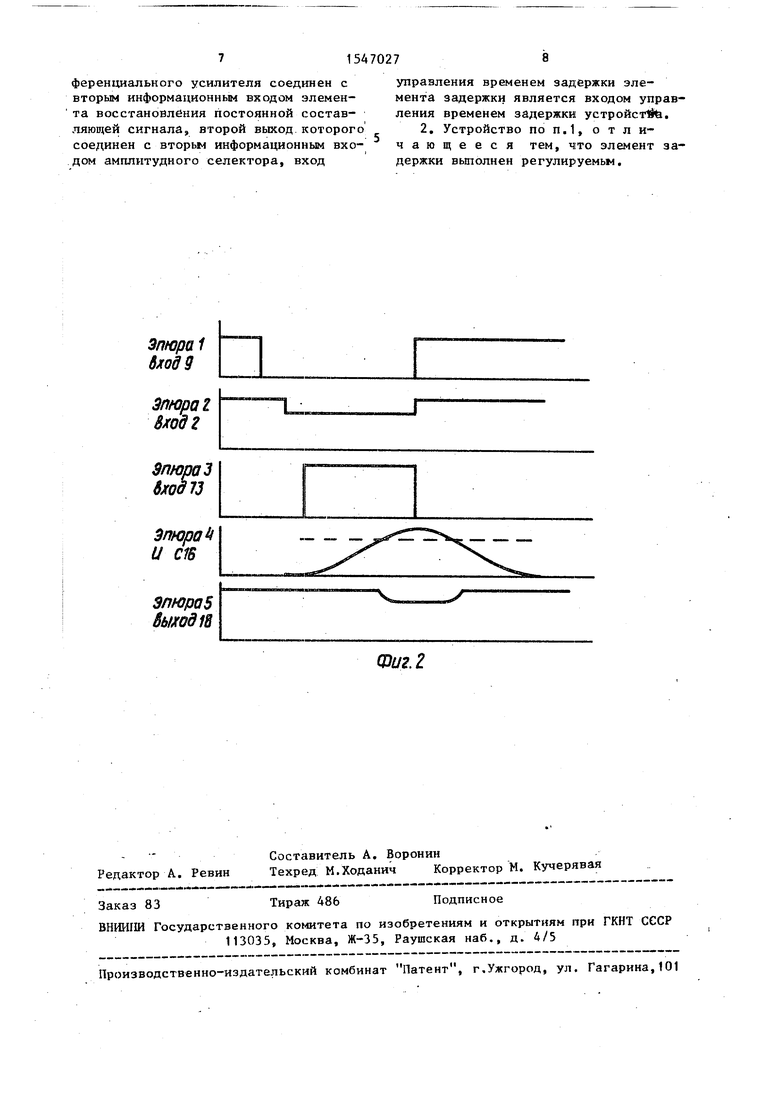

На фиг.1 изображена функциональная схема предлагаемого устройства} на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит компенсирующий элемент 1, элемент 2 задержки, дифференциальный усилитель 35 огра- ничитель 4, элемент 5 восстановления постоянной составляющей сигнала, интегрирующий конденсатор 6, амплитудный селектор 7, информационный вход 8 устройства, вход 9 управления временем задержки устройства, строби рующий вход 10 устройства, выход 11 устройства.

Компенсирующий элемент 1 выполнен в виде эмиттерного повторителя на транзисторах 12 и 13, в цепи нагрузки которого включены регулируемые источники тока на транзисторах 14-17 и ограничительном резисторе 18

Элемент 2 задержки выполнен на эмиттерном повторителе на транзистор 19, в цепь нагрузки которого включены транзистор 20, конденсатор 21, резисторы 22 и 23 и транзистор 24.

Дифференциальный усилитель 3 вы- полней на транзисторах 25 и 26, ре,- зисторах 27 и 28 и генераторе 29 тока.

Ограничитель 4 выполнен на диодах 30 и 31.

Элемент 5 восстановления постоянной составляющей сигнала выполнен на транзисторах 32-34, резисторах 35-41 и конденсаторе 42. Амплитудный селектор 7 выполнен на транзисторах 42-44, генераторах 45 и 46 тока и резисторе 47.

Устройство работает следующим образом.

Q 5

0

5 0

,

о

0

5

В начале цикла считывания происходит выбор столбца (не показано), при этом на входе 9 (эпюра 1 на фиг.2) появляется высокий потенциал, а на входе 10 (эпюра 3 на фиг.2) - низкий потенциал. Элемент 2 задержки работает с малым временем задержки и устройство быстро отрабатывает изменения потенциала входа 8. После окончания переходных процессов появляется низкий потенциал на входе 9 (эпюра 1 на фиг.2) и происходит переключение времени задержки. Принцип изменения времени задержки и работы компенсирующего элемента 1 следующий. При появлении низкого потенциала на входе 9 (эпюра 1 на фиг.2) транзистор 24 переходит в режим отсечки. Ток источников тока на транзисторах ,15 и 20 резко падает до меньшего значения, определяемого резистором 23. Постоянная времени разряда конденсатора 21 значительно увеличивается, что и определяет время задержки на транзисторах 19 и 20 для отрицательных импульсов. Время задержки элемента 2 приблизительно равно длительности входного сигнала. При изменении тока источников на транзисторах 15 и 20 напряжения на входах дифференциального усилителя 3 изменяются на одинаковую величину, равную изменению напряжения на эмиттер-база транзисторов 1J и 19. Небольшая задержка повышения напряжения на входе дифференциального усилителя 3 обусловлена быстродействием транзистора 13. Этот короткий импульс дифференциального напряжения на входах дифференциального усилителя 3 устраняется некоторой задержкой прихода входного сигнала относительно момента переключения времени задержки. При изменении тока через транзисторы 13 и 19 изменяется ток базы этих транзисторов, что может привести к изменению потенциала на входе. Лля устранения влияния изменения тока базы транзисторов 13 и 19 производят компенсацию этого изменения путем пропорционального увеличения тока коллектора транзистора 14, После окончания переключения времени задержки на вход 8 поступает входной сигнал отрицательной полярности малой амплитуды (эпюра 2 на фиг.2). На один из входов дифференциального усилителя 3 проходит незадержанный сигнал с компенсирующего элемента 1 , а на другой вход дифференциального усилителя 3 поступает задержанный сигнал с элемента 2 задержки. Дифференциальный усилитель 3 усиливает разность незадержанного и задержанного сигналов. Усиленный сигнал с дифференциального усилителя 3 поступает на вход элемента 5 восстановления постоянной составляющей сигнала и ограничителя 4. Уровень ограничения выбран таким, что полезный сигнал не ограничивается, а шумы и помехи высокой частоты ограничиваются до уровня полезного сигнала. Элемент 5 обеспечивает подавление потенциала, появляющегося из-за рассогласования напряжения эмиттер-база пары транзисторов 13 и 19 и транзисторов 25 и 26 дифференциального усилителя 3, а также температурного дрейфа этих напряжений. На вход 10 поступает сигнал строба, который приходит с некоторым запаздыванием относительно входного сигнала (эпюра 3 на фиг.2). На элементе 5 происходит дальнейшее усиление

сигнала для обеспечения работы амплитудного селектора 7. Коэффициент усиления элемента 5 зависит от амплитуды сигнала строба на входе 10. С приходом строба на вход 10 при наличии входного сигнала начинается заряд интегрирующего конденсатора 6 (эпюра 4 на фиг.2,). Интегрирующий конденсатор 6 обеспечивает фильтрацию ограниченных высокочастотных шумов и помех. Линейно нарастающее напряжение между входами амплитудного селектора 7 сравнивается с порогом. При превышении порога на выходе 11 амплитудного селектора 7 появляется отрицательный импульс большой амплитуды (эпюра 5 на фиг.2), что соответствует единичному состоянию ячейки накопителя (не показано). После окончания импульса строба на входе

10 происходит разряд интегрирующего конденсатора 6. При появлении высокого потенциала на входе 9 происходит переключение элемента 2 задержки на

5

0

работу с мальм временем задержки. Порог амплитудного селектора 7 зависит от коэффициента усиления элемента 5, так как коэффициент усиления элемента 5 регулируется амплитудой импульса на входе 10.

Таким образом, введение в устройство считывания информации компенсирующего элемента, ограничителя, интегрирующего конденсатора и выполнение элемента задержки регулируемым позволяет за счет повышения быстродействия входных цепей и накопления заряда на интегрирующем конденсаторе повысить устойчивость устройства к помехам и шумам высокой частоты, что дает возможность использовать одну схему с несколькими переключаемыми столбцами, так как значительно ускоряются переходные процессы при переключении столбцов накопителя информации.

25 Формула изобретения

5

0

5

0

5

ференциального усилителя соединен с вторым информационным входом элемента восстановления постоянной составляющей сигнала, второй выход которого соединен с вторым информационным входом амплитудного селектора, вход

Эпюра 1 6А од9

Эпюраl Вход 2

Эпюра 3 дхоё73

Эпюров U C1S

эпюров Выходя

управления временем задержки элемента задержки является входом управления временем задержки устройств.

Фиг. 2

| Hunter P.E | |||

| Test results anan experimental crosstic random access memory /GRAM/ | |||

| - IEEE Transactions on magnetics Vol | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-02-28—Публикация

1988-06-27—Подача