: I

Изобретение относится к области вычислительной техники и может быть использовано в системах контро.ля вычислительных устройств. 5

Известно устройство для обнаружения потери импульса, содержащее -квазиселекторы, триггер, элементы И, элемент НЕ и элемент ИЛИ f17 .

Недостатком известного устройства ю является низкая достоверность контроля.

Наиболее близким техническим решением к изобретению является устройство для контроля последовательности j импульсов, содержащее счетный триггер, элементы И, элемент ИЛИ-НЕ и ждущие мультивибраторы 2 .

Недостатком такого устройства является отсутствие возможности контро-2о ля увеличения частоты импульсов во входной импульсной последовательности.

Целью изобретения является расширение функциональных возможностей 25 устройства для контроля последовательности импульсов.

Цель достигается тем, что в устройство для контроля последователь,ности импульсов, содержащее элемент JQ

ИЛИ, элемент задержки и счетный триггер, едини йый и нулевой выходы которого подключены к первым входам соответственно первого и второго элементов и, а счетный вход подк.гпочен к входной шине, введен дополнительный счетный триггер, нулевой и единичный выходы которого подключены к вторым входам соответственно первого и второго Элементов И, при этом третьи входы последних подключены к выходу элемента задержки и к счетному входу дополнительного счетного триггера, единичный вход счетного триггера соединен с нулевым входом дополнительного счетного триггера и с шиной начальной установки выходы первого и второго элементов И соединены с входами элемента Или, вход элемента задержки соединен с входной шиной.

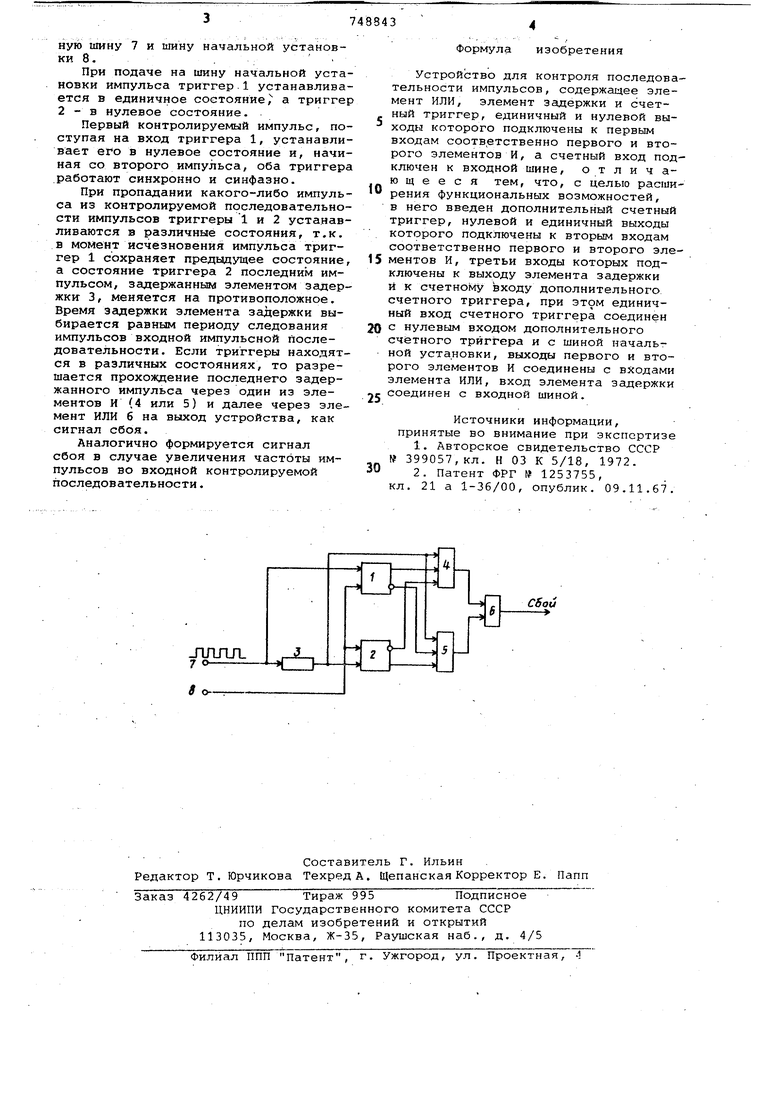

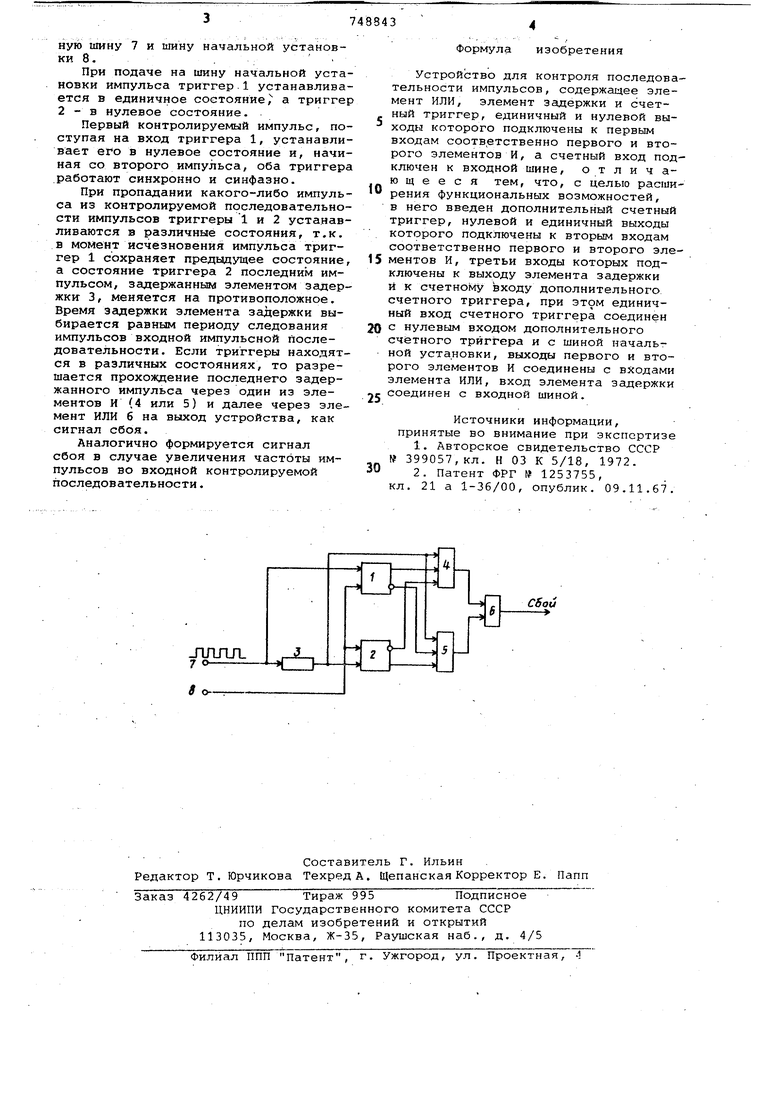

На чертеже представлена принципи- . альная электрическая схема устройства для контроля последовательности им- . пульсов.

Устройство для контроля пос.ледовательности импульсов содержит счетные триггеры 1 и 2, элемент задержки 3, элементы И 4-5, элемент ИЛИ 6, входную шину 7 и шину начальной установки 8 ..

При подаче на шину начальной установки импульса триггер 1 устанавливается в единичное состояние а триггер 2 - в нулевое состояние.

Первый контролируемый импульс, поступая на вход триггера 1, устанавливает его в нулевое состояние и, начиная со второго импульса, оба триггера работают синхронно и синфазно.

При пропадании какого-либо импульса из контролируемой последовательности импульсов триггеры 1 и 2 устанавливаются в различные состояния, т.к. в момент исчезновения импульса триггер 1 сохраняет предыдущее состояние, а состояние триггера 2 последним импульсом, задержанным элементом задержки 3, меняется на противоположное. Время задержки элемента задержки выбирается равным периоду следования импульсов входной импульсной последовательности. Если триггеры находятся в различных состояниях, то разрешается прохождение последнего задержанного импульса через один из элементов И (4 или 5) и далее через элемент ИЛИ б на выход устройства, как сигнал сбоя.

Аналогично формируется сигнал сбоя в случае увеличения частоты импульсов во входной контролируемой последовательности.

Формула изобретения

Устройство для контроля последовательности импульсов, содержащее элемент ИЛИ, элемент задержки и счетный триггер, единичный и нулевой выходы которого подключены к первым входам соотв,етственно первого и второго элементов И, а счетный вход подключен к входной шине, отличающееся тем, что, с целью расширения функциональных возможностей, в него введен дополнительный счетный триггер, нулевой и единичный выходы которого подключены к вторым входам соответственно первого и второго элементов И, третьи входы которых подключены к выходу элемента задержки и к счетному Ьходу дополнительного счетного триггера, при этом единичный вход счетного триггера соединен

0 с нулевым входом дополнительного счётного триггера и с шиной начальной установки, выходы первого и второго элементов И соединены с входами элемента ИЛИ, вход элемента задержки соединен с входной шиной.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 399057, кл. Н 03 К 5/18, 1972.

2.Патент ФРГ № 1253755,

кл. 21 а 1-36/00, опублик. 09.11.67.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности импульсов | 1983 |

|

SU1177899A1 |

| Устройство для контроля информации по модулю три | 1988 |

|

SU1580369A1 |

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

| Устройство контроля цифровых блоков | 1985 |

|

SU1339567A1 |

| Устройство для задержки импульсов | 1988 |

|

SU1713093A1 |

| Устройство для контроля цифровых последовательностей | 1988 |

|

SU1603388A1 |

| Устройство для контроля последовательности импульсов | 1981 |

|

SU957425A1 |

| Селектор импульсов по длительности | 1980 |

|

SU917331A2 |

| Устройство для допускового контроля частоты следования импульсов | 1982 |

|

SU1034165A1 |

| Устройство для контроля -разряд-НОгО СчЕТчиКА | 1979 |

|

SU839060A1 |

Авторы

Даты

1980-07-15—Публикация

1975-11-14—Подача