Изобретение относится к вычислительной технике и может быть использовано при разработке устройств автономного и встроенного контроля цифровых узлов.

Цель изобретения - повьпиение достоверности контроля.

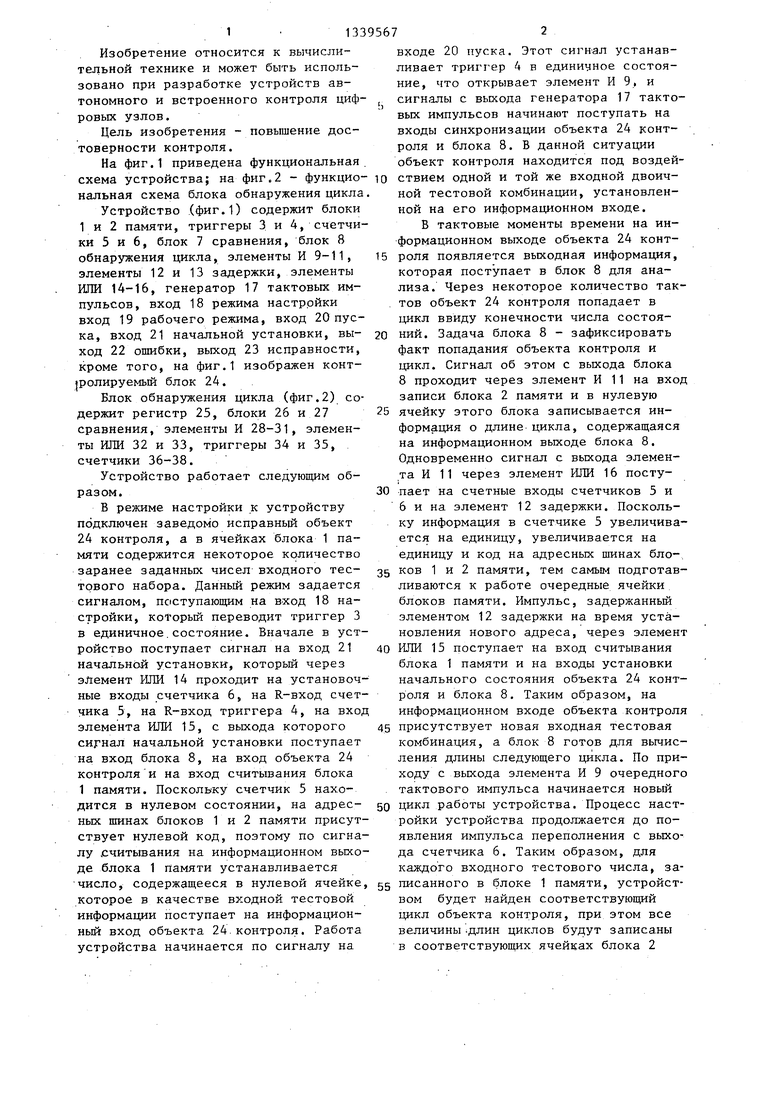

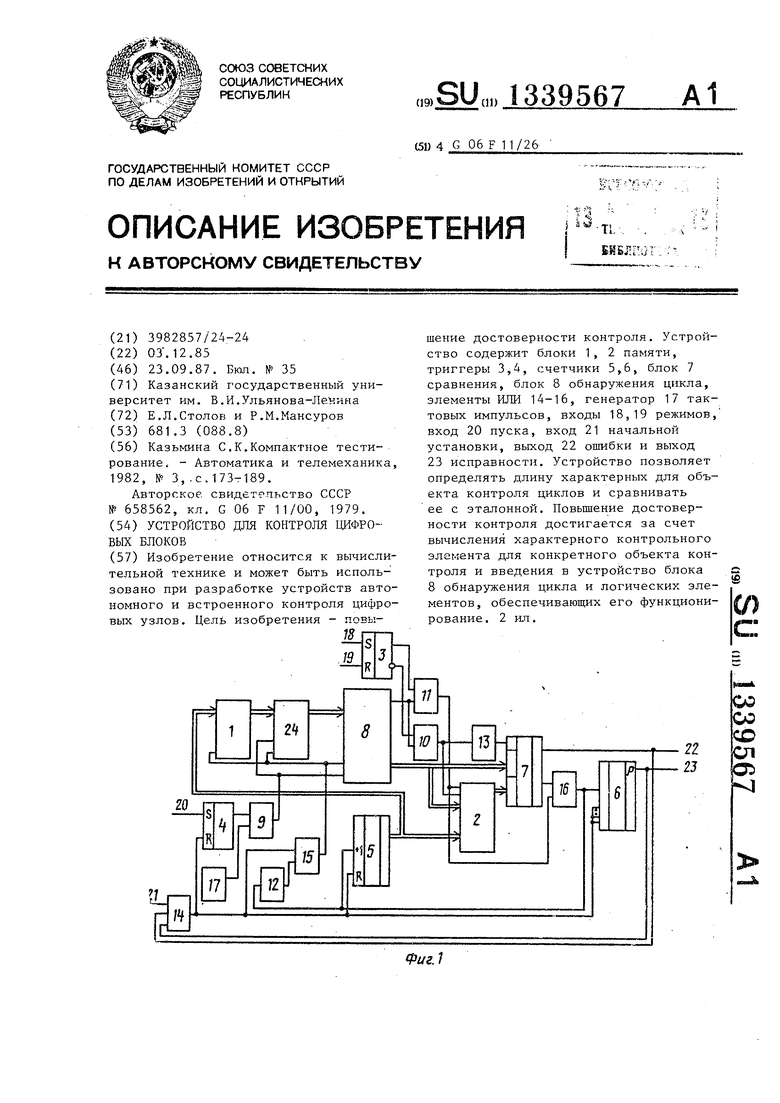

На фиг.1 приведена функциональная.

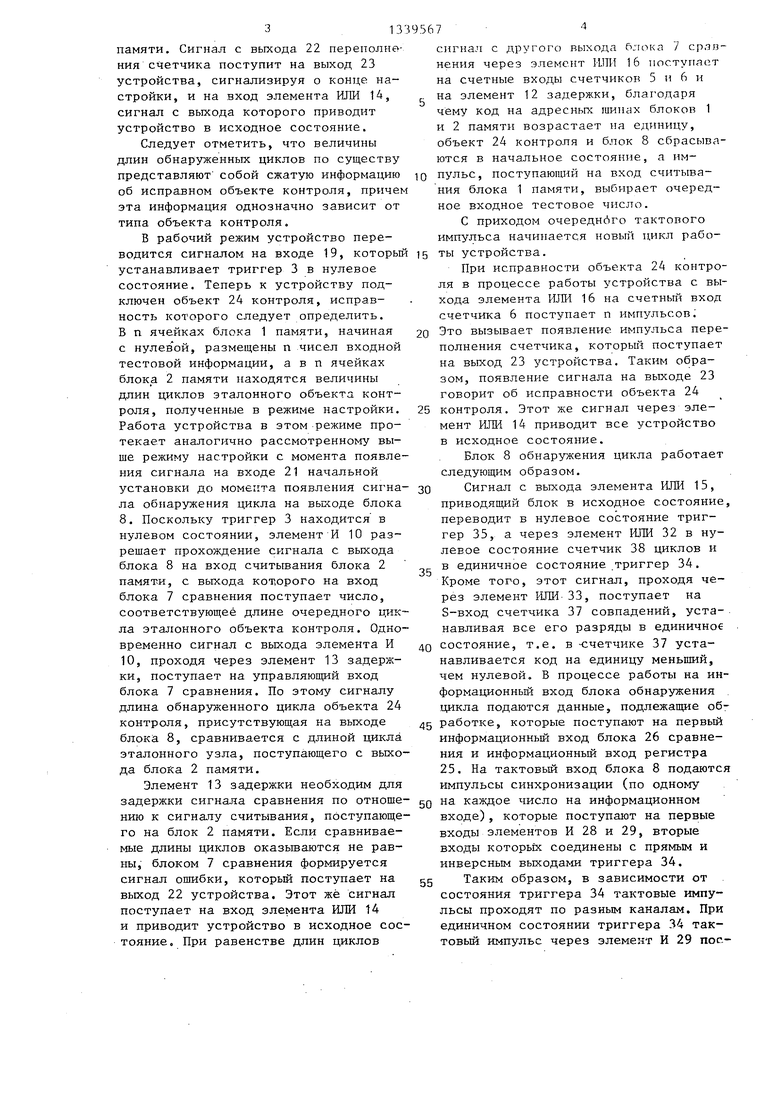

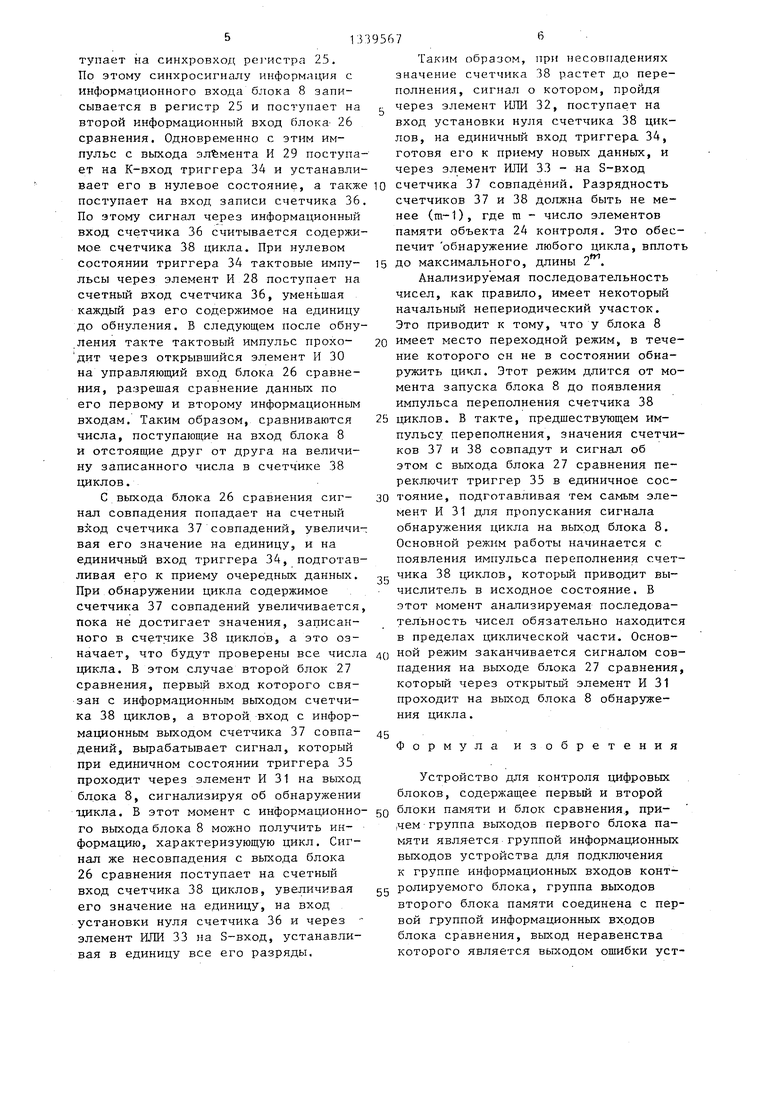

схема устройства; на фиг,2 - функцио- ю ствием одной и той же входной двоичнальная схема блока обнаружения цикла

Устройство (фиг.1) содержит блоки 1 и 2 памяти, триггеры 3 и 4, счетчики 5 и 6, блок 7 сравнения, блок 8 обнаружения цикла, элементы И 9-11, элементы 12 и 13 задержки, элементы ШШ 14-16, генератор 17 тактовых импульсов, вход 18 режима настройки вход 19 рабочего режима, вход 20 пуска, вход 21 начальной установки, выход 22 ошибки, выход 23 исправности, кроме того, на фиг.1 изображен конт- |ролируемый блок 24.

Блок обнаружения цикла (фиг.2) содержит регистр 25, блоки 26 и 27 сравнения, элементы И 28-31, элементы ИЛИ 32 и 33, триггеры 34 и 35, счетчики 36-38.

Устройство работает следующим образом.

В режиме настройки к устройству подключен заведомо исправный объект 24 контроля, а в ячейках блока 1 памяти содержится некоторое количество заранее заданных чисел входного тестового набора. Данный режим задается сигналом, поступающим на вход 18 настройки, который переводит триггер 3 в единичное.состояние. Вначале в устройство поступает сигнал на вход 21 началънЬ-й установки, который через элемент ИЛИ 14 проходит на установочные входы счетчика 6, на R-вход счетчика 5, на R-вход триггера 4, на вход элемента ИЛИ 15, с выхода которого сигнал начальной установки поступает на вход блока 8, на вход объекта 24 контроля и на вход считывания блока 1 памяти. Поскольку счетчик 5 находится в нулевом состоянии, на адресных шинах блоков 1 и 2 памяти присутствует нулевой код, поэтому по сигналу считывания на информационном выходе блока 1 памяти устанавливается

число, содержащееся в нулевой ячейке, 55 писанного в блоке 1 памяти, устройст- которое в качестве входной тестовой вом будет найден соответствующий информации поступает на информацион- цикл объекта контроля, при этом все ный вход объекта 24.контроля. Работа величины-длин циклов будут записаны устройства начинается по сигналу на в соответствующих ячейках блока 2

входе 20 пуска. Этот сигн-ал устанавливает триггер 4 в единичное состояние, что открывает элемент И 9, и сигналы с выхода генератора 17 тактовых импульсов начинают поступать на входы синхронизации объекта 24 контроля и блока 8. В данной ситуации объект контроля находится под воздейной тестовой комбинации, установленной на его информационном входе.

В тактовые моменты времени на информационном выходе объекта 24 контроля появляется выходная информация, которая поступает в блок 8 для анализа. Через некоторое количество тактов объект 24 контроля попадает в цккл ввиду конечности числа состояНИИ. Задача блока 8 - зафиксировать факт попадания объекта контроля и цикл. Сигнал об этом с выхода блока 8 проходит через элемент И 11 на вход записи блока 2 памяти и в нулевую

ячейку этого блока записывается информация о длине цикла, содержащаяся на информационном выходе блока 8. Одновременно сигнал с выхода элемента И 11 через элемент ШШ 16 поступает на счетные входы счетчиков 5 и 6 и на элемент 12 задержки. Поскольку информация в счетчике 5 увеличивается на единицу, увеличивается на единицу и код на адресных шинах бло-,

ков 1 и 2 памяти, тем самым подготавливаются к работе очередные ячейки блоков памяти. Импульс, задержанный элементом 12 задержки на время установления нового адреса, через элемент

ИЛИ 15 поступает на вход считывания блока 1 памяти и на входы установки начального состояния объекта 24 контроля и блока 8. Таким образом, на информационном входе объекта контроля

присутствует новая входная тестовая комбинация, а блок 8 готов для вычисления длины следующего цикла. По приходу с выхода элемента И 9 очередного тактового импульса начинается новый

цикл работы устройства. Процесс настройки устройства продолжается до появления импульса переполнения с выхоа счетчика 6. Таким образом, для каждого входного тестового числа, за

памяти. Сигнал с выхода 22 переполнения счетчика поступит на выход 23 устройства, сигнализируя о конце настройки, и на вход элемента ИЛИ 14, сигнал с выхода которого приводит устройство в исходное состояние.

Следует отметить, что величины длин обнаруженных циклов по существу представляют собой сжатую информацию об исправном объекте контроля, причем эта информация однозначно зависит от типа объекта контроля.

В рабочий режим устройство переводится сигналом на входе 19, который устанавливает триггер 3 в нулевое состояние. Теперь к устройству подключен объект 24 контроля, исправность которого следует определить. В п ячейках блока 1 памяти, начиная с нулев ой, размещены п чисел входной тестовой информации, а в п ячейках блока 2 памяти находятся величины длин циклов эталонного объекта контроля, полученные в режиме настройки. Работа устройства в этом режиме протекает аналогично рассмотренному выше режиму настройки с момента появления сигнала на входе 21 начальной установки до момента появления сигнала обнаружения цикла на выходе блока 8. Поскольку триггер 3 находится в нулевом состоянии, элемент И 10 разрешает прохождение сигнала с выхода блока 8 на вход считывания блока 2 памяти, с выхода которого на вход блока 7 сравнения поступает число, соответствующее длине очередного цикла эталонного объекта контроля. Одновременно сигнал с выхода элемента И 10, проходя через элемент 13 задержки, поступает на управляюш;ий вход блока 7 сравнения. По этому сигналу длина обнаруженного цикла объекта 24 контроля, присутствующая на выходе блока 8, сравнивается с длиной цикла эталонного узла, поступающего с выхода блока 2 памяти.

Элемент 13 задержки необходим для задержки сигнала сравнения по отношению к сигна.пу считывания, поступающего на блок 2 памяти. Если сравниваемые длины циклов оказьгоаются не рав

ны, блоком 7 сравнения формируется сигнал ошибки, который поступает на выход 22 устройства. Этот же сигнал поступает на вход элемента ИЛИ 14 и приводит устройство в исходное состояние. При равенстве длин циклов

0

5

5

сигна: с другого выхода блока / сравнения через элемент МПИ 16 поступает на счетные входы счетчиков 5 и 6 и на элемент 12 задержки, благодаря чему код на адресных шинах блоков 1 и 2 памяти возрастает на единицу, объект 24 контроля и блок 8 сбрасываются в начальное состояние, а импульс, поступающий на вход считывания блока 1 памяти, выбирает очередное входное тестовое число.

С приходом очередного тактового импульса начинается новый цикл работы устройства.

При исправности объекта 24 контроля в процессе работы устройства с выхода элемента ИЛИ 16 на счетный вход счетчика 6 поступает п импульсов; Это вызывает появление импульса переполнения счетчика, который поступает на выход 23 з стройства. Таким образом, появление сигнала на выходе 23 говорит об исправности объекта 24 контроля. Этот же сигнал через элемент ИЛИ 14 приводит все устройство в исходное состояние.

Блок 8 обнаружения цикла работает следующим образом.

Сигнал с выхода элемента ИЛИ 15, приводящий блок в исходное состояние, переводит в нулевое состояние триггер 35, а через элемент ИЛИ 32 в нулевое состояние счетчик 38 циклов и в единичное состояние триггер 34. Кроме того, этот сигнал, проходя через элемент ИЛИ-33, поступает на S-вход счетчика 37 совпадений, устанавливая все его разряды в единичное состояние, т.е. в -счетчике 37 устанавливается код на единицу меньший, чем нулевой, В процессе работы на информационный вход блока обнаружения цикла подаются данные, подлежащие об5 работке, которые поступают на первый информационный вход блока 26 сравнения и информационный вход регистра 25. На тактовый вход блока 8 подаются импульсы синхронизации (по одному на каждое число на информационном входе), которые поступают на первые входы элементов И 28 и 29, вторые входы которьгх соединены с прямым и инверсным выходами триггера 34.

5 Таким образом, в зависимости от состояния триггера 34 тактовые импульсы проходят по разным каналам. При единичном состоянии триггера 34 тактовый импульс через элемент И 29 пос0

5

0

0

тупает на синхровход регистра 25, По этому синхросигналу информация с информационного входа блока 8 записывается в регистр 25 и поступает на второй информационный вход еитока 26 сравнения. Одновременно с этим импульс с выхода элемента И 29 поступает на К-вход триггера 34 и устанавливает его в нулевое состояние, а также ю счетчика 37 совпадений. Разрядность

поступает на вход записи счетчика 36. По этому сигнал через информационный вход счетчика 36 считывается содержимое счетчика 38 цикла. При нулевом состоянии триггера 34 тактовые импульсы через элемент И 28 поступает на счетный вход счетчика 36, уменьшая каждый раз его содержимое на единицу до обнуления. В следующем после обну- .ления такте тактовый импульс прохо- дит через открывшийся элемент И 30 на управляющий вход блока 26 сравнения, разрешая сравнение данных по его первому и второму информационным входам. Таким образом, сравниваются числа, поступающие на вход блока 8 и отстоящие друг от друга на величину записанного числа в счетчике 38 циклов.

С выхода блока 26 сравнения сигнал совпадения попадает на счетный вход счетчика 37 совпадений, увеличивая его значение на единицу, и на единичный вход триггера 34, подготавливая его к приему очередных данных. При обнаружении цикла содержимое счетчика 37 совпадений увеличивается, Пока не достигает значения, зацисан- ного в счетчике 38 циклов, а это означает, что будут проверены все числа

цикла. В этом случае второй блок 27 сравнения, первый вход которого связан с информационным выходом счетчика 38 циклов, а второй вход с информационным выходом счетчика 37 совпадений, вырабатывает сигнал, который при единичном состоянии триггера 35 проходит через элемент И 31 на выход блока 8, сигнализируя об обнаружении цикла. В этот момент с информационно го выхода блока В можно получить информацию, характеризующую цикл. Сигнал же несовпадения с выхода блока 26 сравнения поступает на счетный вход счетчика 38 циклов, увеличивая его значение на единицу, на вход установки нуля счетчика 36 и через элемент ИЛИ 33 на S-вход, устанавливая в единицу все его разряды.

Таким образом, при несовпадениях значение счетчика 38 растет до переполнения, сигнал о котором, пройдя через элемент ИЛИ 32, поступае.т на вход установки нуля счетчика 38 циклов, на единичный вход триггера 34, готовя его к приему новых данных, и через элемент ИЛИ 33 - на S-вход

счетчиков 37 и 38 должна быть не менее (т-1), где га - число элементов памяти обьекта 24 контроля. Это обеспечит обнаружение любого цикла, вплоть

до максимального, длины 2,

Анализируемая последовательность чисел, как правило, имеет некоторый начальный непериодический участок. Это приводит к тому, что у блока 8

имеет место переходной режим, в течение которого он не в состоянии обнаружить цикл. Этот режим длится от момента запуска блока 8 до появления импульса переполнения счетчика 38

циклов. В такте, предществующем импульсу переполнения, значения счетчиков 37 и 38 совпадут и сигнал об этом с выхода блока 27 сравнения переключит триггер 35 в единичное состояние, подготавливая тем самы14 элемент И 31 для пропускания сигнала обнаружения цикла на выход блока 8. Основной режим работы начинается с появления импульса переполнения счетчика 38 циклов, который приводит вычислитель в исходное состояние. В этот момент анализируемая последовательность чисел обязательно находится в пределах циклической части. Основной режим заканчивается сигналом совпадения на выходе блока 27 сравнения, который через открытый элемент И 31 проходит на выход блока 8 обнаружения цикла.

50

45

Формула изобретения

Устройство для контроля цифровых блоков, содержащее первый и второй блоки памяти и блок сравнения., при- ;Чем группа выходов первого блока памяти является группой информационных выходов устройства для подключения к группе информационных входов конт- gi ролируемого блока, группа выходов

второго блока памяти соединена с первой группой информационных вх.одов блока сравнения, выход неравенства которого является выходом ошибки устройства, отличаюп1ееся тем, что, с целью повьшения достоверности контроля, в устройство введены блок обнаружения цикла, ,два счетчика, два триггера, генератор тактовых импульсов, два элемента задержки, три элемента ИЛИ и три элемента И, цри- чем группа информационных входов бло15

20

30

ка обнаружения цикла является группой ю памяти, вход записи которого соединен информационных входов устройства для подключения к группе выходов контролируемого блока, вход пуска устройства соединен с S-входом первого триггера, выход которого соединен с первым входом первого элемента И, выход которого соединен с входом синхронизации блока обнаружения цикла и является выходом устройства для подключения к синхровходу контролируемого блока, вход начальной установки устройства соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом неравенства блока сравнения, выход равенства 25 которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с счетными входами первого и второго счетчиков и входом первого элемента задержки, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соедин ен с входом чтения первого блока памяти, с входом начальной установки блока обнаружения цикла и является выходом устройства для подключения к входу начальной установки контролируемого блока, адресный вход второго блока памяти объединен с адресньм входом первого блока памяти и подключен к выходу второго счетчика, вход обнуления которого соединен с нулевым входом первого триггера, с установочными входом первого счетчика, вторым входом третьего элемента ИЛИ, и выходом первого элемента ИЛИ, третий вход которого соединен с выходом переполнения первого счетчика и является выходом исправности устройства, входы режимов настройки и работы которого соединены с нулевым и единичным входами второго триггера соответственно, прямой и инверсный выходы которого соединены с первыми входами соответственно второго и третьего элементов И, вторые входы которых объединены и подключены к выходу обнаружения цикла блока обнаружения цикла, группа информационных выходов

с вторым входом второго элемента ИЛИ и выходом второго элемента И, выход генератора тактовых импульсов соединен с вторым входом первого элемента И, причем блок обнаружения цикла содержит регистр, две схемы сравнения, четьфе элемента И, два элемента ИЛИ, два триггера и три счетчика, причем в блоке обнаружения цикла информационный вход регистра объединен с первым информационным входом первой схемы сравнения и является информационным входом блока обнаружения цикла, вход синхронизации которого соединен с входами синхронизации первого и второго триггеров блока обнаружения цикла и с первыми входами первого и второго элемента И блока обнаружения цикла, вторые входы которых соединены соответственно с прямым и инверсным выходами первого триггера блока обнаружения цикла, вход J которого соединен с счетным входом первого счетчика и выходом равенства первой схемы 3g сравнения, выход неравенства которой

соединен с входом установки в О - второго счетчика, с счетным входом третьего счетчика и первым входом первого элемента ИЛИ блока обнаружения цикла, выход первого элемента ИЛИ соединен с входом установки в единичное состояние всех разрядов первого счетчика, группа разрядных выходов которого соединена с первой группой входов второй схемы сравнения, вторая группа входов которой соединена с группой информационных входов второго счетчика, с группой разрядных выходов третьего счетчика и является информационным выходом блока, вход начальной установки блока соединен с нулевым входом второго триггера и с первым входом второго элемента ИЛИ блока обнаружения цикла, второй вход второго элемента ИЛИ соединен с выходом переполнения третьего счетчика, вход установки в О, которого соединен с выходом второго элемента ИЛИ, с вторым входом первого элемента ИЯИ

40

45

БО

55

9567

которого соединена с группой информационных входов второго блока памяти и второй группой информационных входов блока сравнения, вход разрешения сравнения которого соединен с вькодом второго элемента задержки, вход которого соединен с выходом третьего элемента И и входом чтения второго блока

5

0

0

памяти, вход записи которого соединен 5

с вторым входом второго элемента ИЛИ и выходом второго элемента И, выход генератора тактовых импульсов соединен с вторым входом первого элемента И, причем блок обнаружения цикла содержит регистр, две схемы сравнения, четьфе элемента И, два элемента ИЛИ, два триггера и три счетчика, причем в блоке обнаружения цикла информационный вход регистра объединен с первым информационным входом первой схемы сравнения и является информационным входом блока обнаружения цикла, вход синхронизации которого соединен с входами синхронизации первого и второго триггеров блока обнаружения цикла и с первыми входами первого и второго элемента И блока обнаружения цикла, вторые входы которых соединены соответственно с прямым и инверсным выходами первого триггера блока обнаружения цикла, вход J которого соединен с счетным входом первого счетчика и выходом равенства первой схемы g сравнения, выход неравенства которой

соединен с входом установки в О - второго счетчика, с счетным входом третьего счетчика и первым входом первого элемента ИЛИ блока обнаружения цикла, выход первого элемента ИЛИ соединен с входом установки в единичное состояние всех разрядов первого счетчика, группа разрядных выходов которого соединена с первой группой входов второй схемы сравнения, вторая группа входов которой соединена с группой информационных входов второго счетчика, с группой разрядных выходов третьего счетчика и является информационным выходом блока, вход начальной установки блока соединен с нулевым входом второго триггера и с первым входом второго элемента ИЛИ блока обнаружения цикла, второй вход второго элемента ИЛИ соединен с выходом переполнения третьего счетчика, вход установки в О, которого соединен с выходом второго элемента ИЛИ, с вторым входом первого элемента ИЯИ

0

5

О

5

1 3

и с единичным входом iicpiiot o тригте .- ра блока, обнаружения цикла, К-нход которого соединен с входом записи второго счетчика, с тзыходом первого элемента И и с входом синхронизации регистра, группа выходов которого соединена с второй г|)уппой информационных входов первой схемы сравнения, вход разрешения сравнения которой соединен с выходом третьего элемента И блока обнаружения цикла, группа .входом третьего элемента И соединена с

9567

г руппой инверсных выходов второго счетчика, вход управления счетом которого соединен с входом третьего элемента И и выходом второго элемента

)

И, ВЫХОД равенства второй схемы сравнения соединен с первым входом четвертого элемента И и с единичным входом второго триггера блока обнаружения цикла,выход второго триггера соедй.- нен с вторым входом четвертого элемента И,выход которого является выходом обнаружения цикла блока обнаружения цикла.

OmSAZ

Jm эл. 9

От т 15

К ЭЛ.7

«5л70,П

Редактор Е.Папп

Фи&.2

Составитель И.Иваныкин Техред М.Дндьк

Заказ 4223/39 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Л{-35, Раушская наб., д. 4/5

-Производственно-полиграфическое предприятие, г. Ужгород, уд. Проектная, 4

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Устройство для охранной сигнализации | 1990 |

|

SU1783561A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1589280A2 |

| Устройство для обнаружения ошибок в блоках памяти программ | 1988 |

|

SU1709395A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1354196A2 |

| Устройство для группового поиска кратных дефектов в комбинационных логических блоках | 1980 |

|

SU896628A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК | 1990 |

|

RU2019034C1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств автономного и встроенного контроля цифровых узлов. Цель изобретения - повы1В шение достоверности контроля. Устройство содержит блоки 1, 2 памяти, триггеры 3,4, счетчики 5,6, блок 7 сравнения, блок 8 обнаружения цикла, элементы ИЛИ 14-16, генератор 17 тактовых импульсов, входы 18,19 режимов, вход 20 пуска, вход 21 начальной установки, выход 22 ошибки и выход 23 исправности. Устройство позволяет определять длину характерных для объекта контроля циклов и сравнивать ее с эталонной. Цовьшение достоверности контроля достигается за счет вычисления характерного контрольного элемента для конкретного объекта контроля и введения в устройство блока 8 обнаружения цикла и логических элементов, обеспечивающих его функционирование. 2 И.П. 1C С/) с: 22 23 О5 ОО СО ел GD ы

| Казьмина С,К.Компактное тестирование, - Автоматика и телемеханика, 1982, № 3,-с.173-189 | |||

| Устройство для контроля на цикличность | 1977 |

|

SU658562A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1985-12-03—Подача