сг

о со со

00 00

Изобретение относится к вычислительной технике и может быть использовано при наладке и ремонте цифровых вычислительных машин, в частности дпя поиска перемежающихся неисправностей.

Целью изобретения является повышение полноты контроля.

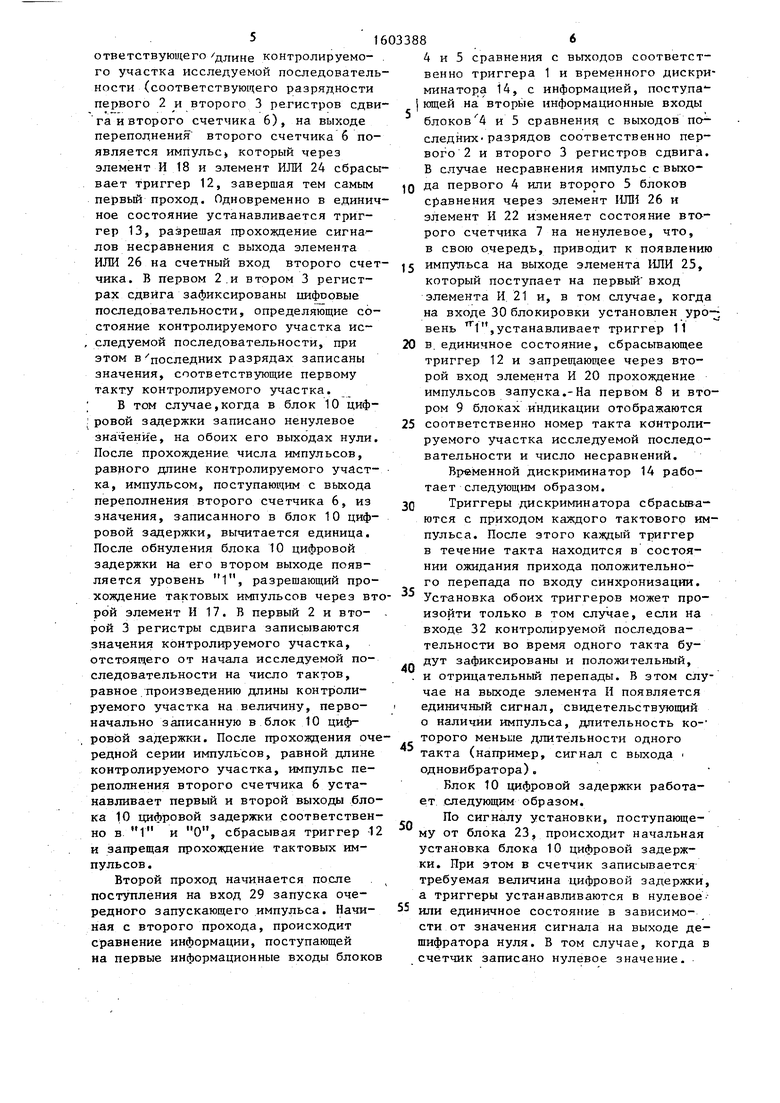

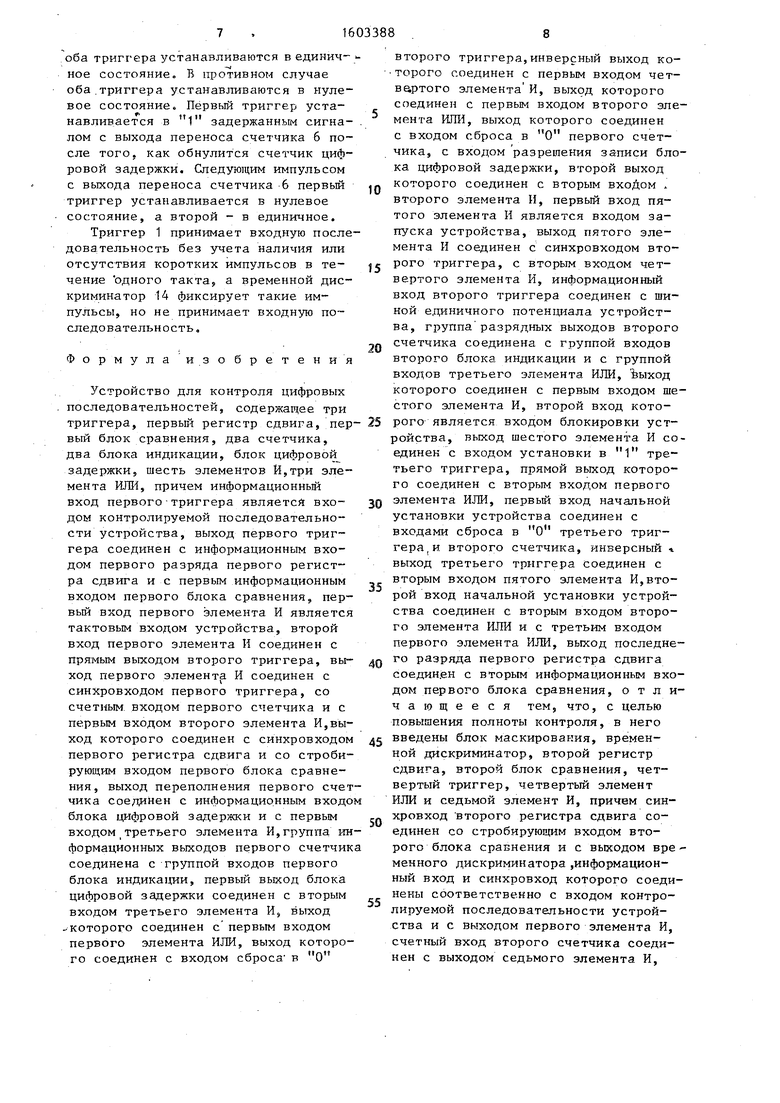

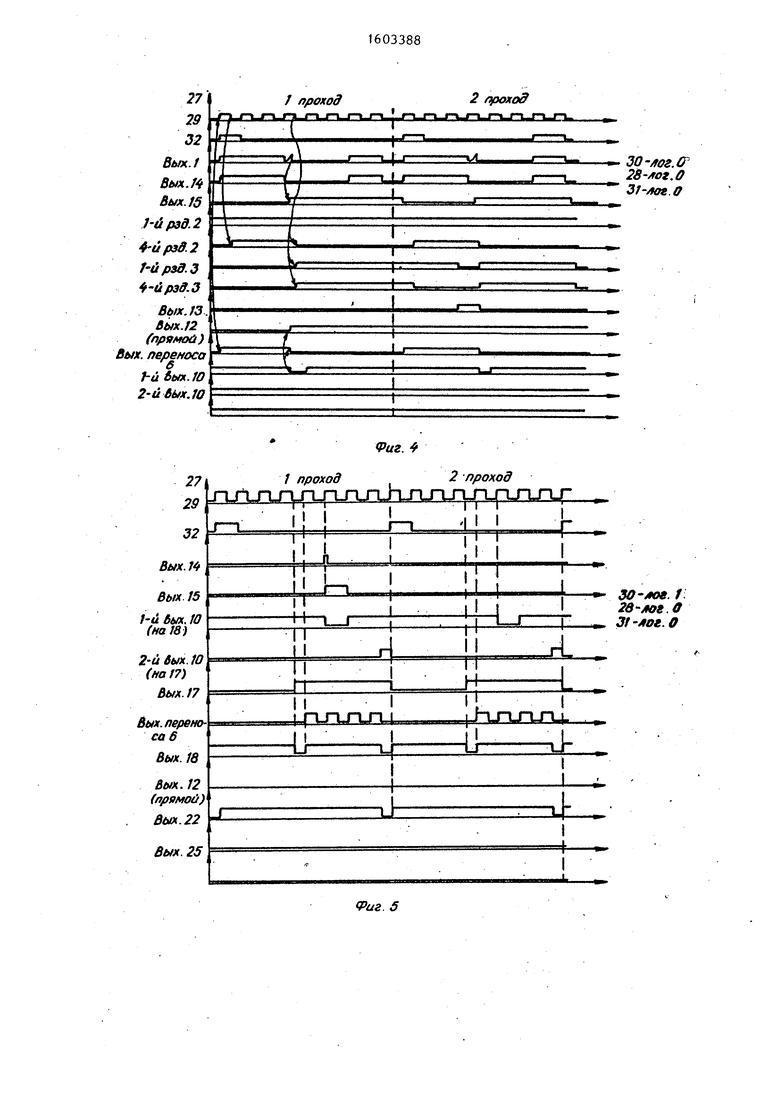

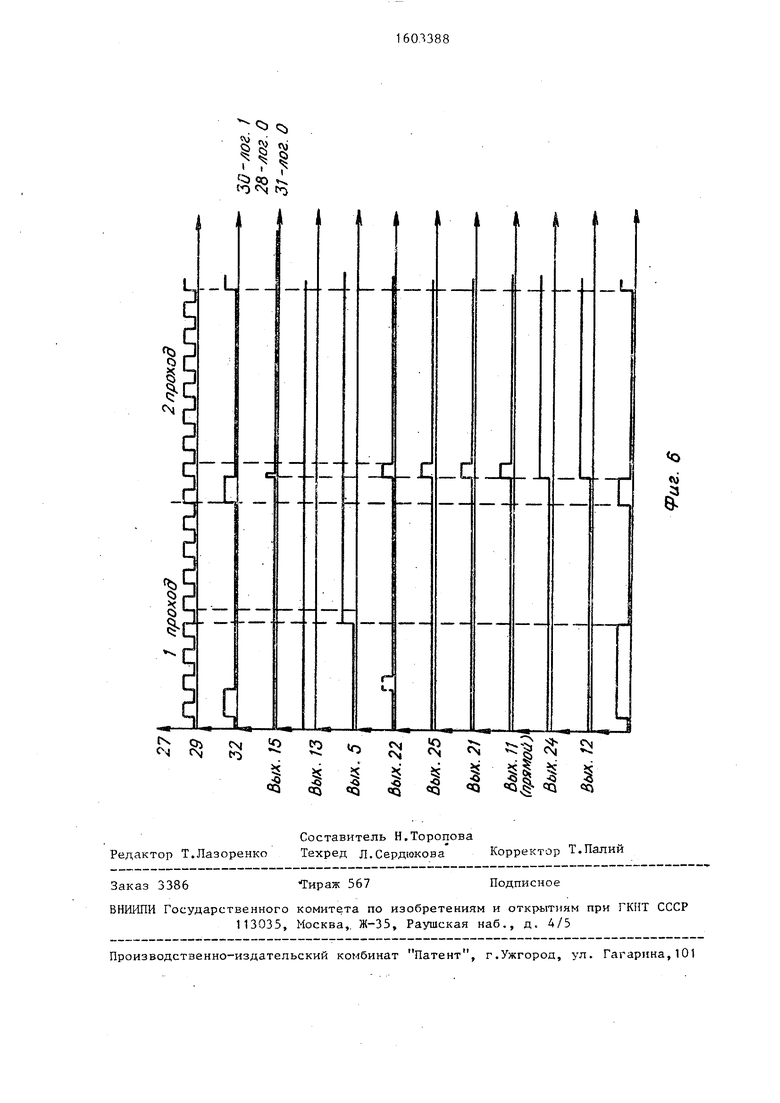

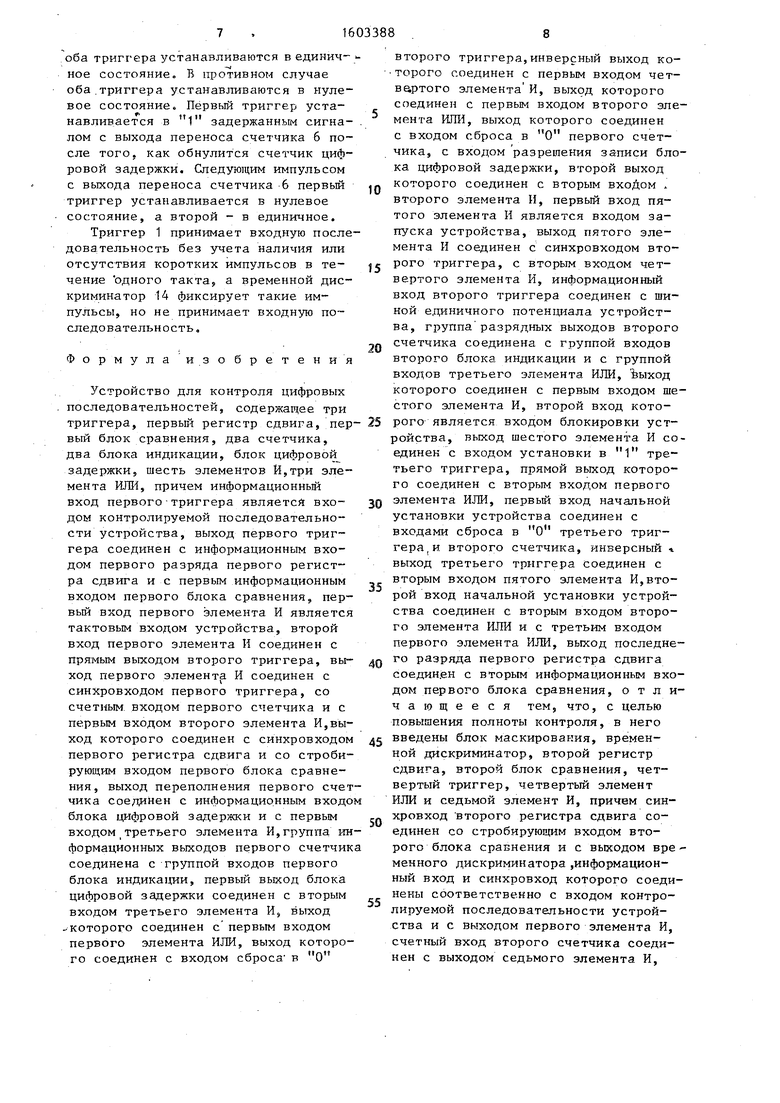

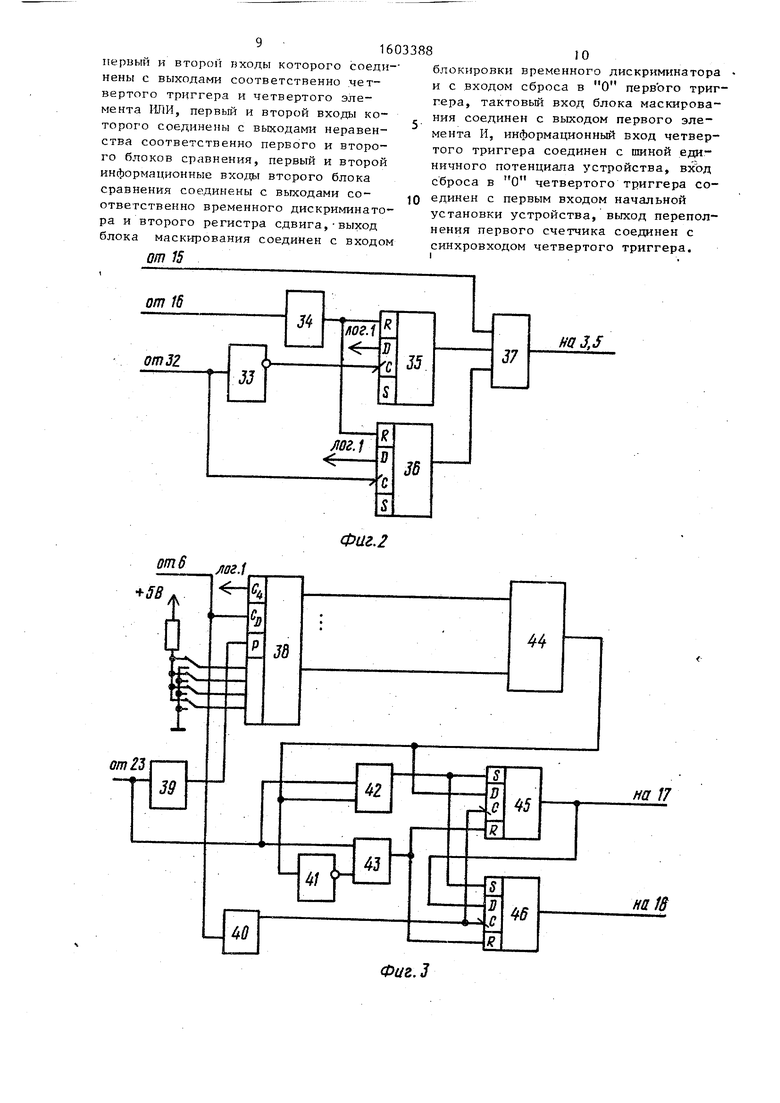

На фиг.1 представлена структурная схема устройства; на фиг.2 - схема временного дискриминатора; на фиг.З - схема блока цифровой задержки; на фиг.4 - диаграмма работы при нулевой цифровой задержке;на фиг.З - то же, при цифровой задержке, равной единице; на фиг.6 - то же, при единичном сигнале на входе блокировки и нулевой цифровой задержке. Длина контролируемой цифровой последователности 8 тактов, длина контролируемого за один проход участка 4 такта.

Устройство содержит триггер 1, регистры 2 и 3 сдвига, блоки 4 и 5 сранения, счетчики 6 и 7, блоки 8 и 9 индикации, блок 10 цифровой задержки триггеры 11-13, временной дискримина тор 14, блок 15 маскирования, элементы И 16-22, элементы ИЛИ 23-26 тактовый вход 27, первый вход 28 начальной установки, вход 29 запуска, вход 30 блокировки, второй вход 31 начальной установки и вход 32 контролируемой последовательности..

Временной дискриминатор 14 содержит элемент ШШ-НЕ 33, формирователь 34 короткого импульса, триггеры 35 и 36 элемент И 37.

Блок 10 цифровой задержки содержи счетчик 38, элемент ИЛИ 39, элемент 40 задержки, элемент НЕ 41, элемент И 42 и 43, дешифратор 44, триггеры 45 и 46.

Устройство работает следующим образом.

Перед началом работы устанавливаются в исходное состояние первый 6 и второй 7 счетчики, триггеры 11-13, в блок 10 цифровой задержки записывается требуемая величина задержки, в блок 15 маскирования - маскирующая последовательность, в которой, каждому такту контролируемой периодической импульсной последовательности соответствуют О или 1 в зависимости от того, определено ипи не определено на соответствующем такте значение сигнала. На вход 32 контролируемой последовательно0

0

5

сти поступает исследуем ая цифровая последовательность, на тактовьш вход 27 поступают тактовые импульсы (например, от внутреннего генератора контролируемого блока), но на выход первого элемента И 16 они не проходят, поскольку на втором входе первого элемента И 16 - уровень О с прямого входа триггера 12. С приходом импульса запускаJ однозначно связанного с началом контролируемого участка исследуемой цифровой последовательности, на выходе элемента 5 И 20 появляется импульс, который устанавливает триггер 12 в единичное состояние, разрешая тем самым подачу тактовых импульсов на синхровходь; блока 15 маскирования, триггера 1, временного дискриминатора 14 и счетный вход первого счетчика 6, а также на первьй вход элемента И 17.

В том случае, когда в блок 10 цифровой задержки записан ноль, на его обоих выходах - уровни 1, разрешающие прохождение сигналов через элементы И 17 и 18. Тактовые импульсы с выхода элемента И 17 поступают на входы синхронизации первого 2 и второго 3 регистров сдвига, входы блоков 5 и 4 сравнения. В регистры 2 и 3 сдвига последовательно записываются состояния выходов триггера 1 и временного дискриминатора 14. Первьй 4 и второй 5 блоки сравнения сравнивают состояния выходов последних разрядов соответственно первого и второго регистров 2 и 3 сдвига с выходами соответственно триггера 1 и временного дискриминатора 14, однако результат несравнения на первом проходе не фиксируется на втором счетчике 7, поскольку элемент И 22 закрыт по второму входу уровнем 1 с выхода триггера 13. В тех тактах исследуемой цифровой последовательности, когда сигналы могут принимать различные значения, единичный уровень, поступающий с выхода блока 15 маскирования на установочные входы триггера 1 ввода и временного дискриминатора 14, устанавливает их в определенные (нулевые) состояния, в результате чего на первом 2 и втором 3 регистрах сдвига в случае нормальной работы контролируемого блока формируется стабильная цифровая последовательность. После прохояоде- ния числа тактовых импульсов, со0

5

0

5

0

5

10

20

51603388

ответствующего /длине контролируемо- . го участка исследуемой последовательности (соответствующего разрядности первого 2 и второго 3 регистров сдвига и второго счетчика 6), на выходе переполнения второго счетчика б появляется импульс который через элемент И 18 и элемент ИЛИ 24 сбрасывает триггер 12, завершая тем самым первый проход. Одновременно в единичное состояние устанавливается триггер 13, разрешая прохождение сигналов несравнения с выхода элемента ИЛИ 26 на счетный вход второго счетчика. В первом 2.и втором 3 регистрах сдвига зафиксированы цифиовые последовательности, определяющие состояние контролируемого участка ис- следуемой последовательности, при этом в последних разрядах записаны значения, соответствующие первому такту контролируемого участка. В том случае,когда в блок 10 циф- ровой задержки записано ненулевое значени е, на обоих его выходах нули. После прохождение числа импульсов, paBjioro длине контролируемого участка, импульсом, поступающим с выхода переполнения второго счетчика 6, из значения, записанного в блок 10 цифровой задержки, вычитается единица. После обнуления блока 10 цифровой задержки на его втором выходе появляется уровень 1, разрешающий прохождение тактовых импульсов через второй элемент И 17. В первый 2 и вто- - ой 3 регистры сдвига записываются значения контролируемого участка, тстоящего от начала исследуемой последовательности на число тактов, авное произведению длины контролиуемого участка на величину, первоачально записанную в блок 10 цифовой задержки. После прохождения очередной серии импульсов, равной длине контролируемого участка, импульс переполнения второго счетчика 6 устанавливает первый и второй выходы блока 10 цифровой задержки соответствен25

30

35

40

но в 1 и о, сбрасывая триггер 12 и запрещая прохождение тактовых имульсов .

Второй проход начинается после поступления на вход 29 запуска очередного запускающего импульса. Начиная с второго прохода, происходит сравнение информации, поступающей на первые информационные входы блоков

5 и

е о т т од

е

м у ки тр а ил ст щи сч

45

50

55

10

20

388

5

0

5

0

6

4 и 5 сравнения с выходов соответственно триггера 1 и временного дискриминатора 14, с информацией, поступа - ющей на вторые информационные входы блоков 4 и 5 сравнения с выходов последних- разрядов соответственно первого 2 и второго 3 регистров сдвига. В случае несравнения импульс с выхода первого 4 или второго 5 блоков сравнения через элемент lUBi 26 и элемент И 22 изменяет состояние второго счетчика 7 на ненулевое, что, в свою очередь, приводит к появлению 5 импульса на выходе элемента ИЛИ 25, который поступает на первьм вход элемента И 21 и, в том случае, когда на входе 30 блокировки установлен уро вень 1,устанавливает триггер 11 в. единичное состояние, сбрасывающее триггер 12 и запрещающее через второй вход элемента И 20 прохождение импульсов запуска.-На первом 8 и втором 9 блоках индикации отображаются соответственно номер такта контролируемого участка исследуемой последовательности и число несравнений.

Временной дискриминатор 14 работает следующим образом.

Триггеры дискриминатора сбрасываются с приходом каждого тактового импульса. После этого каждый триггер в течение такта находится в состоянии ожидания прихода положительного перепада по входу синхронизации. Установка обоих триггеров может произойти только в том случае, если на входе 32 контролируемой последовательности во время одного такта будут зафиксированы и положительный, и отрицательный перепады. В этом случае на выходе элемента И появляется единичный сигнал, свидетельствующий о наличии импульса, длительность ко- торого меньше длительности одного такта (например, сигнал с выхода одновибратора),

Блок 10 цифровой задержки работает следующим образом.

По сигналу установки, поступающему от блока 23, происходит начальная установка блока 10 цифровой задержки. При этом в счетчик записывается требуемая величина цифровой задержки, а триггеры устанавливаются в нулевое .- или единичное состояние в зависимости от значения сигнала на выходе де- щифратора нуля. В том случае, когда в счетчик записано нулевое значение.

5

0

5

оба триггера устанавливаются в единим- - ное состояние. В противном случае оба.триггера устанавливаются в нулевое состояние« Первый триггер устанавливается в 1 задержанным сигна- . лом с выхода переноса счетчика 6 после того, как обнулится счетчик цифровой задержки. Следующим импульсом с выхода переноса счетчика 6 первый Q триггер устанавливается в нулевое состояние, а второй - в единичное.

Триггер 1 принимает входную последовательность без учета наличия или

отсутствия коротких импульсов в те- J5

чение одного такта, а временной дискриминатор 14 фиксирует такие импульсы, но не принимает входную последовательность.

20

Формула изобретения

Устройство для контроля цифровых последовательностей, содержащее три триггера, первый регистр сдвига, пер- 25 вый блок сравнения, два счетчика, два блока индикации, блок цифровой задержки, шесть элементов И,три элемента ИЛИ, причем информационньй вход первоготриггера является вхо- ЗО дом контролируемой последовательности устройства, выход первого триггера соединен с информационным входом первого разряда первого регистра сдвига и с первым информационным ,, входом первого блока сравнения, первый вход первого элемента И является тактовым входом устройства, второй вход первого элемента Н соединен с прямым выходом второго триггера, вы- Q ход первого элемента И соединен с синхровходом первого триггера, со счетным входом первого счетчика и с первым входом второго элемента И,выход которого соединен с синхровходом 45 первого регистра сдвига и со строби- рующим входом первого блока сравнения, выход переполнения первого счетчика соединен с информационным входом блока цифровой задержки и с первым -л входом третьего элемента И,группа информационных выходов первого счетчика соединена с группой входов первого блока индикации, первый выход блока цифровой задержки соединен с вторым входом третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса в О

второго триггера,инверсный выход ко- торого соединен с первым входом чет- вартого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом сброса в О первого счетчика, с входом разрешения записи блока цифровой задержки, второй выход которого соединен с вторым входом . второго элемента И, первый вход пятого элемента И является входом запуска устройства, выход пятого элемента И соединен с синхровходом второго триггера, с вторым входом четвертого элемента И, информационный вход второго триггера соединен с шиной единичного пoтeнIJДiaлa устройства, группа разрядных выходов второго счетчика соединена с группой входов второго блока индикации и с группой входов третьего элемента ИЛИ, Ъыход которого соединен с первым входом шестого элемента И, второй вход которого является входом блокировки устройства, выход шестого элемента И соединен с входом установки в 1 третьего триггера, прямой выход которого соединен с вторым входом первого элемента ИЛИ, первьй вход начальной установки устройства соединен с входами сброса в О третьего триггера, и второго счетчика, инверсный выход третьего триггера соединен с вторым входом пятого элемента И,второй вход начальной установки устройства соединен с вторым входом второго элемента ИЛИ и с третьим входом первого элемента ИЛИ, выход последнего разряда первого регистра сдвига соедин.ен с вторым информационным входом первого блока сравнения, о т л и чагощееся тем, что, с целью повышения полноты контроля, в него введены блок маскирования, временной дискриминатор, второй регистр сдвига, второй блок сравнения, четвертый триггер, четвертый элемент ИЛИ и седьмой элемент И, причем син- хровход второго регистра сдвига соединен со стробирующим входом второго блока сравнения и с выходом временного дискриминатора ,информацион- ный вход и синхровход которого соединены соответственно с входом контролируемой последовательности устройства и с выходом первого элемента И, счетный вход второго счетчика соединен с выходом седьмого элемента И,

первый и второй входы которого соединены с выходами соответственно четвертого триггера и четвертого элемента ИГШ, первый и второй входы которого соединены с выходами неравенства соответственно первого и второго блоков сравнения, первый и второй информационные входы второго блока сравнения соединены с выходами соответственно временного дискриминатора и второго регистра сдвига,выход блока маскирования соединен с входом

от 15

10

блокировки временного дискриминатора и с входом сброса в О первого триггера, тактовый вход блока маскирования соединен с выходом первого элемента И, информационный вход четвертого триггера соединен с шиной единичного потенциала устройства, вхЪд сброса в О четвертого триггера соединен с первым входом начальной установки устройства, выход переполнения первого счетчика соединен с синхровходом четвертого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля цифровых последовательностей | 1987 |

|

SU1418718A1 |

| Устройство для обработки реакции логических блоков | 1990 |

|

SU1725221A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1411750A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля цифровых систем | 1983 |

|

SU1130871A1 |

| Двухканальное устройство для сопряжения ЭВМ | 1989 |

|

SU1735860A1 |

Изобретение относится к вычислительной технике и может быть использовано при наладке и ремонте цифровых вычислительных машин. Отличительной особенностью устройства является то, что оно позволяет контролировать последовательности, сигналы в которых могут быть представлены в виде коротких импульсов, а состояние которых в отдельных тактах контролируемого участка исследуемой последовательности может быть неопределенным. Целью изобретения является повышение полноты контроля. Поставленная цель достигается за счет введения временного дискриминатора 14, триггера 13, регистра 3 сдвига, блока 5 сравнения, элемента ИЛИ 26, элемента И 22. 6 ил.

Фиг.2

Фиг.З

Риг. 5

Составитель Н.Торопова Редактор Т.Лазоренко Техред Л.Сердюкова Корректор Т.Палий

Заказ 3386

Тираж 567

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКИТ СССР 113035, Москва,. Ж-35, Раушская наб., д. 4/5

-I да Д1 ияг м-г .-г ми ч-т-1I---.---.-.-.-- - .-. - - --. - -- «-«-- - «

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Подписное

| Устройство для поиска перемежающихся неисправностей | 1979 |

|

SU920732A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-30—Публикация

1988-10-24—Подача